If there are no takers for this empty board then if you can provide assembled and tested one to Mark that would be great. I will cover your costs as indicated before🙂

Looks like Marcel’s DAC implements RTZ in the hardware logic itself whereas Andrea’s one uses a separate FPGA fifo module for this function and then feeds the DAC module. Extra costs, complexity and noise. Clocking in the former is also more straightforward with flexible options

Thanks, but I have read that already before posting earlier. DAC manual indicates it can operate without this external fifo but RTZ function not possible unless this fifo-lt is used. Costs going well above USD1k for diy use

There is a simple board to bypass the FIFO. You can generate RTZ however you like and feed it in there. Or you can skip that board too. What's needed is pretty simple, there is a bit clock and + and - data phases for each channel. RTZ or non-RTZ is implemented with those five signals. If you want SE instead of balanced, then its only three signals.

Other than that, as I have tried to point out repeatedly, this stuff is not low cost!

IMHO, Iancanada and or Twisted Pear weren't/aren't particularly low cost either by the time you get done buying stuff. As others have already pointed out in various places, if you want to save money buy a Topping, Behringer, etc.

Other than that, as I have tried to point out repeatedly, this stuff is not low cost!

IMHO, Iancanada and or Twisted Pear weren't/aren't particularly low cost either by the time you get done buying stuff. As others have already pointed out in various places, if you want to save money buy a Topping, Behringer, etc.

Last edited:

Not trying to disadvantage cost wise but if performance is really that good then can be considered at another level. I am not sure how to generate RTZ by other means, any idea? I am not in favour of fifo for something synchronous - reclocking is fine.

Another interesting insight indicated earlier: commercial products of this type have got some 6-8 times markup. So assuming a build of Andrea’s or Marcel’s is about $2k then it will be well within striking distance of similar commercial ones. Have you compared with Holo May L3 (~$6k)?

Another interesting insight indicated earlier: commercial products of this type have got some 6-8 times markup. So assuming a build of Andrea’s or Marcel’s is about $2k then it will be well within striking distance of similar commercial ones. Have you compared with Holo May L3 (~$6k)?

Hi acko, I will try to take the concerns one at a time....if performance is really that good then can be considered at another level.

Andrea is very focused on performance in all aspects of design. The FIFO is to accommodate any type of I2S input including from a SPDIF receiver. The alternative is PLL or ASRC. FIFO is the only bit-perfect, ultra-low jitter option that works in the general case. Asynchronous USB is a special case that doesn't require a dac FIFO, but it can still work with such a FIFO anyway (actually there is already a short FIFO in the XMOS algorithm). My own preference would be for a simplified option for those people only wanting to use USB sources.

Yes, but don't want to take up space explaining here in this thread. Besides, Marcel explained the rational for RTZ before. Once understood it becomes pretty clear what the waveforms have to look like. At that point its just a question of implementing the necessary digital logic.I am not sure how to generate RTZ by other means, any idea?

This has already been thought of. IIUC Andrea is at the Munich audio show right now. I believe that's one of the things he is interested in looking at.Have you compared with Holo May L3 (~$6k)?

In addition to the questions you raise, there are other things that are important to high performance dac design. Andrea has done a more thorough job at covering all the bases than is seen in most other designs. That is not to say he has achieved perfection, nor is to criticize other designers. It is just that Andrea is a no-compromise kind of guy. He wants to do everything the best he knows how, regardless of cost. Most people aren't exactly motivated by the same internal drive. Many designers may be more cost conscious, or have other goals as a part of what motivates them. I can't speak for Marcel, but I wouldn't be surprised if he were to say the dac he designed for this thread was, among other goals, meant to be diy'er friendly and of reasonable cost to build. If so, that wouldn't be a bad thing. It would mean more people could build it and enjoy it.

Last edited:

I've been following both Andrea's and Marcel's RTZ implementations as best I can, but I have kind of a newbie question 🙂

I have the need for an 8 channel, phase accurate & high quality DSD implementation. DSD256 is plenty for my needs. Would something like the MiniDSP MCHStreamer (https://www.minidsp.com/products/usb-audio-interface/mchstreamer) and four of Marcel's RTZ boards do the trick?

The MCHStreamer is specified to output 8 channels of DSD256. I would be pre-converting PCM to DSD, before streaming the 8 channels out of the computer via USB. In a nutshell, I'm wondering if the DSD streams are phase accurate (relative to one another & regardless if generated by the above MCHStreamer or something else), would 4 of the RTZ DSD boards work ok together?

I'm thinking I might need a single clock distributed to the 4 boards, but not 100% sure about that.

Edit: including filter boards/power supplies of course, I'm just focusing on the core DACs 🙂

I have the need for an 8 channel, phase accurate & high quality DSD implementation. DSD256 is plenty for my needs. Would something like the MiniDSP MCHStreamer (https://www.minidsp.com/products/usb-audio-interface/mchstreamer) and four of Marcel's RTZ boards do the trick?

The MCHStreamer is specified to output 8 channels of DSD256. I would be pre-converting PCM to DSD, before streaming the 8 channels out of the computer via USB. In a nutshell, I'm wondering if the DSD streams are phase accurate (relative to one another & regardless if generated by the above MCHStreamer or something else), would 4 of the RTZ DSD boards work ok together?

I'm thinking I might need a single clock distributed to the 4 boards, but not 100% sure about that.

Edit: including filter boards/power supplies of course, I'm just focusing on the core DACs 🙂

Last edited:

Regarding MCHStreamer, I didn't see anything in a quick look at the manual about support for external clocks. If external clocks are not supported then I would not consider using it unless maybe if all of its I2S outputs were passed through a multichannel FIFO buffer then reclocked using a very good set clock set. IIUC low jitter clocks be be more important for DSD since the amplitude step sizes are full scale on/off (whereas for PCM amplitude step sizes are smaller, so for PCM a timing error may result in less total integrated error per sample). FIRDAC for DSD may help with that, but still it may be something to consider.

Yes, understood. Thanks for the detailed explanation. Can see the logic for separating RTZ logic from DAC core. Marcel has also separated this on board. So this FIFO-lite seems to refer to depth of buffering and will be fine for spdif without introducing too much delays if someone were to hook up to Video system also.…. The FIFO is to accommodate any type of I2S input including from a SPDIF receiver. The alternative is PLL or ASRC. FIFO is the only bit-perfect, ultra-low jitter option that works in the general case. Asynchronous USB is a special case that doesn't require a dac FIFO, but it can still work with such a FIFO anyway (actually there is already a short FIFO in the XMOS algorithm). My own preference would be for a simplified option for those people only wanting to use USB sources.

Yes, but don't want to take up space explaining here in this thread. Besides, Marcel explained the rational for RTZ before. Once understood it becomes pretty clear what the waveforms have to look like. At that point it’s just a question of implementing the necessary digital logic.

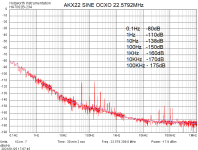

The next concern is clocking. I have got clocks that are higher performance than others (I think?). Shown attached. Both sine and hcmos types are about the same in terms of phase noise performance. All in a compact module. I can use this to drive my own DACs directly and can be used with Marcel’s also without the need for converters. Andrea’s one is lower performance sine type to start with and then after conversion on his fifo board is even worse. As you mentioned, it very important for DSD clocking with low jitter clocks. So, how can I bypass the on-board clock circuit and feed a better one. I do remember Andrea mentioning about his sonic empire clocks that address the loss of quality, any news on this?

Attachments

There is a board to bypass the FIFO completely. It converts DSD over I2S bus into the signals needed to run the dac board. If you want to use your own master clocks and not use the FIFO board then you probably have to design your own RTZ circuitry or copy something like Marcel's 🙂 Once you have the RTZ data signals, a way to select clock families, and a master clock divider for DSD sample rates below DSS256, then you can reclock the prepared I2S bus signals using your master clock. Of course, you may want to have phase noise measurement gear on hand to test performance and make sure its up to your specifications.

Also, you would probably also want to send copies of your master clocks to your USB board so that it operates synchronously with your other clock circuitry.

Basically, you would have to do the same thing with Marcel's dac since his digital circuitry is probably not going to preserve the phase noise of your clocks. You would have to reclock all signals before they go to the shift registers. Then the shift registers will probably degrade the phase noise.

My guess would be that the UHS logic family reclocking D-flip flops that drive the resistors on Andrea's dac board will probably preserve your phase noise better than shift registers.

Also, you would probably also want to send copies of your master clocks to your USB board so that it operates synchronously with your other clock circuitry.

Basically, you would have to do the same thing with Marcel's dac since his digital circuitry is probably not going to preserve the phase noise of your clocks. You would have to reclock all signals before they go to the shift registers. Then the shift registers will probably degrade the phase noise.

My guess would be that the UHS logic family reclocking D-flip flops that drive the resistors on Andrea's dac board will probably preserve your phase noise better than shift registers.

Last edited:

Just a quick note. Iancanada has a FIFO buffer that handles 8 channels of DSD512 (plus an additional 7 channels of i2s) and allows use of an external clock: https://www.audiophonics.fr/en/diy-...multi-channel-i2sdsd-fifo-buffer-p-17125.html

Manual: https://raw.githubusercontent.com/iancanada/DocumentDownload/master/McFIFO series/McFIFO/McFIFOManual.pdf

Manual: https://raw.githubusercontent.com/iancanada/DocumentDownload/master/McFIFO series/McFIFO/McFIFOManual.pdf

I may have an old McFIFO buffer around here somewhere. It was one of the things I tried. Also got the McClock or whatever it was called, the master clock board that goes with it. Didn't sound good me. IMHO the clocking wasn't clean.

Did sound a little better when I put it in a steel shielding case. Maybe it was affected by environmental EMI/RFI to some extent. Didn't seem like that was the only problem though. IIRC the clock board had cutouts to add optional voltage regulators for the clocks (at added cost of course).

Bottom for me, If I were going to use that FIFO I would design my own master clock board and reclock every signal after it left the FIFO.

Again if it were me and if using MCHStreamer I might consider hacking it and feeding it my own clocks. Then I would just reclock the I2S output signals and skip the FIFO.

Did sound a little better when I put it in a steel shielding case. Maybe it was affected by environmental EMI/RFI to some extent. Didn't seem like that was the only problem though. IIRC the clock board had cutouts to add optional voltage regulators for the clocks (at added cost of course).

Bottom for me, If I were going to use that FIFO I would design my own master clock board and reclock every signal after it left the FIFO.

Again if it were me and if using MCHStreamer I might consider hacking it and feeding it my own clocks. Then I would just reclock the I2S output signals and skip the FIFO.

Last edited:

I was thinking the same (eg hacking in an external clock input). It does have an output, but I'm guessing it isn't the greatest - the whole unit is <$120, haha!

If I am not mistaken The MCHStreamer looks like a low cost unit with PLL synthesized timing from a single clock. No point hacking into it with like an ocxo. FIFO is needed to retime with audio clocks if aiming for something better.

Actually, the point I was making: the sine-to-square circuit on fifo-lite board look similar to his stand alone module - degrades the incoming clock quality to start with. Unless improvements has been made on his fifo version.There is a board to bypass the FIFO completely. It converts DSD over I2S bus into the signals needed to run the dac board. If you want to use your own master clocks and not use the FIFO board then you probably have to design your own RTZ circuitry or copy something like Marcel's 🙂 Once you have the RTZ data signals, a way to select clock families, and a master clock divider for DSD sample rates below DSS256, then you can reclock the prepared I2S bus signals using your master clock. Of course, you may want to have phase noise measurement gear on hand to test performance and make sure its up to your specifications.

Also, you would probably also want to send copies of your master clocks to your USB board so that it operates synchronously with your other clock circuitry.

Basically, you would have to do the same thing with Marcel's dac since his digital circuitry is probably not going to preserve the phase noise of your clocks. You would have to reclock all signals before they go to the shift registers. Then the shift registers will probably degrade the phase noise.

My guess would be that the UHS logic family reclocking D-flip flops that drive the resistors on Andrea's dac board will probably preserve your phase noise better than shift registers.

Understood with clock distribution to various circuits there could be some effects also that will require attention later.

Hi acko, I will try to take the concerns one at a time.

Andrea is very focused on performance in all aspects of design. The FIFO is to accommodate any type of I2S input including from a SPDIF receiver. The alternative is PLL or ASRC. FIFO is the only bit-perfect, ultra-low jitter option that works in the general case. Asynchronous USB is a special case that doesn't require a dac FIFO, but it can still work with such a FIFO anyway (actually there is already a short FIFO in the XMOS algorithm). My own preference would be for a simplified option for those people only wanting to use USB sources.

The problem with a FIFO is that it is bound to overflow or underflow eventually when the reading and writing clocks are not synchronized, so you have to come up with some trick to keep it about half full - like detecting silence in the signal and then inserting or removing some zero samples to get it half full again (which doesn't work when there is no silence).

It is just that Andrea is a no-compromise kind of guy. He wants to do everything the best he knows how, regardless of cost.

Using clock doublers with DSD and then trying to suppress the resulting mixed-down idle tones with a FIRDAC is certainly a compromise. I'd prefer another compromise: avoid the whole issue by not using clock doublers and accept that the close-in phase noise is a bit higher.

Does anyone know what kind of voltage reference Andrea uses?

Close-in phase noise and voltage reference noise both modulate the signal, close-in phase noise in phase (or equivalently in frequency) and voltage reference noise in amplitude. Both effects cause sidebands (skirts) around the desired signal in the spectrum, but those due to voltage reference noise are usually dominant by far. At least in psychoacoustic tests with simple waveforms, the sideband level at which amplitude modulation becomes audible is smaller than or about equal to the sideband level at which phase modulation becomes audible, depending on the modulating frequency. For both, the levels at which they become audible in these psychoacoustic tests are far above the sideband levels produced by any reasonable DAC.

I can't speak for Marcel, but I wouldn't be surprised if he were to say the dac he designed for this thread was, among other goals, meant to be diy'er friendly and of reasonable cost to build. If so, that wouldn't be a bad thing. It would mean more people could build it and enjoy it.

Yes, of course it is.

If you meant to imply that Andrea's designs are DIY'er unfriendly and of unreasonable cost, then it is the first thing you wrote in this thread that doesn't sound like an advertisement for Andrea 😉

Last edited:

In a nutshell, I'm wondering if the DSD streams are phase accurate (relative to one another & regardless if generated by the above MCHStreamer or something else), would 4 of the RTZ DSD boards work ok together?

I can't think of any reason why they wouldn't.

I'm thinking I might need a single clock distributed to the 4 boards, but not 100% sure about that.

Edit: including filter boards/power supplies of course, I'm just focusing on the core DACs 🙂

Can you find anything about the multichannel DSD output in the user manual? If they use four independent I2S interfaces to output raw DSD rather than I2S, maybe there are already four synchronous bit clocks available.

That's fine Acko, happy to build up a pair of boards, DAC and filter, for Marcel's RTZ for you if you're happy to cover costs. I'll PM you to progress.If there are no takers for this empty board then if you can provide assembled and tested one to Mark that would be great. I will cover your costs as indicated before🙂

So that begs the question of whether I should return the prototype to Marcel and send Mark the new build once it's done and tested? I have commitments next weekend (cycling 100miles for charity in the RideLondon event!) but have some leave the following week when I should be able to get the build done if I can get all the parts delivered in the next week or so.

- Home

- Source & Line

- Digital Line Level

- Return-to-zero shift register FIRDAC