Thanks!

Would using old mkrom.exe with new FW be problematic?

//

I don't remember. Why just not use the newest version mkrom.exe ?

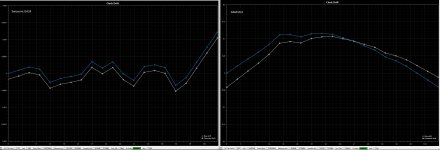

Here's a comparison of the clock drift of the DAM1021 vs. an old Swissonic DA24 converter via an DAAD roundtrip using a PCM4222EVM (AES/EBU output) as the AD converter and a couple of RME soundcards, both clocked via the PCM4222EVM's two AES/EBU outputs.

Test setups:

a)

digital connections:

PCM4222EVM (master) into RME hdspe via AES/EBU

DAM1021 (slave), fed from RME hdspe via AES/EBU

analog connections:

DAM1021 into PCM4222EVM

b)

digital connections:

PCM4222EVM (master) into RME hdspe via AES/EBU

Swissonic DA24 (slave), fed from RME 9652 via ADAT

analog connections:

DA24 into PCM4222EVM

The DA24 loop has the theoretical disadvantage of using two different sound cards with their own receiver chips and reclocking contraptions.

Nevertheless, as can be seen in the image (comparison generated via the free DeltaWave software) the DA24 is two orders of magnitude (100 times) better in terms of following the incoming clock (y axis is deviation, x axis is time in seconds). The DA24 is also faster to readjust over time.

This is just one snapshot, but it is representative of what is going on from previous measurements in various scenarios I have made.

I'd like to try with DAm1021 if

a) a longer term monitoring algorithm in the DAM1021 that gets a more accurate clock speeds measurement over time

b) a much faster as well as a much slower adjustment algorithm than the current 0.1 Hz

c) differences in the correction size

wouldn't lead to a better outcome.

Soeren, could you please add options to set the clock update rate and correction amount ourselves via the serial interface?

Is it possible to set the update speed of the clock much faster? Maybe even out of the audio range? Or would that effectively introduce audible jitter?

Test setups:

a)

digital connections:

PCM4222EVM (master) into RME hdspe via AES/EBU

DAM1021 (slave), fed from RME hdspe via AES/EBU

analog connections:

DAM1021 into PCM4222EVM

b)

digital connections:

PCM4222EVM (master) into RME hdspe via AES/EBU

Swissonic DA24 (slave), fed from RME 9652 via ADAT

analog connections:

DA24 into PCM4222EVM

The DA24 loop has the theoretical disadvantage of using two different sound cards with their own receiver chips and reclocking contraptions.

Nevertheless, as can be seen in the image (comparison generated via the free DeltaWave software) the DA24 is two orders of magnitude (100 times) better in terms of following the incoming clock (y axis is deviation, x axis is time in seconds). The DA24 is also faster to readjust over time.

This is just one snapshot, but it is representative of what is going on from previous measurements in various scenarios I have made.

I'd like to try with DAm1021 if

a) a longer term monitoring algorithm in the DAM1021 that gets a more accurate clock speeds measurement over time

b) a much faster as well as a much slower adjustment algorithm than the current 0.1 Hz

c) differences in the correction size

wouldn't lead to a better outcome.

Soeren, could you please add options to set the clock update rate and correction amount ourselves via the serial interface?

Is it possible to set the update speed of the clock much faster? Maybe even out of the audio range? Or would that effectively introduce audible jitter?

Attachments

Last edited:

According to the Si clock document, the settling time for a small change (<1000ppm) is about 100 uS, i.e. approx 4 samples. So changing clock more often I think is a no go.

//

//

Here's a comparison of the clock drift of the DAM1021 vs. an old Swissonic DA24 converter via an DAAD roundtrip using a PCM4222EVM (AES/EBU output) as the AD converter and a couple of RME soundcards, both clocked via the PCM4222EVM's two AES/EBU outputs.

.....

Soeren, could you please add options to set the clock update rate and correction amount ourselves via the serial interface?

Is it possible to set the update speed of the clock much faster? Maybe even out of the audio range? Or would that effectively introduce audible jitter?

The slow PLL on the dam1021 is on purpose, the FIFO takes up any differences.... The audio clock is supposed to be constant, a fast PLL is a disadvantage which can add jitter, especially if you don't have a FIFO, like that old DA24 probably don't have.....

So I see no need to change it, or to add options to adjust it. What will happen in next firmware release is the the clock adjustments will be in smaller steps....

Last edited:

The slow PLL on the dam1021 is on purpose, the FIFO takes up any differences.... The audio clock is supposed to be constant, a fast PLL is a disadvantage which can add jitter, especially if you don't have a FIFO, like that old DA24 probably don't have.....

So I see no need to change it, or to add options to adjust it. What will happen in next firmware release is the the clock adjustments will be in smaller steps....

will this future enhancement be made available to the dac1541?

My suspicion, with a hint of proof available, is that the DAM digital PLL algorithm can not end up in a none adjusting state even if it was fed a 1 ppm oscillator. NB not talking jitter or phase noise but frequency stability. It seem to hunt and go around the center in a trial strategy... it seems like its Q > 0,5 i.e. its not critically dampened.

50 ppm for a 49 Mhz clock is approx 2500 Hz. This is about 2,5 Hz for actual pitch which at least I can detect. DAM buffer is said to be 44 samples i.e. 22 in any direction meaning 0,5 ms. 2250 Hz is 0,4 ms - so if the if the algorithm was adaptive it should be able to leave the Si be if the DAM was fed a 50 ppm clock.

If one modulate a 340 Hz sinus with a varying 340+/- 2,5 Hz sinus one can really appreciate the impact of this kind of deviation. The DAM need a piano tuner really - it plays variably out of tune 🙂

Or did I fluke math again.

//

50 ppm for a 49 Mhz clock is approx 2500 Hz. This is about 2,5 Hz for actual pitch which at least I can detect. DAM buffer is said to be 44 samples i.e. 22 in any direction meaning 0,5 ms. 2250 Hz is 0,4 ms - so if the if the algorithm was adaptive it should be able to leave the Si be if the DAM was fed a 50 ppm clock.

If one modulate a 340 Hz sinus with a varying 340+/- 2,5 Hz sinus one can really appreciate the impact of this kind of deviation. The DAM need a piano tuner really - it plays variably out of tune 🙂

Or did I fluke math again.

//

Indeed, but with smaller & smaller steps and always less and less frequent if the source-clock is stable... should the performed test not be longer than one second so we see the PLL further stabelize?

Doing changes more often will make the clock stay relatively longer in its stabilising phase after a frequency change. In that phase I bet it is not a good clock.

//

//

I still wish for a music PLL mode and a Movie mode... despite after Christmas...

//

//

Last edited:

Run it on the built in USB and clock is apparently not touched.

I must have done a faulty calculation above re: the 2,5 Hz deviation... please someone tell me where!?

//

I must have done a faulty calculation above re: the 2,5 Hz deviation... please someone tell me where!?

//

Here's a comparison of the clock drift of the DAM1021 vs. an old Swissonic DA24 converter via an DAAD roundtrip using a PCM4222EVM (AES/EBU output) as the AD converter and a couple of RME soundcards, both clocked via the PCM4222EVM's two AES/EBU outputs.

What circuit are you using for the AES/EBU interface? Just wondering... Interesting would be to have the same test using the I2S interface (and the test running over a longer period).

Somehow I believe spdif could result in a better locking behavior as we avoid the isolators and their noise in the Dam1021.

Is the input selected or is it in 'auto'-mode?=> differences were reported, but I'm a bit in disbelief here but will try myself for sure.

After some bad soldering C122 ceramic capacitor has been demaged(doing VRef cap mod). I cannot find schematic for Dam1021 so can somebody prompt the vule of it ?

Run it on the built in USB and clock is apparently not touched.

I must have done a faulty calculation above re: the 2,5 Hz deviation... please someone tell me where!?

//

The stability is usually not the cycle to cycle stability but over a certain period of time, e.g. per second, per day, per year, ...

For the SI514 the 50ppm is the "total stability" ... for 10 years??? ... not very clear in the specs.

Your 2.5 Hz is the total stability of the 48kHz sampling frequency.

However the 340Hz sine will also be "totally" stable with 50ppm = 0.017Hz.

And if thats the variation in 10 years, well 😉

"However the 340Hz sine will also be "totally" stable with 50ppm = 0.017Hz."

Yeees - but if someone pokes the osc a few times per second or every other second and change its frequency by several hundred Hz - what happens then to the "stability" of the clock? Oscillator still on 50ppm of course... that's the crystal I suppose.... ehh?

//

Yeees - but if someone pokes the osc a few times per second or every other second and change its frequency by several hundred Hz - what happens then to the "stability" of the clock? Oscillator still on 50ppm of course... that's the crystal I suppose.... ehh?

//

If I recall my measurements correctly the "poking" it is not a few 100HZ but a few Hz. The oscillation due adjustment had a amplitude of about 10Hz of a 49MHz clock. So 0.2ppm. And 0.2ppm of 340Hz are 68uHz - but no idea if that's audible.

Last edited:

Thats not audible for sure.

OK, have you sorted out how this rate of change jives with a buffer of 44 samples?

//

OK, have you sorted out how this rate of change jives with a buffer of 44 samples?

//

- Home

- Vendor's Bazaar

- Reference DAC Module - Discrete R-2R Sign Magnitude 24 bit 384 KHz