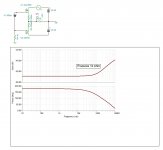

I don't understand the poor PSRR.

The output voltage is defined by the gate voltage not the power rails.

The output voltage is defined by the gate voltage not the power rails.

Early effect and capacitances.

Patrick

Thanks.

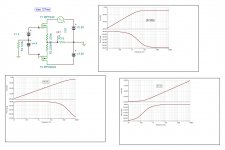

One way around it is to use bigger smoothing capacitors.

Feedback will help too.

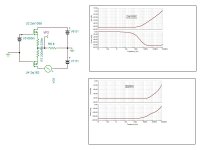

About early effect , the 2sj164 sim model has 138 ma for 0v gate when drain is 50v while the k has only 1.8ma . Is this normal or wrong modeled?Early effect and capacitances.

Patrick

Surely the output of any FET is defined by gate and drain voltages? FETs are not high output impedance devices like BJTs.nigelwright7557 said:The output voltage is defined by the gate voltage not the power rails.

PS I thought Early effect applies to BJTs alone - it expresses how far short the transistor falls from being a perfect current source.

Last edited:

Two distinct mechanism play a role here, and they shouldn't be mixed up: one is the equivalent of the Early effect for FET devices, the channel modulation, which happens under all conditions, including DC, and apart from massive feedback or cascoding has no solution, the other is the Miller capacitance effect between D and G, which is frequency-dependent and can easily be cured with a low drive impedance (the cascode also works in this case)These lateral MOSFETs are very commonly used on this forum, has anyone noticed the very poor power supply ripple rejection? Any solution? The feedback is bringing down to -90 db only if the gates are driven by high impedance.

- Home

- Amplifiers

- Solid State

- PSRR of 2SK1058/2SJ164