adding a resistor to the source of both devices reduces the Id and thus reduces the Pq.

That ends up looking like the style promoted by D.Feucht rather than the simpler B1/DCB1

That ends up looking like the style promoted by D.Feucht rather than the simpler B1/DCB1

Hi Andrew,

will this method increase the noise seen by the load? The 862s have really low noise, if lower Idss is needed one can simply use bf861, which looks quite similar to 862.

will this method increase the noise seen by the load? The 862s have really low noise, if lower Idss is needed one can simply use bf861, which looks quite similar to 862.

Does anyone know the real noise figures in dB of BF862, NXP has not published a plot of the noise figure and I don't know how to interpret nV/root Hz .

Output noise = Stage gain * sqrt(bandwidth) * Ein

If Ein is 1.2nV/rtHz and the stage gain is 1times (-0dB) then for a 20Hz to 20kHz bandwidth the output noise due to Ein is:

1 * sqrt( 20000 - 20) * 1.2 = 1* 141 * 1.2 = 169nVrms

Now compare to a power amplifier with an Ein = 10nV/rtHz and a stage gain of 27times

Output noise due to Ein = 27 * 141 * 10 = 38070nV = 38uVrms ~ 0.04mVrms

If Ein is 1.2nV/rtHz and the stage gain is 1times (-0dB) then for a 20Hz to 20kHz bandwidth the output noise due to Ein is:

1 * sqrt( 20000 - 20) * 1.2 = 1* 141 * 1.2 = 169nVrms

Now compare to a power amplifier with an Ein = 10nV/rtHz and a stage gain of 27times

Output noise due to Ein = 27 * 141 * 10 = 38070nV = 38uVrms ~ 0.04mVrms

Last edited:

Almost not at all...........will this method increase the noise seen by the load? ............

Signal to Noise Ratio = 20log(Signal/Noise)

If your signal is for 1W into 8ohms, then Signal = 2.828Vac = 28280mVac

Noise = 0.04mVrms

S/N = 20log(28280/0.04) = 97dB ref 1W for a 10nV/rtHz power amplifier.

If your signal is for 1W into 8ohms, then Signal = 2.828Vac = 28280mVac

Noise = 0.04mVrms

S/N = 20log(28280/0.04) = 97dB ref 1W for a 10nV/rtHz power amplifier.

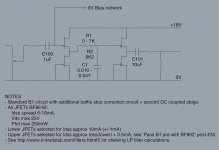

2 Stage B1 with BF861B and BSC network

Dear diyers,

I was thinking of building a 2 stage B1 with baffle step correction between the stages. Please see attached diagram. I have built the B1 with LSK170 and I am very happy with it. For this project I wanted to use BF861B's (Vds max 25V, Ptot 250mW max, yfs 16-25mS), selected for about 10mA Idss, upper JFET Idss a bit greater than lower as per post #35.

In practice, R1 in the comp network would be DIP switched series resistors of 1K, 2K, 4K and C1 DIP switched parallel caps of 0.01uF, 0.015uF and 0.022uF. This should give a nice set of possibilities with fz about 300Hz to 2kHz and A 0dB to about -6dB.

As you can see, I was intending to DC couple the two followers - the 9V (approx) bias is already there for the 2nd stage.

Any comments before I commit to making this would be appreciated. Will it work?

Thanks.

Dear diyers,

I was thinking of building a 2 stage B1 with baffle step correction between the stages. Please see attached diagram. I have built the B1 with LSK170 and I am very happy with it. For this project I wanted to use BF861B's (Vds max 25V, Ptot 250mW max, yfs 16-25mS), selected for about 10mA Idss, upper JFET Idss a bit greater than lower as per post #35.

In practice, R1 in the comp network would be DIP switched series resistors of 1K, 2K, 4K and C1 DIP switched parallel caps of 0.01uF, 0.015uF and 0.022uF. This should give a nice set of possibilities with fz about 300Hz to 2kHz and A 0dB to about -6dB.

As you can see, I was intending to DC couple the two followers - the 9V (approx) bias is already there for the 2nd stage.

Any comments before I commit to making this would be appreciated. Will it work?

Thanks.

Attachments

- Status

- Not open for further replies.

- Home

- Amplifiers

- Pass Labs

- Pass B1 pre with BF862