Hello Henry,

I have replaced the FETs with 12AU7/12AX7 for simulation in your A2 Design (with no other changes), they seem to be performing just as well.

May be that will tone down the harshness you heard from your original design?

Or may be just something new to try.

Thanks

Mallik

I have replaced the FETs with 12AU7/12AX7 for simulation in your A2 Design (with no other changes), they seem to be performing just as well.

May be that will tone down the harshness you heard from your original design?

Or may be just something new to try.

Thanks

Mallik

Interesting. I would check your simulation. IIRC, A1 and A2 bias the input stage at 2.5mA per side. Check the tube data sheets. There is no way to make them work in this circuit with only 8V on the plates.

FWIW, A1 may have had a little problem before I changed the compensation, but A2 was always smooth-sounding. I've thought hard about building a version of A2 with a tube input stage. It would take more voltage, and a non-trivial redesign to make the circuit safe during warm-up, and in the event of tube heater failure.

FWIW, A1 may have had a little problem before I changed the compensation, but A2 was always smooth-sounding. I've thought hard about building a version of A2 with a tube input stage. It would take more voltage, and a non-trivial redesign to make the circuit safe during warm-up, and in the event of tube heater failure.

I doubt simulators know what starved anode regime means...15...50v supplied ecc83 will make for a good guitar FX.

Interesting. I would check your simulation. IIRC, A1 and A2 bias the input stage at 2.5mA per side. Check the tube data sheets. There is no way to make them work in this circuit with only 8V on the plates.

FWIW, A1 may have had a little problem before I changed the compensation, but A2 was always smooth-sounding. I've thought hard about building a version of A2 with a tube input stage. It would take more voltage, and a non-trivial redesign to make the circuit safe during warm-up, and in the event of tube heater failure

Might be an issue with the spice model I am working with. I just ran it as a preliminary check.

You could run the input LTP on a separate high voltage single Rail, and the rest of the circuit on +-18v.

Also take a look at John Broskie's Voltage Quintupler circuit. You wont need additional voltages on the transformer. and can run the Tube LTP on 90v rail.

I don't have a 12AU7 SPICE model, and I'm too lazy to go find one right now. I do have a 12AX7 model, though. I've been busy, so I asked my cat to run the simulation. He's just like me, enjoys audio design. In fact, when I show people my projects, they often ask, "Hey, did you design that, or is it something the cat dragged in?" Anyway, my cat says the simulation works just fine with a 12AX7 in place of the 2N5564. I asked him how that could be and he just rolled his eyes at me and said, "Meow, meow. Meow, meow, meow. Meow." Then he went on catdiyaudio.com and posted a message about how stupid and embarrassing his owner is.

We talked about it and my cat explained that SPICE simulations can be useful, but you can't trust them blindly. He said the tube model probably wasn't designed to give realistic results at such an unusual operating point. In the end, I had to concede he was probably right. He did say the circuit could probably be made to work well with a proper power supply and a low-meow triode.

We talked about it and my cat explained that SPICE simulations can be useful, but you can't trust them blindly. He said the tube model probably wasn't designed to give realistic results at such an unusual operating point. In the end, I had to concede he was probably right. He did say the circuit could probably be made to work well with a proper power supply and a low-meow triode.

Don't take it personally. All persons, indeed all non-cats, are stupid and embarrassing to a cat.he went on catdiyaudio.com and posted a message about how stupid and embarrassing his owner is.

You are valued until Cat learns to work the can opener.

After much more work than I expected, I got the HPA1 rebuild working tonight. I still need to finish a few details, but I'm listening to it right now. I wasn't planning on doing this, but I took the DCG3 apart and liberated its power supply for the new build.

My first thought when I started listening to the HPA1 was, "This sounds exactly the same; I'm fooling myself." It's a nice sounding amplifier.

Then I switched back to the HPA2 and had the same impression as my first audition. The HPA2 seems to have a softer overall tonality, with more body in the midrange and more ambience. The HPA2 may have more bass, or it may be that the amount of bass is the same, but the difference in tonal balance makes it seem that way. I hate the word "seems" in audio reviews because it implies uncertainty, but it can also mean, "giving the impression or sensation."

I find this all very interesting. I keep saying I don't have golden ears, and I don't. But it's easy to start thinking like an audiophile, even if you don't want to, as soon as you start listening for differences between equipment. Again, these differences may be very subtle, or illusory. Or, a golden ear type might say the difference is night and day.

At the end of the day, what matters is if you enjoy listening. I decommissioned the DCG3 because, after building the HPA1, I didn't want to listen to it anymore. I'm enjoying the HPA1 right now. They're both good amplifiers, with slightly different characters. But I believe I prefer HPA2.

As always, your mileage may vary.

I said to my cat, "Cat, check out my new amplifier."

"Meow, looks the same as the old one," he replied.

"I know," I said. "The definition of insanity is doing the same thing over and over again and expecting different results."

"Hurm," said the cat. "I can tell you right meow, I'm sure it sounds like cat pee."

"Well, that's incredibly rude," I blurted out, giving him an angry look.

The cat shrugged. "Op-amp regulators. What can I spray?"

"You can't possibly know what it sounds like," I scolded. "You're a cat. And you haven't listened to it yet."

I had to wait while he licked his thigh. Finally, he answered. "Hey, in a blind test, I correctly identified different cat food brands in eight out of eight trials."

"Fine," I said, exasperated. "If you think you're so smart, let me see something you've built."

He pretended to ignore me and instead hopped up on the counter where I had placed a can of chicken kitty mush. "You got a can opener?" he asked.

"Get a job and buy your own!" I shouted, and stomped off. Stupid cat.

This is the A3 in its nearly finished form. The Elma attenuator shown here is the one with the broken index stop. I have Vishay-Dale metal film resistors coming this week to rebuild the Eizz attenuator. Once done, the Elma will come out and Eizz will go into the A3 in its place.

I took my other Elma attenuator out of the awful Aikido preamp and replaced all ninety-six resistors (huge job) with new Vishay RN55s, converting it from 100K to 20K impedance. I put it in the A2, in place of the stock Eizz. I could not shake the feeling the amp was missing something with the Eizz in there. Indeed, it sounds noticeably more transparent with the metal film ladder attenuator. I won't try to explain or justify that observation.

I'm not gonna lie, trying to play at being an audiophile, and straddling the fence between the objectivist and subjectivist camps was really awkward and stressful. I have no patience for audio dogma. No doubt, I over-reacted, so sorry about that. But I am an engineer first, and that's just the way it's gonna be.

I do want to say, I've put a lot of hours on the A2 and the A3 in the past couple of months. I have the distinct sense, imagined or not, that break-in and warm-up are a thing -- much as it pains me to admit it. The A3 was actually quite awful when new. It is now thoroughly broken-in and sounds tolerable from a cold start, but prefers to warm up for an hour or two before listening. The A2 doesn't seem to change much with warm-up, but if I let it sit for a week or two without power, it sounds very thin and bright until it's been on for a few hours. I do not pretend to understand these things, or even know if they are "real" effects. I've decided not to over-think it.

My impression of the two amps is consistent now. The story hasn't changed much. The A3 is noticeably warmer and more full-bodied, and this enhances the ambience and soundstage in a pleasant way. It is very easy and engaging to listen to. I cannot say if this is due to its distortion character, or something less esoteric like output impedance. The A2, in contrast, sounds leaner, though not necessarily more detailed. After listening to the A2 for a while, the A3 sounds a little bloated in the midbass. What is remarkable (to me) about the A2 is that it does not sound overly bright, nor electronic, nor is it lacking in warmth. It's just a slightly different, more analytical presentation. I don't have a clear preference between the two; it depends on my mood.

Oddly, I cannot get interested in listening to the A30 Pro at all, though I've tried hard to like it. Everything is there in the sound, but it bores me. Again, I can't explain or prove that. It just is what it is.

I received my 100VA Toroidy SUPREME AUDIO GRADE V2 power transformer weeks ago but haven't made any progress on the official HPA-1 power supply. The transformer is huge. I believe the Super Regulator is a good circuit. Since both amps have the same supply (excepting the one is +-24V whereas the other is +-17V), I believe this lets me compare the two signal circuits, apples to apples. At some point I may build another HPA-1 clone with the recommended supply so I can evaluate them directly. For now I am satisfied with the A3 as-is.

I have also spent some time with the A1 (with Miller compensation) and find it sounds very much like the A2. The A1 is still on the breadboard. The PCBs are a little shopworn and I'm not sure if I'm going to repackage it, though I do have a third identical box in the works.

I would encourage people to build any of these amps, if you can get the parts. I can't recommend the A1 with its original two-pole compensation, but it sounds very good with the Miller scheme. Possibly this could be resolved with some tweaking. I recommend the A3 if you are looking for something that's easier to build and has a unique sonic character. If you prefer a more conventional hi-fi sound, build the A2. Or just save yourself a lot of bother and build a WHAMMY kit or an RJM Sapphire. Or buy a Topping amp and don't worry about it.

I'm very busy with work and don't have any new projects planned for now. I just wanted to give this update for completeness.

I have the distinct sense, imagined or not, that break-in and warm-up are a thing -- much as it pains me to admit it.

I believe the Super Regulator is a good circuit.

We'll read along to find out if more pain awaits in the next episode of 'cat tales' 🙂

Parts came today (Vishay-Dale RN50s) and I rebuilt the EIZZ attenuator, and installed it in the A3. Sounds very good. This is not an inexpensive attenuator -- it's about $50 worth of resistors, and $60 for the stock attenuator -- but it's a lot cheaper than a DACT. I'm listening to Sonny Rollins "Way Out West" right now and it's pretty amazing, so no complaints about the volume control.

I modified the A3 circuit and threw it in SPICE over the weekend. Similar overall concept, but very different nonetheless, especially if you take the attitude that every little thing matters. All bipolar, classic circuit, not at all original. I'm reluctant to share right now, but it could be another New Headphone Amplifier Design. I haven't shown the schematic to the cat yet, either. I'm not interested in his sarcatsic comments.

Looks great! What are you going for with this design?

I'm not sure your cat needs any more headphone amps though to be honest 😉!

I'm not sure your cat needs any more headphone amps though to be honest 😉!

I'm not really sure where I'm going. It's basically an A3 with my A2 diamond buffer output stage, and a diamond buffer input stage, too. So, in that sense, not an HPA-1 clone at all since the only thing it has in common is the current mirrors in the middle. It's more of a standard current-feedback topology like you can see published everywhere. I need to do some more analysis in the simulator to work out the internal gain structure. The HPA-1 has very aggressive loading on the VAS to keep the loop gain down. This circuit has about 20 dB more loop gain than the A3, which is just controlled by two resistors. The feedback network works differently in a CFA. Loop gain depends on the value of Rf and the transresistance of the middle stage. I suppose the intent is the same as always: to build it, see if it's stable, and whether it has an identifiable sound signature.

I won't release the schematic until it's done because I don't want to invite nit-picking.

I won't release the schematic until it's done because I don't want to invite nit-picking.

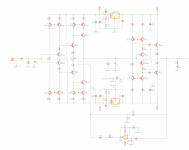

I decided to post my schematic. As I said, I make no claims as to originality, and I'm not really interested in hearing about why it sucks.

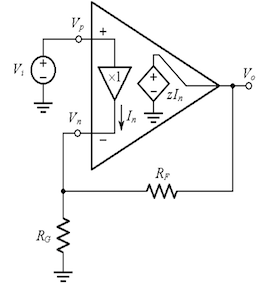

Referring to these generic diagrams (full schematic is below):

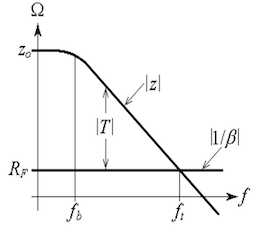

Breaking the feedback loop, applying a voltage Vi to the non-inverting input results in a current In = Vi / Rg flowing out of the inverting terminal. This current is mirrored to the output load impedance Zo, producing an output voltage Vo = In * Zo. It follows that the open-loop voltage gain is just Aol = Zo / Rg. In my circuit, at DC, this is 200 * log(100K / 332) = 49.6dB.

Connecting the feedback resistor Rf, a feedback current If = (Vo - Vi) / Rf flows back into the inverting input. Loop gain is just the difference between Aol and Acl. With a little math, you can show that the loop gain is given by |T| = Zo / Rf. At DC, this is just 20 * log(100K / 332) = 42.5dB. There is a dominant pole in the open-loop response at frequency 1 / (2 * pi * Rl * Cdom) = 33.9 kHz. This is confirmed by the SPICE Bode plot. Closed-loop gain is 1 + (Rf / Rg) = 1 + (750 / 332) = 3.26. We lose a little in the input divider network; call the final closed-loop gain 10 dB.

Closed-loop bandwidth is the frequency where the loop gain falls to unity, around 2 MHz. Increasing Rf raises the closed-loop gain and lowers the closed-loop bandwidth. On the other hand, if we change the closed-loop gain by varying Rg, the closed-loop bandwidth remains the same. This is because both the open- and closed-loop gains are affected equally by Rg (on a log scale). As we change Rg, the two curves rise or fall by the same amount, and the frequency where they intersect stays constant.

There's obviously a limit to how far we can go with this since the input buffer output impedance is non-zero. That is, we can't get infinitely high open-loop gain by setting Rg to zero. There are some practical limits on the value of Rg. Intuitively, values around ten times the buffer output impedance seem to make sense.

From a design standpoint, we might start by deciding how much loop gain (feedback) we want. I arbitrarily picked 40 dB with the intent of maybe drying up the sound a little bit compared to the HPA-1. It's unclear why Zo is set so low (4.7K | 4.7K = 2.35K) in the Pass Labs amplifier. Perhaps this is to swamp the nonlinear input capacitance of the MOSFET output stage, or maybe it was just selected by ear. Lower values of Zo mean correspondingly higher currents flow out of the driver stage. The diamond buffer output stage in the new design presents a friendlier input load, so I set the driver load resistor at 100K. It follows that Rf = 750 Ohms gets us close to our 40 dB loop gain target.

From there, we can select the value of Cdom. There's plenty of phase margin, so I picked 47pF. This is about fifteen times lower than the combined capacitive load seen by the A3 driver. Open-loop frequency response is flat across the audio band, which some people think is a good thing. I am adopting a distinctly anti-Self approach here of not trying to maximize midband NFB.

Slew rate is less of a problem in a CFA because the Cdom charging current comes from the feedback network. But I couldn't think of a good reason to use a larger capacitor, which would require lowering resistor values all around to get to my open-loop gain and bandwidth targets.

I have cribbed the DC servo from the HPA-1 clone. The stock servo output resistor is given as 150K. This is relatively high, presumably to minimize interaction of the audio signal with the servo. This means the op-amp will have to swing a correspondingly larger voltage to cancel a given output offset. I reduced the value to 100K in this design because my rail voltages are lower and I don't want the servo amp to run out of voltage headroom. In practice, it shouldn't matter.

I have added my driver stage regulators, just because. These devices are unavailable right now, but I have a stash of them. A capacitance multiplier would be easier to source parts for, and would be more in keeping with the HPA-1 design philosophy. But I was lazy and didn't feel like solving another layout problem. And this is not an HPA-1.

I've also added an input ultrasonic filter. It may not be needed in a CFA, and the HPA-1 doesn't have one. But I don't see the point of extending wide-open arms to RF at the input, so there you go.

I changed the output transistors from KSA1220/KSC2690 (in the A3) to TTA/TTC004B. In the SPICE simulation, the KSA1220 is doing a weird thing where the base-emitter junction breaks down at higher output currents. The TTA004B does not exhibit this behavior, and I saw no issue on the bench with the A2. The TTA/TTC parts are still in production, whereas the KSA1220 is not (though I have some on hand). The KSA/KSC parts are rated for higher Ft, but the former devices are plenty fast enough for this application.

I debated getting rid of the output diamond cross-coupling connections on account of the very low collector-emitter voltage (~1.2V) available to Q11 and Q13. But the TTA/TTC004B are specified for a low saturation voltage and the output stage works fine in the A1/A2. Cross-coupling reduces simulated distortion by a small margin, so I decided to leave the cross-coupling as-is. I did not cross-couple the input diamond buffer because it doubles the current in Q9 and Q14 with no apparent improvement in overall distortion.

I tossed the output inductor because the amplifier is not significantly affected by capacitive output loads on account of the generous phase margin. Similarly, the output Zobel network doesn't do much in the simulator, but I left it in as a reflex.

I set all the mirror emitter resistors to 100 Ohms as I saw no need for current gain in the middle stage mirror (as used in the HPA-1). I moved the offset trimpot to the junction of the input buffer emitter resistors because I like the symmetry. You can debate the sonic horrors of passing the feedback signal through a potentiometer wiper, but I won't worry about it.

The whole thing hangs together nicely in SPICE with a clean square wave response and no tendency to misbehave with capacitive loads, or under clipping. The distortion plot above was at 1.5VRMS output into 32 Ohms. Distortion products rise with higher output voltages, as is the case with the HPA-1 measurements published by Stereophile. Simulated THD is under 0.01%, and more like 0.001%, under most operating conditions.

You could argue that this whole exercise is pointless since there is no hope of my bettering the HPA-1. Still, if I can get the parts, I will build this soon. I expect it will sound fine. Since I have another chassis ready to go, I will have three physically similar headphone amplifiers, and only one pair of ears. I can't complain about the sound of the A2 and A3 (or the A1, for that matter). Perhaps I will put some of these amps up for sale, dunno. I will probably just put the A1 PC boards in plastic bags and throw them in my bedside table drawer, along with the DCG3 board.

I have put my Kicad files on GitHub: https://github.com/hapasternack/A4. I'm not soliciting contributions, but I suppose if anyone wants to suggest improvements you can send me pull requests and I will look at them. I will report on my progress with this project, but will leave my cat to respond to any naysayers.

The cat was looking over my shoulder the other night while I worked on this, and smirking. I asked him what was so funny, but he just shook his head and refused to say anything. I told him if he didn't have anything nice to say, he could keep it to himself. He just smirked some more and started chewing on the cable to my soldering iron. So I ignored him.

Referring to these generic diagrams (full schematic is below):

Breaking the feedback loop, applying a voltage Vi to the non-inverting input results in a current In = Vi / Rg flowing out of the inverting terminal. This current is mirrored to the output load impedance Zo, producing an output voltage Vo = In * Zo. It follows that the open-loop voltage gain is just Aol = Zo / Rg. In my circuit, at DC, this is 200 * log(100K / 332) = 49.6dB.

Connecting the feedback resistor Rf, a feedback current If = (Vo - Vi) / Rf flows back into the inverting input. Loop gain is just the difference between Aol and Acl. With a little math, you can show that the loop gain is given by |T| = Zo / Rf. At DC, this is just 20 * log(100K / 332) = 42.5dB. There is a dominant pole in the open-loop response at frequency 1 / (2 * pi * Rl * Cdom) = 33.9 kHz. This is confirmed by the SPICE Bode plot. Closed-loop gain is 1 + (Rf / Rg) = 1 + (750 / 332) = 3.26. We lose a little in the input divider network; call the final closed-loop gain 10 dB.

Closed-loop bandwidth is the frequency where the loop gain falls to unity, around 2 MHz. Increasing Rf raises the closed-loop gain and lowers the closed-loop bandwidth. On the other hand, if we change the closed-loop gain by varying Rg, the closed-loop bandwidth remains the same. This is because both the open- and closed-loop gains are affected equally by Rg (on a log scale). As we change Rg, the two curves rise or fall by the same amount, and the frequency where they intersect stays constant.

There's obviously a limit to how far we can go with this since the input buffer output impedance is non-zero. That is, we can't get infinitely high open-loop gain by setting Rg to zero. There are some practical limits on the value of Rg. Intuitively, values around ten times the buffer output impedance seem to make sense.

From a design standpoint, we might start by deciding how much loop gain (feedback) we want. I arbitrarily picked 40 dB with the intent of maybe drying up the sound a little bit compared to the HPA-1. It's unclear why Zo is set so low (4.7K | 4.7K = 2.35K) in the Pass Labs amplifier. Perhaps this is to swamp the nonlinear input capacitance of the MOSFET output stage, or maybe it was just selected by ear. Lower values of Zo mean correspondingly higher currents flow out of the driver stage. The diamond buffer output stage in the new design presents a friendlier input load, so I set the driver load resistor at 100K. It follows that Rf = 750 Ohms gets us close to our 40 dB loop gain target.

From there, we can select the value of Cdom. There's plenty of phase margin, so I picked 47pF. This is about fifteen times lower than the combined capacitive load seen by the A3 driver. Open-loop frequency response is flat across the audio band, which some people think is a good thing. I am adopting a distinctly anti-Self approach here of not trying to maximize midband NFB.

Slew rate is less of a problem in a CFA because the Cdom charging current comes from the feedback network. But I couldn't think of a good reason to use a larger capacitor, which would require lowering resistor values all around to get to my open-loop gain and bandwidth targets.

I have cribbed the DC servo from the HPA-1 clone. The stock servo output resistor is given as 150K. This is relatively high, presumably to minimize interaction of the audio signal with the servo. This means the op-amp will have to swing a correspondingly larger voltage to cancel a given output offset. I reduced the value to 100K in this design because my rail voltages are lower and I don't want the servo amp to run out of voltage headroom. In practice, it shouldn't matter.

I have added my driver stage regulators, just because. These devices are unavailable right now, but I have a stash of them. A capacitance multiplier would be easier to source parts for, and would be more in keeping with the HPA-1 design philosophy. But I was lazy and didn't feel like solving another layout problem. And this is not an HPA-1.

I've also added an input ultrasonic filter. It may not be needed in a CFA, and the HPA-1 doesn't have one. But I don't see the point of extending wide-open arms to RF at the input, so there you go.

I changed the output transistors from KSA1220/KSC2690 (in the A3) to TTA/TTC004B. In the SPICE simulation, the KSA1220 is doing a weird thing where the base-emitter junction breaks down at higher output currents. The TTA004B does not exhibit this behavior, and I saw no issue on the bench with the A2. The TTA/TTC parts are still in production, whereas the KSA1220 is not (though I have some on hand). The KSA/KSC parts are rated for higher Ft, but the former devices are plenty fast enough for this application.

I debated getting rid of the output diamond cross-coupling connections on account of the very low collector-emitter voltage (~1.2V) available to Q11 and Q13. But the TTA/TTC004B are specified for a low saturation voltage and the output stage works fine in the A1/A2. Cross-coupling reduces simulated distortion by a small margin, so I decided to leave the cross-coupling as-is. I did not cross-couple the input diamond buffer because it doubles the current in Q9 and Q14 with no apparent improvement in overall distortion.

I tossed the output inductor because the amplifier is not significantly affected by capacitive output loads on account of the generous phase margin. Similarly, the output Zobel network doesn't do much in the simulator, but I left it in as a reflex.

I set all the mirror emitter resistors to 100 Ohms as I saw no need for current gain in the middle stage mirror (as used in the HPA-1). I moved the offset trimpot to the junction of the input buffer emitter resistors because I like the symmetry. You can debate the sonic horrors of passing the feedback signal through a potentiometer wiper, but I won't worry about it.

The whole thing hangs together nicely in SPICE with a clean square wave response and no tendency to misbehave with capacitive loads, or under clipping. The distortion plot above was at 1.5VRMS output into 32 Ohms. Distortion products rise with higher output voltages, as is the case with the HPA-1 measurements published by Stereophile. Simulated THD is under 0.01%, and more like 0.001%, under most operating conditions.

You could argue that this whole exercise is pointless since there is no hope of my bettering the HPA-1. Still, if I can get the parts, I will build this soon. I expect it will sound fine. Since I have another chassis ready to go, I will have three physically similar headphone amplifiers, and only one pair of ears. I can't complain about the sound of the A2 and A3 (or the A1, for that matter). Perhaps I will put some of these amps up for sale, dunno. I will probably just put the A1 PC boards in plastic bags and throw them in my bedside table drawer, along with the DCG3 board.

I have put my Kicad files on GitHub: https://github.com/hapasternack/A4. I'm not soliciting contributions, but I suppose if anyone wants to suggest improvements you can send me pull requests and I will look at them. I will report on my progress with this project, but will leave my cat to respond to any naysayers.

The cat was looking over my shoulder the other night while I worked on this, and smirking. I asked him what was so funny, but he just shook his head and refused to say anything. I told him if he didn't have anything nice to say, he could keep it to himself. He just smirked some more and started chewing on the cable to my soldering iron. So I ignored him.

Last edited:

For anyone who is actually following, this is a typo. I meant to say "A2." A3, evidently, has FQP MOSFET outputs.I changed the output transistors from KSA1220/KSC2690 (in the A3) to TTA/TTC004B.

Can you post your PSU SPICE file?Thanks. I will look at the simulation this weekend.

I built a power supply tonight.

View attachment 1019481

The kitten found use for the empty Mouser box.

View attachment 1019482

Edit: I just realized -- "Kitten... Mouser." Haha, joke.

The power supply regulator is built exactly according to Jan Didden's schematic. I didn't bother simulating it on the assumption that the design is fully worked out by now.

https://www.diyaudio.com/community/threads/super-regulator.247281/

Here are the Kicad files:

https://www.dropbox.com/s/oy1sgmckvbb15nk/Super-Regulator Combined Dual.zip?dl=0

https://www.diyaudio.com/community/threads/super-regulator.247281/

Here are the Kicad files:

https://www.dropbox.com/s/oy1sgmckvbb15nk/Super-Regulator Combined Dual.zip?dl=0

- Home

- Amplifiers

- Headphone Systems

- New Headphone Amplifier Design