Here is a very readable and fairly comprehensive guide to the Buffalo 3 (written for the older ES9018):

http://www.twistedpearaudio.com/doc...-Buffalo_III_DAC_Integration_Guide_V2.1.3.pdf

See page 11. You want:

Pin 1: MCLK1 to EXT_MCK or unconnected

Pin 2: GND

Pin 3: DATA1 to D2

Pin 4: GND

Pin 5: BCK1 to DCK

Pin 6: GND

Pin 7: LRCK1 to D1

Pin 8: GND

Realize that the I2S signal from your Denafrips Hermes DDC is sensitive to all manner of interference, which is why it is important to keep the connection as short as possible. If that is inconvenient, then there is a Twisted Pear module specifically designed to allow the I2S connection to stretch 30 meters or so. It is called the Teleporter, and it has a small footprint so it might fit inside your DDC in place of the existing RJ45 socket. It also requires a low-current 5 volt source, which shouldn't be too hard to find. You would use a second Teleporter near the Buffalo 3, and you can conveniently connect the Teleporter to the Buffalo3 using small shielded u.fl cables. That would be an optimal setup for the very best performance. If you prefer to use a simple wired I2S connection, then it is probably better to not connect the DDC's MCLK, because the ES9028 can then compensate for small timing errors that may be introduced into the I2S.

Enjoy your project,

Frank

http://www.twistedpearaudio.com/doc...-Buffalo_III_DAC_Integration_Guide_V2.1.3.pdf

See page 11. You want:

Pin 1: MCLK1 to EXT_MCK or unconnected

Pin 2: GND

Pin 3: DATA1 to D2

Pin 4: GND

Pin 5: BCK1 to DCK

Pin 6: GND

Pin 7: LRCK1 to D1

Pin 8: GND

Realize that the I2S signal from your Denafrips Hermes DDC is sensitive to all manner of interference, which is why it is important to keep the connection as short as possible. If that is inconvenient, then there is a Twisted Pear module specifically designed to allow the I2S connection to stretch 30 meters or so. It is called the Teleporter, and it has a small footprint so it might fit inside your DDC in place of the existing RJ45 socket. It also requires a low-current 5 volt source, which shouldn't be too hard to find. You would use a second Teleporter near the Buffalo 3, and you can conveniently connect the Teleporter to the Buffalo3 using small shielded u.fl cables. That would be an optimal setup for the very best performance. If you prefer to use a simple wired I2S connection, then it is probably better to not connect the DDC's MCLK, because the ES9028 can then compensate for small timing errors that may be introduced into the I2S.

Enjoy your project,

Frank

Hello Frank,

Thanks so much for your help. Greatly appreciated.

I plan to use a very short cable, so I'll follow your advice, and leave Pin 1 unconnected.

Cheers,

narla

Thanks so much for your help. Greatly appreciated.

I plan to use a very short cable, so I'll follow your advice, and leave Pin 1 unconnected.

Cheers,

narla

Hi all,Hello,

today flashed sync firmware to atiny85 an now all dsd files play without unlocks 🙂) but with some light noise on both channels.

As for the sync mode: how to set dpll switches. for true sync mode dpll should be completely off? how to do so.

For switch 1 pos 1: what does normal mode mean?

BR

Branko

I am wondering the same thing and cannot find any answer anywhere on the www; How do the Dip Switch settings work for the DPLL at the BIIISE Pro?

Standard SW2 Dip sw 5-8 are ON = default.

I interpreted the following:

If switch 5 is the low bit than the setting 5= OFF, 6 = ON, 7 = ON, 8= ON will set the lowest value.

Set all to OFF you will set the highest value.

But how does it work with all the settings in between?

Does someone has a matrix or logic for that?

The integration guide for the BIIISE shows a matrix but the Pro has a 4 bit setting.

Currently I’m on the following setting:

5-ON, 6-OFF, 7-ON, 8-ON. Is this one setting higher than the lowest?

What is the next step? 7-OFF and the others ON?

Thank you,

Jordo

Attached is a binary to decimal conversion table. On the binary side, the zeros and ones are your switch positions, starting with 8 on the left and 5 on the right.But how does it work with all the settings in between?

Does someone has a matrix or logic for that?

if 'OFF' = 1, and 'ON'=0, then b0010 is the rather low bandwidth of d2. One step higher would be (#8->#5) b0011 or on, on, off, offCurrently I’m on the following setting:

5-ON, 6-OFF, 7-ON, 8-ON. Is this one setting higher than the lowest?

If you have DSD noise, perhaps start with the highest bandwidth (d16 or b1111 = all off) to learn if the noise can be diminished by bandwidth. If so, then tweak away... 🙂

Edit: I should add that register 12 in the 9028 and 9038 is 8 bits and the low 4 bits control DSD bandwidth while the high 4 bits control PCM bandwidth. I don't know offhand how Russ's firmware manages exactly. I would guess that, for example, a d8 setting of the B3 switches gives you the same bandwidth for BOTH PCM and DSD. I find that I need more bandwidth for DSD than for PCM. Indeed, the chip defaults are d5 for PCM and d10 for DSD.

Attachments

Last edited:

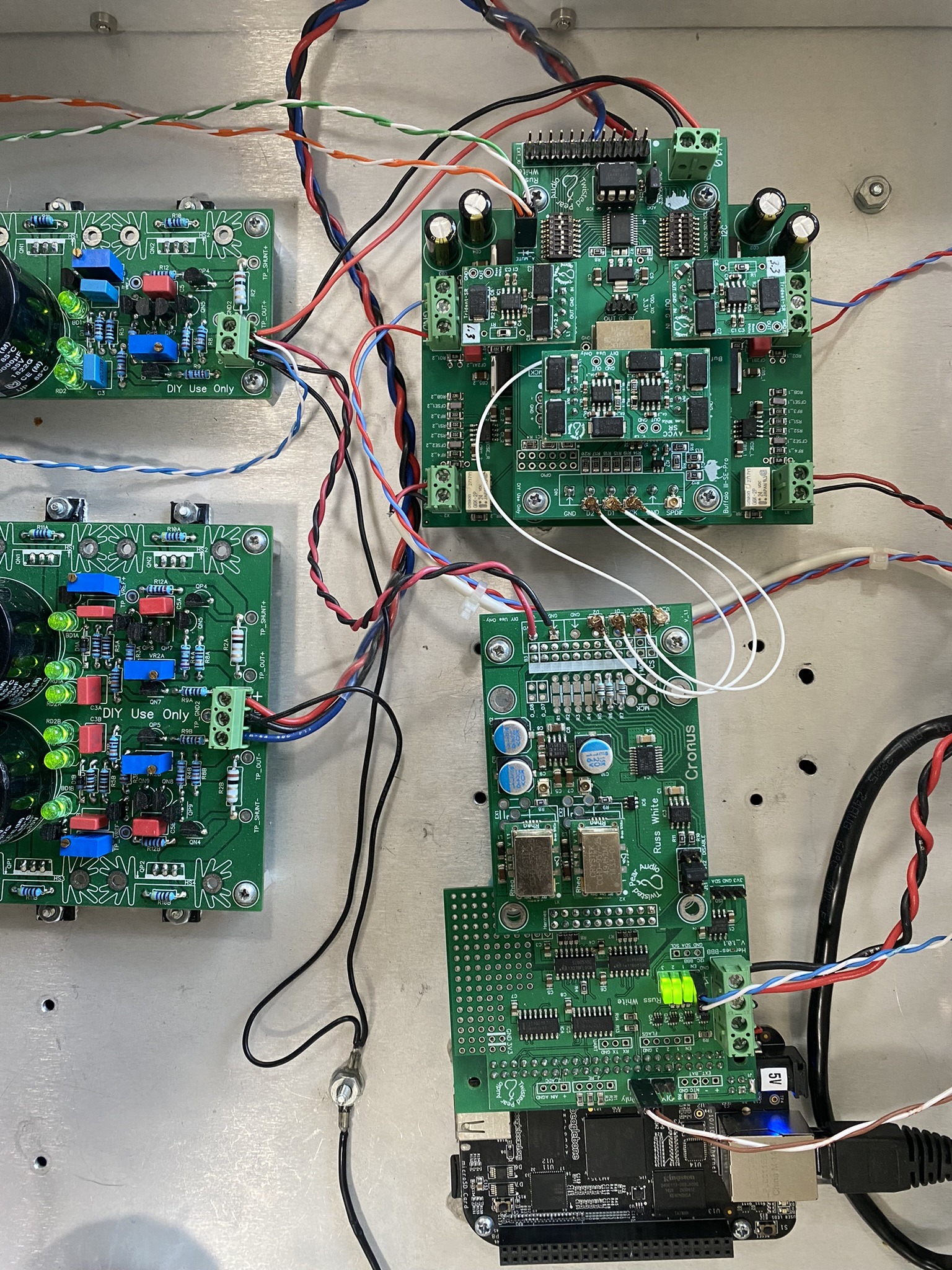

Tried sync mode with my BBB/Hermes/Cronus setup today. Been using async for years and has been working great. Reading back in this forum it seemed to be a simple matter of connecting Cronus master clock output to Buffalo and removing power supply to the Buffalo clock. Didn't work for me at all, just got silence. Changed DPLL to 1111, no luck. Using stock firmware and UFL cables. Am I forgetting something?

Perhaps it is a question of correctly initializing on power-up. Is there a way to be sure the Cronus master clock is started and stable before power goes to the B3, or the initialization reset is performed?Tried sync mode with my BBB/Hermes/Cronus setup today. Been using async for years and has been working great. Reading back in this forum it seemed to be a simple matter of connecting Cronus master clock output to Buffalo and removing power supply to the Buffalo clock. Didn't work for me at all, just got silence. Changed DPLL to 1111, no luck. Using stock firmware and UFL cables. Am I forgetting something?

If you can delay the B3 reset by 2-3 seconds I’d expect success.

Last edited:

Thanks for your suggestion Frank. I disconnected power to the DAC until a few seconds after the Cronus was powered. No dice, same thing.

I give up and go back to async. I will post a pic of my setup. Maybe someone here will notice something not right.

I give up and go back to async. I will post a pic of my setup. Maybe someone here will notice something not right.

My next suggestion is to check the MCLK output. Got a fast scope?Thanks for your suggestion Frank. I disconnected power to the DAC until a few seconds after the Cronus was powered. No dice, same thing.

I give up and go back to async. I will post a pic of my setup. Maybe someone here will notice something not right.

Hi,Tried sync mode with my BBB/Hermes/Cronus setup today. Been using async for years and has been working great. Reading back in this forum it seemed to be a simple matter of connecting Cronus master clock output to Buffalo and removing power supply to the Buffalo clock. Didn't work for me at all, just got silence. Changed DPLL to 1111, no luck. Using stock firmware and UFL cables. Am I forgetting something?

think you need firmware chip with "true sync" firmware?

Branko

My problem with Sync mode turned out to be software related. GentooPlayer worked fine in Async but not at all using Sync mode. The Pure DSD driver that has been mentioned here works great though. HQPlayer converting PCM to DSD256 sounds fantastic!

Hi,Hello Andrea, true/pure sync (no DPLL) firmware is not a new official firmware version, but a beta version that Russ released some time ago to test 128fs mode.

You can find firmware link in post #506 and instructions scattered along the following posts. Pure sync mode is active at start, if you properly position n. 1 dip switch in first group, as explained in post 506.

To program the ATTiny85 chip needed you can use a simple programmer, like the one linked in post #516. Total expense for the mod (including programmer) is just a few euros.

Even if totally noob about chip programming and I2C, i tried and succeded replacing normal firmware with pure sync one. Sound is slightly better IMHO, but incredible improvements are not to be expected as normal sync mode is already very good in this dac. Async mode is good but in a lower league than sync mode IMHO, when a decent master clock/reclock/FIFO setup is used. As Frank said, in any sync mode onboard oscillator has to be disabled by removing its trident (or different) power supply and a master clock has to be provided.

I had a problem with 128fs mode, about annoying pops in case of files frequency changing. Some other user had it too, many didn't. So i switched back to normal sync firmware.

My personal additional suggestion is to take care to implement a first order LP filter at around 32/33 khz, somewhere on output (obviously after I/V and possibly first O/S preamplification), as for any sabre dac. But this is only an "unofficial" tip...

Given your musical tastes, a tubes or high permeability/nanocrystalline core transformers I/V output stage should be considered, too.

I am now uncertain what is right for true sync mode:

Do I need the firmware Version mentioned in Post #506 of this thread? Or does it work with standard firmware chip? And then how to enable it? Did the firmware changed with newer send versions of the B3pro? How to check firmware version?

Regards

Branko

I just did it and it’s working fine with standard firmware. The special sync mode firmware may offer some improvement. Maybe someone here can enlighten us about the difference.Hi,

I am now uncertain what is right for true sync mode:

Do I need the firmware Version mentioned in Post #506 of this thread? Or does it work with standard firmware chip? And then how to enable it? Did the firmware changed with newer send versions of the B3pro? How to check firmware version?

Regards

Branko

Disclaimer - I'm not a digital signal processing engineer, nor an engineer at all! So I welcome corrections/clarifications.Hi,

I am now uncertain what is right for true sync mode:

Do I need the firmware Version mentioned in Post #506 of this thread? Or does it work with standard firmware chip? And then how to enable it? Did the firmware changed with newer send versions of the B3pro? How to check firmware version?

Regards

Branko

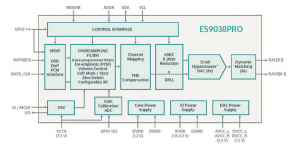

Yes, it is a bit confusing but the ESS Pro data sheets help to better understand the role played by the DPLL. First, look at the the dac's block diagram attached below. The raw data enter from the left side and are subjected to various types of tweaking (like deemphasis, slow/fast FIR filters, etc.). The last preparatory step (from left to right) before rendering the analog stream is the anti-jitter function carried out with help of the DPLL, which is driven by whatever clock the DAC is using. It basically moves early or late frames of data by small increments of time. The B3 onboard clock is 100MHz, which is fast, so those incremental time corrections can be pretty small, but still the data timing is usually just 'very close' rather than 'dead-on'. What if you just change the master clock frequency so that it is an integral multiple of the data sample rate (whether 128, 64, or whatever)? Then the jitter reduction function can more exactly meter the data 'time domain' into the analog converter block. It is actually pretty easy to hear the difference between the onboard vs. external master clocks from Cronus with the DPLL running. So that's what you are doing when you just hook up a Cronus MCLK to the B3 and pull the on board clock trident.

Now, 128_Fs mode (as is used in the true-sync firmware) is controlled by register 10, and 128_Fs mode DOES fully bypass the ASRC. Is this good? If you have very clean incoming data, perhaps so. If you are using jittery Toslink SPDIF out of your video equipment, perhaps that will sound worse with 128_Fs than leaving the jitter eliminator running. I have experimented with 128_Fs and I really don't hear a consistent difference compared to running the DPLL at the narrowest setting. [My PCM is pretty clean so it sounds good at the narrowest DPLL bandwidth regardless of the master clock source.] Therefore I leave the ASRC running from the Cronus clocks, which is also what happens when you use stock B3 firmware. So for my own system, the priority for using "True sync" 128_Fs processing comes into play only near the end of the "system improvement wish-list".

Frank

Attachments

HI,

thank you for these explanations.

Only to be sure: for true sync with stock firmware chip there is no need for any "special" setting (i.e. dpll "off").

I just remove the clock trident and connect the mck from cronus?

thx

Branko

thank you for these explanations.

Only to be sure: for true sync with stock firmware chip there is no need for any "special" setting (i.e. dpll "off").

I just remove the clock trident and connect the mck from cronus?

thx

Branko

Greetings Branko,HI,

thank you for these explanations.

Only to be sure: for true sync with stock firmware chip there is no need for any "special" setting (i.e. dpll "off").

I just remove the clock trident and connect the mck from cronus?

thx

Branko

To answer your question, the 'true-sync" firmware that incorporates 128_Fs mode in the DAC IS technically different from the stock firmware. However, it may or may not sound better in every system. I suggest that you try the stock firmware with the external (Cronus?) master clock and then adjust the DPLL for the best sound. If you find that you can run the stock firmware cleanly at or near the lowest DPLL bandwidth setting (note post #1124) then probably the true-sync firmware, which turns the DPLL OFF, will also be satisfactory. I believe that the DPLL switch positions play no function with PCM in the true-sync firmware but I don't know what is going on with DSD. Perhaps put the two types of firmware on different chips for easier comparison of the sound and performance?

Enjoy the tweaking!

Frank

PS - it is winter - to avoid damaging ESD, always touch a ground before touching the DAC.

Last edited:

Here is a brief update on the question of "true sync" and DPLL bandwidth. My PCM signal is very clean and I've been tweaking the DAC using I2C and listening using both of my Buffalo3Pro systems (but no measurements). Driving loudspeakers I am getting reliably better (and enjoyable!) soundstage with:

register 0x0a - 0x10 - enable 128*FSR mode

register 0x0c - 0x0f - turn DPLL OFF for PCM (rarely using DSD so bandwidth is left wide open JIC)

register 0x0d - 0x30 - dither ON, THD modulation OFF, jitter eliminator ON

Unfortunately, I don't know which controls would give you these settings with the 'true sync' code onboard.

register 0x0a - 0x10 - enable 128*FSR mode

register 0x0c - 0x0f - turn DPLL OFF for PCM (rarely using DSD so bandwidth is left wide open JIC)

register 0x0d - 0x30 - dither ON, THD modulation OFF, jitter eliminator ON

Unfortunately, I don't know which controls would give you these settings with the 'true sync' code onboard.

What is the master clock when using this settings, the 100 MHz or the Cronus clocks? In other words, does te MCLK have to match the sample rate for this mode?Here is a brief update on the question of "true sync" and DPLL bandwidth. My PCM signal is very clean and I've been tweaking the DAC using I2C and listening using both of my Buffalo3Pro systems (but no measurements). Driving loudspeakers I am getting reliably better (and enjoyable!) soundstage with:

register 0x0a - 0x10 - enable 128*FSR mode

register 0x0c - 0x0f - turn DPLL OFF for PCM (rarely using DSD so bandwidth is left wide open JIC)

register 0x0d - 0x30 - dither ON, THD modulation OFF, jitter eliminator ON

Unfortunately, I don't know which controls would give you these settings with the 'true sync' code onboard.

- Home

- More Vendors...

- Twisted Pear

- Introducing the Buffalo III-SE-Pro 9028/9038