just use some I/O to be delta sigma output or discrete FF (like a CHORD 😀)

After that, the signal directly come to analog filter.

I think use FPGA, we can provide balance signal with dc offset

Which of the two do you use: just an FPGA I/O or an extra flip-flop? With an extra flip-flop, you basically use the flip-flop rather than the FPGA as the DAC, and you have much more opportunity to limit crosstalk.

I don't quite understand your last sentence. Do you mean you generate a balanced output signal and then convert to single-ended (if needed at all) after the analogue reconstruction filter? Using balanced outputs and return-to-zero coding can much reduce the data dependence of the current that you draw from the reference supply.

Clocking Hell.

Err I mean each of those three FPGAs will have it's own master clock and you need a sync clock.. and the bit stream clock.

I thought the easiest way was to run a set of shift registers and then sync the switching as one. They would be cheaper than using an FPGA for the same role - that way you only need one. Which is pretty much what most of the FPGA R2R DACs do.

Which of the two do you use: just an FPGA I/O or an extra flip-flop? With an extra flip-flop, you basically use the flip-flop rather than the FPGA as the DAC, and you have much more opportunity to limit crosstalk.

I don't quite understand your last sentence. Do you mean you generate a balanced output signal and then convert to single-ended (if needed at all) after the analogue reconstruction filter? Using balanced outputs and return-to-zero coding can much reduce the data dependence of the current that you draw from the reference supply.

This design I only use FPGA, as per CHORD, they use FF NC7SZ175 😀.

DS out is 0 or 3V, so DC offset is a half.

So each channel, output will have 2 signals.

You can see my draft for more detail.

* I draw too bad ...

Attachments

High quality Raspberry Pi I2S HAT - part 1 - overviewInput is I2S, how it can be master? can you talk more about it? 🙂

I think 2nd is the best. Re-clocking from any lower to high freq will cause terrible noise, jitter... clock will bad.

😀 I understand your design.

It's ok

But when master (DAC) call for data from slave (RPi), at this time is between 2 samples, which sample will choose? I think It will still loose sample.

This is same as event or push in USB Audio

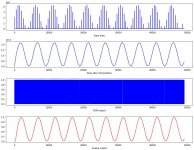

Simulation of interpolation and DS DAC by Python

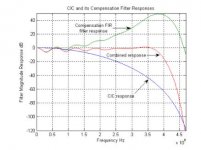

It looks like you use linear interpolation. If that's true, then how do you compensate for the sinc^2 roll-off? It's quite substantial at low sample rates, for example -6.3356 dB at 20 kHz at 44.1 kHz sample rate.

Clocking Hell.

Err I mean each of those three FPGAs will have it's own master clock and you need a sync clock.. and the bit stream clock......

There aren't three FPGAs on that board. There are two CPLDs and one FPGA. The two CPLDs do not have the resources to do much more than replicate the role of the HC595s.

It looks like you use linear interpolation. If that's true, then how do you compensate for the sinc^2 roll-off? It's quite substantial at low sample rates, for example -6.3356 dB at 20 kHz at 44.1 kHz sample rate.

you're right.

you're right.In my project, CIC interpolation need add FIR compensation

Attachments

Last edited:

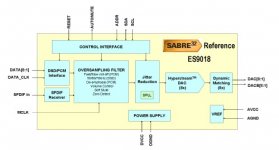

The cost of each FPGA is quite high, at least US$100, or even US$300. In addition, the noise of the FPGA itself is higher than that of the DAC chip. The DAC HAT of iancanada using ES9028Q2M is only $49.00. In other words, if your FPGA-based DAC is not as good as ES9028Q2M, even if everyone wants to sponsor you, I am afraid there is no way.

Euro 14.89 at Farnell, not sure if it is with or without VAT:

https://nl.farnell.com/xilinx/xc6slx9-2tqg144c/fpga-spartan-6-102-i-o-tqfp-144/dp/2763358?st=xc6slx9

https://nl.farnell.com/xilinx/xc6slx9-2tqg144c/fpga-spartan-6-102-i-o-tqfp-144/dp/2763358?st=xc6slx9

There aren't three FPGAs on that board. There are two CPLDs and one FPGA. The two CPLDs do not have the resources to do much more than replicate the role of the HC595s.

The CPLDs I've seen have been titchy compared those. You can do PWM for example at very quick rates using a CLPD, but as you've said they're very limited without ADC or internal resources.

The cost of each FPGA is quite high, at least US$100, or even US$300. In addition, the noise of the FPGA itself is higher than that of the DAC chip. The DAC HAT of iancanada using ES9028Q2M is only $49.00. In other words, if your FPGA-based DAC is not as good as ES9028Q2M, even if everyone wants to sponsor you, I am afraid there is no way.

😀 not expensive as you think

Based on fpga that you choose and quantity you buy

Euro 14.89 at Farnell, not sure if it is with or without VAT:

https://nl.farnell.com/xilinx/xc6slx9-2tqg144c/fpga-spartan-6-102-i-o-tqfp-144/dp/2763358?st=xc6slx9

the price is reasonable because a FPGA is very flexible and multi-purpose ... We can update, add more function ...

the price is reasonable because a FPGA is very flexible and multi-purpose ... We can update, add more function ...😀 not expensive as you think

Based on fpga that you choose and quantity you buy

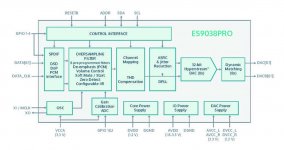

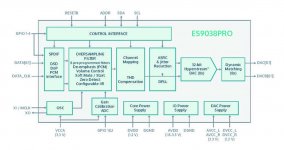

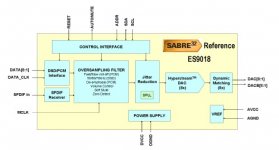

ESS 9038Pro is already a very powerful DAC chip. If you use a cheap version of FPGA to implement the DAC, I would not expect yours to be better than the DAC chip. Chord DAVE uses the LX75 version of the Spartan 6 FPGA and three more.

https://www.newark.com/xilinx/xc6slx75t-2fgg484i/fpga-spartan-6-268-i-o-fbga-484/dp/32AC9780

Iancanada's the reclock module uses Altera Cyclone IV. So if you want to implement a much more complex DAC, you can only use a larger and more advanced FPGA, right?

Last edited:

@yunyun

There are many DACs, amps, speakers...already made, so what's the reason for diyAudio and other comunities, let's close them.

There are many DACs, amps, speakers...already made, so what's the reason for diyAudio and other comunities, let's close them.

ESS 9038Pro is already a very powerful DAC chip. If you use a cheap version of FPGA to implement the DAC, I would not expect yours to be better than the DAC chip. Chord DAVE uses the LX75 version of the Spartan 6 FPGA and three more.

https://www.newark.com/xilinx/xc6slx75t-2fgg484i/fpga-spartan-6-268-i-o-fbga-484/dp/32AC9780

Iancanada's the reclock module uses Altera Cyclone IV. So if you want to implement a much more complex DAC, you can only use a larger and more advanced FPGA, right?

ha ha ha ha, About FPGA, We never know how much resource has used. Large FPGA is not meaning if We not use all... Small FPGA is not simple DAC. It is based on algorithm.

@yunyun

There are many DACs, amps, speakers...already made, so what's the reason for diyAudio and other comunities, let's close them.

Just DIY project. Let's have fun

I'm printing a chassis for our project, let's wait...

According to the BLOCK DIAGRAM of 9038PRO and 9018, it can be easily seen that in order to achieve better sound quality, a larger FPGA or even more FPGAs are needed to accommodate more complex logic units.

In other words, if your FPGA-based DAC only uses a relatively small FPGA, it is not difficult to know that you do not intend to design the performance to be stronger than the existing DAC chip. In other words, it's just for fun, not to get better sound quality.

In other words, if your FPGA-based DAC only uses a relatively small FPGA, it is not difficult to know that you do not intend to design the performance to be stronger than the existing DAC chip. In other words, it's just for fun, not to get better sound quality.

Last edited:

@yunyun

There are many DACs, amps, speakers...already made, so what's the reason for diyAudio and other comunities, let's close them.

Even for fun, Diyer will still consider the benefits, which is why ACKO has withdrawn from the supply of reclock modules, because he can’t keep up with iancanada’s reclock modules at all.

@yunyun

There are many DACs, amps, speakers...already made, so what's the reason for diyAudio and other comunities, let's close them.

Many years ago, I actually spent money to compare ACKO and iancanada modules. In the end, I convinced ACKO with theory that his module was totally unsuccessful. ACKO asked me to pay him some fees and let him continue to develop. However, why should I do this? Isn't it more in my interest to buy the iancan module directly?

I'm sure a very basic FPGA-based DAC can't compete with the highest SINAD DAC chips on the market when the only thing you care about is how many dB's of SINAD you get per dollar, but then again, what difference does it make whether the noise is 10 dB or 100 dB below audibility under normal listening conditions?

Regarding benefits, XC6SLX9 FPGAs have many:

-They are relatively cheap

-You can still hand solder them, unlike the bigger ones that are all in ball grid array packages

-As with any FPGA, you can tweak the configuration file, so instead of tube or op-amp rolling, you can do configuration file rolling

Regarding benefits, XC6SLX9 FPGAs have many:

-They are relatively cheap

-You can still hand solder them, unlike the bigger ones that are all in ball grid array packages

-As with any FPGA, you can tweak the configuration file, so instead of tube or op-amp rolling, you can do configuration file rolling

- Home

- Source & Line

- Digital Line Level

- FPGA-based delta sigma DAC