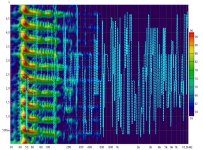

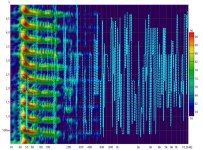

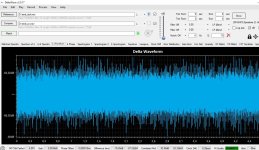

Perhaps. This is what I recieved on recordings with 24Mhz xtal and xo on XMOS in SMSL, it uses external clock to generate audio signals and external clock for DAC. Difference in peak energy time, predominantly after 2KHz and up.

Attachments

Pointless to post measurements without details about the measurement setup.

If you truly believe your ADC is capable of measuring differences of crystal vs. clock then just make 2 recordings and compare them with DeltaWave.

If you truly believe your ADC is capable of measuring differences of crystal vs. clock then just make 2 recordings and compare them with DeltaWave.

No.But XMOS uses this 26Mhz xtal as main clock for itself and also in the end in order to generate audio signal, does not it ?

The XCore CPU uses so-called "serialized ports", in simple terms - each 1-bit port is a shift register, where the port pin is its output. The CPU only writes data to this register, and the shift is provided by an external clock that has no relation to the CPU clock.

Alex.

Okay, but no/zero/none substrate coupled noise from other clock edges? Unlikely there is exactly zero added phase noise in the shift register output. Whether there is enough to have an audible effect to some but not all humans would be another question (where "to some but not all humans" refers to effects down around the thresholds).The CPU only writes data to this register, and the shift is provided by an external clock that has no relation to the CPU clock.

BTW, I'm not trying to argue @Anatolii_A is right, only asking if you are sure your model of how it works could possibly be a little simplified from the actual hardware?

Last edited:

Okay, but no/zero/none substrate coupled noise from other clock edges?

Who care?

It was mentioned many times - most DAC chips are sensitive just to MCLK's jitter.

For using with ancient DAC chips, use D-type Flip-Flop, clocked from good MCLK (for WCLK, BCLK or both).

Alex.

It appears that @Anatolii_A cares. If he says he hears an effect from changing a clock not directly involved in sending I2S bus data, then how can you be absolutely sure he must be hallucinating? I mean, maybe he does hear some small effect because his dac is not well designed?Who care?

In the case above I am only arguing that: what someone else says they hear when you are not there to see for yourself seems to me more like an opinion about what is likely, rather than something to have absolute certainty about.

Last edited:

This is still about clock jitter, not clock noise. How would clock jitter have an impact on alleged substrate coupled noise?but no/zero/none substrate coupled noise from other clock edges?

It is not about being absolutely sure but which is more likely. Especially when no controls are in place.If he says he hears an effect from changing a clock not directly involved in sending I2S bus data, then how can you be absolutely sure he must be hallucinating?

IMHO, jitter is a type of noise. It is an unwanted signal, which by some definitions is noise.

More specifically, clock noise is from very high frequency edge components. When those edges are jittered in time, and because the VHF edge components can couple well to the substrate because Xc is small at VHF, then a time-varying noise signal could be coupled to the shift register enough to slightly affect its timing. Its a type of effect documented to occur in high speed digital ICs.

More specifically, clock noise is from very high frequency edge components. When those edges are jittered in time, and because the VHF edge components can couple well to the substrate because Xc is small at VHF, then a time-varying noise signal could be coupled to the shift register enough to slightly affect its timing. Its a type of effect documented to occur in high speed digital ICs.

Last edited:

I wrote upper about ADC. Really it does not matter, because I search the delta difference between recordings with the same recorder. Which data from DeltaWave I need to screen ?Pointless to post measurements without details about the measurement setup.

If you truly believe your ADC is capable of measuring differences of crystal vs. clock then just make 2 recordings and compare them with DeltaWave.

Of cource I speak about usual not expencive devices, exactly now about xtal near XMOS in SMSL DAC (perhaps many others but I don't know about >200USD segment they put here).I mean, maybe he does hear some small effect because his dac is not well designed?

.

If you have direct DAC-to-ADC recordings (wav-files), you can post those with the original. But you should create a new thread for these as this thread is not about your clock swappings.Which data from DeltaWave I need to screen ?

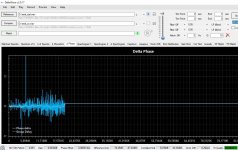

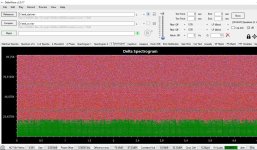

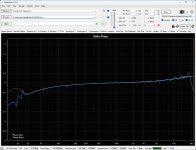

I suppose that I can help with improving device in start post, so let it be one more post about clock swapping here. So, we have one measurement instrument. It is WM8782S + SA9227 with NDK clocks, both with linear supply, we don't care about it specs because we search the difference between recordings at its inputs. As I said, the main difference in sound stage, and this wonderfull tool Delta Wave shows it. It is all about phase characteristic of sound, that's why it doesn't belong to SINAD measurements. So here a screens between difference in measurements (in real life it much better, after recording with this setup it is worse). XU316 XMOS with 24MHz xtal and xo in SMSL DAC with external MCLK. The DAC is already upgraded, with good linear power supplies.

Attachments

Last edited:

about phase ? If you want you can make such a recording and jugement and hear by yourself, it is not difficult. It tells very muchdo not tell much.

you can made it byself, just swipe xtal on XMOS board and record it.Can you post both recordings together with the original.

Your recordings seem to be very short and there are odd spikes in delta phase. So just to double check can you make 60s recordings and post them.

- Home

- Source & Line

- Digital Line Level

- Audiolab Q-DAC