Yes. I initially modeled it with LSK489A with standing current below the lowest possible Idss, and 3k9 was the optimal value of load resistors for it. I did not update them after replacing the input device with JFE2140 and increasing the current to ~4mA per side.

Thank you for your detailed analysis, Marcel.

So it would seem that changing the way I connect them ... is not really going to affect the resulting capacitance load on the cart much?

Not much, just a little.

BTW, if by "each JFET is biased at about 2 mA of drain current", you mean the current which is flowing through each jfet, from Drain to Source - I have this at about 4.8ma (75% of Idss).

If they draw 9.6 mA together, then the voltage drop across the 46 ohm source resistor must be about 0.44 V.

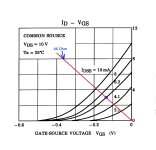

At -0.44 V gate-source voltage, the current is far below 4.8 mA according to this Toshiba graph, at least at 10 V drain-source voltage.

If they draw 9.6 mA together, then the voltage drop across the 46 ohm source resistor must be about 0.44 V.

At -0.44 V gate-source voltage, the current is far below 4.8 mA according to this Toshiba graph, at least at 10 V drain-source voltage.

The value of 46 ohm is what I need for R4 in the LTspice sim.

In 'real life' - ie. actually measuring the built circuit - the value of R4 is 4R4 and the Source voltage I get ... leads to a combined current of about 9.6ma. Drain-Source voltage is about 8v.

With 4.4 ohm and about 30 mS per FET (transconductance at 4.8 mA from a Toshiba datasheet graph), only 20.886 % of the input AC voltage will drop across the resistor, so you can only get about 20 % of capacitance reduction. The remaining capacitance is then 48 pF when you connect C3 to the resistor, 50.4 pF when you don't.

This seems to work.

I had to introduce compensation to make it stable.

AC analysis shows a 2dB peak at 3.2MHz. It's a good thing that there will be a passive low-pass filter implementing the 75us RIAA pole after this stage.

I had to introduce compensation to make it stable.

AC analysis shows a 2dB peak at 3.2MHz. It's a good thing that there will be a passive low-pass filter implementing the 75us RIAA pole after this stage.

With 4.4 ohm and about 30 mS per FET (transconductance at 4.8 mA from a Toshiba datasheet graph), only 20.886 % of the input AC voltage will drop across the resistor, so you can only get about 20 % of capacitance reduction. The remaining capacitance is then 48 pF when you connect C3 to the resistor, 50.4 pF when you don't.

Thanks, Marcel. 👍

So ... not really worth doing. 🙁

But I'm confused by sk's post here:

But if you tie the base (or the gate) of the upper device to the source of the lower device, you’re preventing any voltage variation from developing between the drain and the source of the input device(s), which not only mitigates the Miller effect, but also effectively eliminates the capacitance of the input device altogether.

How can I do what he says ... ie. "eliminate the capacitance of the input device altogether"? What change in my circuit do I need to make, to achieve this?

There are two in parallel, so you should draw a 92 ohm loadline to find the current per JFET. Hence my estimate of 2 mA for an average IDSS.

Thanks, Marcel. 👍

So ... not really worth doing. 🙁

But I'm confused by sk's post here:

How can I do what he says ... ie. "eliminate the capacitance of the input device altogether"? What change in my circuit do I need to make, to achieve this?

stratokaster83 assumes perfect voltage follower behaviour from gate to source. You cannot completely achieve that, but you could get a lot closer by replacing the FETs with some multistage negative feedback circuit (for example a Sziklai pair with a JFET as its first stage and a current source or resistor for biasing it) or by using a much larger source resistor - which would reduce the transconductance, which is unacceptable according to one of your earlier posts.

Thanks again, Marcel.

What you suggest (as a 'solution' to the issue of Ciss) is too complicated; so I will just stay with what I have.

What you suggest (as a 'solution' to the issue of Ciss) is too complicated; so I will just stay with what I have.

Try connecting a 3.9kΩ + 24pF (R and C series circuit) in parallel to the feedback resistor R7.AC analysis shows a 2dB peak at 3.2MHz.

Wouldn't this result in a straightforward (like a first-order LPF) characteristic with almost no peaks?

Thanks Mason.

Now, let's see if I can calculate a Sallen-Key high pass filter without any major brain farts.

This is going to be the infrasonic filter using both halves of a dual opamp for one channel:

The goal was to have a steep attenuation with as little intrusion at 30Hz and above as possible. (Yes, I like organ music, but even LPs with organ music rarely have anything useful below 30Hz.)

-16dB at 10Hz, - 24dB at 8Hz and at least -43dB in the region which contains the worst warp frequencies (0.55Hz to 4.4 Hz).

Now, let's see if I can calculate a Sallen-Key high pass filter without any major brain farts.

This is going to be the infrasonic filter using both halves of a dual opamp for one channel:

The goal was to have a steep attenuation with as little intrusion at 30Hz and above as possible. (Yes, I like organ music, but even LPs with organ music rarely have anything useful below 30Hz.)

-16dB at 10Hz, - 24dB at 8Hz and at least -43dB in the region which contains the worst warp frequencies (0.55Hz to 4.4 Hz).

The whole phono preamplifier would look something like this (sorry for the slightly messy schematic):

It seems that the value of R2 was lowered to increase the current flowing to the LEDs in the first stage, but this resistor is equivalently in parallel with the operating resistance of the lower constant current circuit, so a too low value would make the constant current circuit composed of Q2 etc. meaningless.

The value of R2 should be rather high. If you are concerned that this increases the operating resistance of the LEDs, you can also parallel C to the LEDs.

Actually, I also use a JFET LTP + OP-AMP configuration in a single-stage phono amplifier.

In my circuit also use JFETs for the cascode bootstrap, and I like the simplicity of the circuit as it only requires the addition of two JFETs.

Circuit attached to this post

This FET is suitable for the lower side LTP FETs to operate in the constant current region, so FET with a large Idss (large absolute pinch-off voltage) is suitable. I use 2SK125s as I had many of them, but they are obsolete.

Although they are SMDs, MMBFJ310 or MMBF4391 are good candidates for replacement and are inexpensive.

For reference...

The value of R2 should be rather high. If you are concerned that this increases the operating resistance of the LEDs, you can also parallel C to the LEDs.

Actually, I also use a JFET LTP + OP-AMP configuration in a single-stage phono amplifier.

In my circuit also use JFETs for the cascode bootstrap, and I like the simplicity of the circuit as it only requires the addition of two JFETs.

Circuit attached to this post

This FET is suitable for the lower side LTP FETs to operate in the constant current region, so FET with a large Idss (large absolute pinch-off voltage) is suitable. I use 2SK125s as I had many of them, but they are obsolete.

Although they are SMDs, MMBFJ310 or MMBF4391 are good candidates for replacement and are inexpensive.

For reference...

I doubt that it is very critical because common-mode current is cancelled by the second stage, but you could use a current source instead of R2 to keep the tail impedance high.

Yes, that was indeed the thinking. Putting a capacitor across the LEDs seems to be a good idea.It seems that the value of R2 was lowered to increase the current flowing to the LEDs in the first stage, but this resistor is equivalently in parallel with the operating resistance of the lower constant current circuit, so a too low value would make the constant current circuit composed of Q2 etc. meaningless.

The value of R2 should be rather high. If you are concerned that this increases the operating resistance of the LEDs, you can also parallel C to the LEDs.

It is time to think about phono cartridge termination. I must say that after playing with PhonoLCR, I am now a firm believer in unconventional loading as championed by @Nick Sukhov. While installing a phono stage inside my turntable would not be practical, I can put it right under the turntable and use a short phono cable, which would give me a total cable capacitance of approximately 60pF (wiring inside the tonearm + 45cm of Mogami 2330 cable + capacitance of various connectors, etc.). Assuming total capacitance of 100pF or less, resistive loads between 68kOhm and 100kOhm seem to give the best frequency response and the least amount of peaking compared to conventional loading (47kOhm + 150-300pF), at least for my cartridges.

Last edited:

Preliminary schematic before I start redrawing it in KiCAD and laying out the PCB.

Some cartridges have a substantial mechanical resonance while others have not. They all have iron losses, but some more than others.

I never heard of PhonoLCR, but if it models the loaded cartridge with just two ideal resistors, an ideal inductance, an ideal capacitance and a voltage source, it is bound to be very inaccurate. @Hans Polak has done quite some work on more accurate cartridge modelling.

I never heard of PhonoLCR, but if it models the loaded cartridge with just two ideal resistors, an ideal inductance, an ideal capacitance and a voltage source, it is bound to be very inaccurate. @Hans Polak has done quite some work on more accurate cartridge modelling.

- Home

- Source & Line

- Analogue Source

- 2-stage split gain phono preamp with passive-active RIAA