I haven't RS232 port on my PC so I'm using the one coming from the factory.

There's was USB adapter posted in this thread a few pages ago. I bought it, works great.

The dam1021 is easier to DIY, the dam1121 is intended for OEMs (but also sold to consumers in single quantities) and requires a bit more tinkering.

TOTL dam1021 vs TOTL dam1121:

oscillator: Si514 vs. Si570

typical jitter: 0,8 vs. 0,3 ps

reclocking: before FPGA vs. after FPGA

galvanic isolation on input: yes vs. no

THD @ -1 dB: <0,007 vs. <0,006%

S/N 20 Hz - 20 kHz: 127 vs. 129 dB unweighted

buffered output: yes vs. no

interface header pitch: 2,54 mm vs. 2 mm

power supply: on-board (single feed 7-8VAC or +/-7-15VDC) vs. requires external (separate digital +5VDC and analog +/- 5VDC)

Also agreed that using custom filters really makes it sing. Many people here have been cooking up amazing things here:

Filter brewing for the Soekris R2R

Saving you the trouble of reading through 209 pages I recommend either of the following packs:

DIYA_1021filt_noDCmode.skr : TNT's linear filter (2K taps) + EQHQ_lpbr_b4 + C128dp + NewNOS (without DC filter)

oneoclock's pack : as above but with Soekris' stock linear filter (4K taps)

I'm loving C128dp but it's not for everyone. The other filters are really good too except NewNOS in my opinion. The latter can have a distorted midrange with too much grain.

Well, it looks like there is not much difference at all.

I bought the DAM1021 because it was the most pointed out in the thread so I have thought it was the most used from DIY users.

At the end I got the DAM1021 in order to make a few measurements and to tweak it following my architecture approach.

Practically I'm working on the DAM1021 for the diy audio community, since as you know we are designing our FIFOs/DACs.

There's was USB adapter posted in this thread a few pages ago. I bought it, works great.

I will get the adapter later, now I'm busy working on our new designs.

Anyway after a few hours of listening and comparison I already have an idea of the performance.

You can also use the serial port on a Raspberry Pi, off of the GPIO header.

to install other filter packages on the 1021? ?

Sure. Tx is on header pin 8 and Rx is on header pin 10.

Using raspi-config, disable the serial login shell and enable the serial port. You're now good to go on /dev/serial0. I like to use this Python-based command line interface: GitHub - fortaa/dam1021: Python inferface for the dam1021 DAC

For direct terminal access I use screen; "apt-get install screen" and then "screen /dev/serial0 115200"

This works out-of-the-box on a RPi 3B+. Different RPi versions use different serial configurations, please read UART configuration - Raspberry Pi Documentation

Only caveat is that the dam and RPi must share the same power supply and ground reference, otherwise the serial communication won't work. (So if you have an isolator board then temporarily take it out.)

Using raspi-config, disable the serial login shell and enable the serial port. You're now good to go on /dev/serial0. I like to use this Python-based command line interface: GitHub - fortaa/dam1021: Python inferface for the dam1021 DAC

For direct terminal access I use screen; "apt-get install screen" and then "screen /dev/serial0 115200"

This works out-of-the-box on a RPi 3B+. Different RPi versions use different serial configurations, please read UART configuration - Raspberry Pi Documentation

Only caveat is that the dam and RPi must share the same power supply and ground reference, otherwise the serial communication won't work. (So if you have an isolator board then temporarily take it out.)

gumisb just made some new FIR filters, see post in filter brewing thread.

Last edited:

@andrea_mori also I agree with the time and money you already spent on the project, you'd be cutting yourself short if you didn't take the extra mile with better filters. The differences are clearly audible.

I will give a try with different filters later, but keep in mind that with my upgrade there is no way to add filters, our FIFO Lite does not provide filters option, oversampling has to be made externally (if needed).

So you can no longer run the DAM1021 at 3MHz.

Andrea's hypothesis is that the DAM1021 is so bad he even bought one to prove it by all means.... and that he can do a much better job. To be clear, I have little doubt he can... as many others out here. It is always easier to improve something existing and certainly to criticize someone else's work.

Funny thing he speaks regularly about 'we', as if there is an organisation or group behind him, doing all this purely for hobby. Don't get it, but don't care.

Funny thing he speaks regularly about 'we', as if there is an organisation or group behind him, doing all this purely for hobby. Don't get it, but don't care.

Last edited:

You activities around 1021 are they just experiments in general to learn something or do you have a hypothesis that you would like to prove? If so, what is this hypothesis? It was never clear to me.

//

I thought it was clear, I wrote several times that I don't agree about the design choices of the DAM1021's front end.

IMHO there is a better way to feed the DAC so our upgrade follows our different approach (the FIFO Lite).

I will also measure the phase noise and the ladder accuracy of the DAM before and after the upgrade, since we trust more in this kind of measurements rather than the THD.

Finally we will compare the sound performance of both versions of the DAM1021 (original from factory and and upgraded with our FIFO Lite).

We will arrange a blind listening session with one of my reference system

Tda1541A DAC + 845 tube amp + open baffle: the quasi-eastern way to hi-end

Andrea's hypothesis is that the DAM1021 is so bad he even bought one to prove it by all means.... and that he can do a much better job. To be clear, I have little doubt he can... as many others out here. It is always easier to improve something existing and certainly to criticize someone else's work.

Funny thing he speaks regularly about 'we', as if there is an organisation or group behind him, doing all this purely for hobby. Don't get it, but don't care.

Firstly, I have nothing to demonstrate, if you are satisfied with your DAM1021 you can ignore my posts and live happy.

Evidently you are not one of the members that claims the issue replacing the source and for your taste the DAM is not source dependent.

I'm not citicizing nothing, simply in my technical opinion there is a better way to feed a DAC.

You don't agree, you think the DAM is perfect as is.

Well, I repect your opinion but I disagree, then you can disagree but you should respect my opinion.

Finally, I speak regularly about 'we' because it means me and my co-developer Roberto.

We are audio hobbyist, we like to design and build state of the art audio devices.

And so far we are succeeding.

Curious andrea, given that you are very much into clocking and reclocking, why do you say there is little difference between reclocking before the FPGA (dam1021) and after the FPGA (dam1121)?

Because in my honest opinion the problem is not related to the reclocking.

There is no reclocking in our FIFO Lite, we have implemented a totally different approach.

In our FIFO the time domains before and after the FIFO are fully isolated, the LRCK does not come from the FPGA, it comes directly from the master clock that operates in a separate domain and the FIFO buffer is slaved to this clock.

1/Firstly, I have nothing to demonstrate, .....

2/ You don't agree, you think the DAM is perfect as is.

3/And so far we are succeeding.

1/ Com'on Andrea! All your pages of bashing/complaining/repeating yourself endlessly and even buying one and starting your improvement board before even listening to it as it is, suggest otherwise...

2/ Never said that, it does need some tweaking to be very good for the investment made, no problem with that and that is my opinion.

3/ Good for you, don't forget to live happy ;-)

That does sound good. I was under the assumption reclocking after the FPGA did the same thing. In my case:

RPi PLL rubbish -> galvanic I2S isolator -> dam1121 into FPGA

...FPGA does FIFO buffering...

...FPGA slaved to Si570 *after* the FPGA emitting clean source.

Part of the DIY fun is learning by reading so where am I going wrong here?

RPi PLL rubbish -> galvanic I2S isolator -> dam1121 into FPGA

...FPGA does FIFO buffering...

...FPGA slaved to Si570 *after* the FPGA emitting clean source.

Part of the DIY fun is learning by reading so where am I going wrong here?

1/ Com'on Andrea! All your pages of bashing/complaining/repeating yourself endlessly and even buying one and starting your improvement board before even listening to it as it is, suggest otherwise...

2/ Never said that, it does need some tweaking to be very good for the investment made, no problem with that and that is my opinion.

3/ Good for you, don't forget to live happy ;-)

Well:

- I'm free to express my technical opinion on a diy audio forum and I have never insulted anyone

- I'm free to buy whatever I want, mostly a device offered in a diy audio forum and I have have not spent your money

- I'm free to update whatever I want mostly a device offered in a diy audio forum, I'm not updating yours

- You are free to update your DAM in your own way, I have never said you can't, while I'm free to update mine in the way I want

- You are free to disagree with my tecnhical opinion while I'm free to disagree with yours (although I have never read your TECHNICAL opinion)

That does sound good. I was under the assumption reclocking after the FPGA did the same thing. In my case:

RPi PLL rubbish -> galvanic I2S isolator -> dam1121 into FPGA

...FPGA does FIFO buffering...

...FPGA slaved to Si570 *after* the FPGA emitting clean source.

Part of the DIY fun is learning by reading so where am I going wrong here?

IMHO the FPGA does not provide a clean source and I have already said what I think about the Si570.

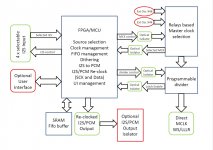

Our approach is a little different, please see the attached picture.

Attachments

I thought it was clear, I wrote several times that I don't agree about the design choices of the DAM1021's front end.

IMHO there is a better way to feed the DAC so our upgrade follows our different approach (the FIFO Lite). ... snip...

So, we can look forward to a redesign of every DAC that you don't think is correctly designed - is that correct? Why just this one?

You say "... is a better way to feed the DAC.." But you are not feeding "the DAC" (Soekris DAC), you are feeding a ladder of resistors... the test will say noting about how a DAM DAC would sound with an other clock / DPLL - sorry, it doesn't work that way.

//

- Home

- Vendor's Bazaar

- Reference DAC Module - Discrete R-2R Sign Magnitude 24 bit 384 KHz