I'm not sure there is value talking about noise levels that low given the LDOs/regulators onboard.

From memory the 3.3v LDO has noise output of 99uV (at min) and 5v reg is 40uV (at min).

If there is a wish to improve things for the FPGA/clock (which are locally decoupled if I remember right), you MUST replace the 3.3v source... then all that needs to happen is bring the ripple at the last cap in the onboard CRC to below 4.4mV (been awhile so hopefully I remember this right) so as not to have a noise value higher than the 40uV of the 5v reg - which is quite easy to achieve with additional filtering on even the stock low voltage transformers when you use a separate 3.3v source.

I've been waiting to try this out - have worked out a trade with a fellow diyaudio member with the SSR03 power supply, but haven't obtained one to verify the above.

Hopefully someone more knowledgeable with power supply mods can chime in. Nigel???

From memory the 3.3v LDO has noise output of 99uV (at min) and 5v reg is 40uV (at min).

If there is a wish to improve things for the FPGA/clock (which are locally decoupled if I remember right), you MUST replace the 3.3v source... then all that needs to happen is bring the ripple at the last cap in the onboard CRC to below 4.4mV (been awhile so hopefully I remember this right) so as not to have a noise value higher than the 40uV of the 5v reg - which is quite easy to achieve with additional filtering on even the stock low voltage transformers when you use a separate 3.3v source.

I've been waiting to try this out - have worked out a trade with a fellow diyaudio member with the SSR03 power supply, but haven't obtained one to verify the above.

Hopefully someone more knowledgeable with power supply mods can chime in. Nigel???

Last edited:

I am a big fan of both Jung super reg and Salas shunt.

Both perform and measure excellently.

Dam1021 sounds great with Salas shunt.

However, we find that putting a pair of 47u Os-con at the output of Salas shunt not only helps to decrease the Noise floor of Dam's output, but 2~3dB lower in 2nd harmonic distortion, i.e. improves THD + N.

Also, the TH+D looks even better without the remote sensing wires.

We believe that there are some tweaks that makes the Salas shunt work best with Dam1021 even though it already sounds great just plug-n-play. (For instance, the 47u pairs should better be put at the power input J1, we think.)

The pair of 47u OS-con do not help much for frequency above 10kHz. That's why my friend suggested me to try some RF linear regulator e.g. ADM7151 and see how does it compare with the Salas shunt, especially in the frequency range near 10kHz.

Both perform and measure excellently.

Dam1021 sounds great with Salas shunt.

However, we find that putting a pair of 47u Os-con at the output of Salas shunt not only helps to decrease the Noise floor of Dam's output, but 2~3dB lower in 2nd harmonic distortion, i.e. improves THD + N.

Also, the TH+D looks even better without the remote sensing wires.

We believe that there are some tweaks that makes the Salas shunt work best with Dam1021 even though it already sounds great just plug-n-play. (For instance, the 47u pairs should better be put at the power input J1, we think.)

The pair of 47u OS-con do not help much for frequency above 10kHz. That's why my friend suggested me to try some RF linear regulator e.g. ADM7151 and see how does it compare with the Salas shunt, especially in the frequency range near 10kHz.

I am using salas shunt with Dam1021 at the moment.

very satisfied.

yet,I doubt that salas shunt can”t cope with high freq requirement of Dam1021.

I will make an IC based regulator for comparison.

just wonder i should use LT1963, tps7a400 or adm7150.

TPS7A4701 is ideal at that voltage range but like said why cant the reg be compatible with the High freq requirement?

If there is a wish to improve things for the FPGA/clock (which are locally decoupled if I remember right), you MUST replace the 3.3v source...

In theory you won't gain much by improving the clock supply...

All Si51x devices include on-chip voltage regulation, which minimizes the impact of system-level power-supply noise on clock jitter and keeps jitter below 1 ps rms even in noisy system environments. This noise immunity is advantageous in FPGA-based systems that rely on tightly regulated switched-mode power supplies. By filtering power-supply noise inside the device, Si51x XO/VCXOs can be mounted next to FPGAs without requiring external low-dropout regulators for power-supply filtering.

In theory you won't gain much by improving the clock supply...

I'm not able to verify independently (i.e. better clock supply versus lower ripple that impacts the 5v reg) - but I tend to respect all your contributions and will take it at face value!

There is definitely a difference when supplying the 3.3V line separately.

Perhaps, as you say the main benefit of supplying the 3.3V line with the ADM7150 is the lower current draw which helps to lower ripple. FWIW, I'm getting good results from a smallish clclc filter (don't have the equipment to verify but ripple at the last PS cap according to psud2 is 0.2mV with a load as high as 360mA)... the voltages are also stable all day (no variations - though it's been awhile since I measured). In a way, my current setup is basically a clclc filter for high-freq stuff combined with the regulators onboard the DAM.

I'm not sure there are details of how the opamps derive the +-4V reference for the R2R ladder from the +-5v line to know how the 40uV noise impacts accuracy there.

When I get some time and obtain that SSR03 I'll hopefully be able to hear if a regulated low-noise supply has any gains (I don't have an AP that arthur has obviously - sigh

Last edited:

Iancanada reports here http://www.diyaudio.com/forums/digi...mate-weapon-fight-jitter-226.html#post3342520 , posts 2258 (more info in 2259) that the SI570 works best with a 3.4V LiFePO4 battery.

It might be worth considering, since so much listening was done on Ian's FIFO project, although clocks and jitter reportedly work differently with R2R and Delta Sigma DACs (i.e. R2R DACs not as susceptible, so may get less milage from improved clock or clock supply) and Ian uses the Sabre DAC...

It might be worth considering, since so much listening was done on Ian's FIFO project, although clocks and jitter reportedly work differently with R2R and Delta Sigma DACs (i.e. R2R DACs not as susceptible, so may get less milage from improved clock or clock supply) and Ian uses the Sabre DAC...

Iancanada reports here http://www.diyaudio.com/forums/digi...mate-weapon-fight-jitter-226.html#post3342520 , posts 2258 (more info in 2259) that the SI570 works best with a 3.4V LiFePO4 battery.

It might be worth considering, since so much listening was done on Ian's FIFO project, although clocks and jitter reportedly work differently with R2R and Delta Sigma DACs (i.e. R2R DACs not as susceptible, so may get less milage from improved clock or clock supply) and Ian uses the Sabre DAC...

The si570 doesn't have the on board LDO reg., so it's comparing apples with brioche...

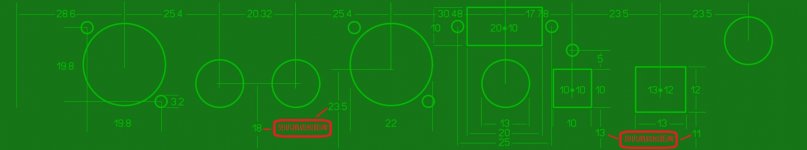

Because my English is poor, so you still look at the pictures.

4 dual-color LED USB input rate, four colors of a single hole LED display, and it is not locked will Flash.

Can be installed in the same location choice or volume.

4 dual-color LED USB input rate, four colors of a single hole LED display, and it is not locked will Flash.

Can be installed in the same location choice or volume.

Attachments

-

QQ圖片20150607143938.jpg159.4 KB · Views: 930

QQ圖片20150607143938.jpg159.4 KB · Views: 930 -

QQ圖片20150607143954.jpg134.2 KB · Views: 926

QQ圖片20150607143954.jpg134.2 KB · Views: 926 -

QQ圖片20150607143958.jpg128.3 KB · Views: 904

QQ圖片20150607143958.jpg128.3 KB · Views: 904 -

QQ圖片20150607144001.jpg134.8 KB · Views: 901

QQ圖片20150607144001.jpg134.8 KB · Views: 901 -

QQ圖片20150607144005.jpg132 KB · Views: 788

QQ圖片20150607144005.jpg132 KB · Views: 788 -

前面板尺寸.JPG133 KB · Views: 220

前面板尺寸.JPG133 KB · Views: 220 -

后面板尺寸.JPG64.3 KB · Views: 185

后面板尺寸.JPG64.3 KB · Views: 185 -

536CD308CB9E64EAEFCA5FB8827DDE8E.jpg174.7 KB · Views: 222

536CD308CB9E64EAEFCA5FB8827DDE8E.jpg174.7 KB · Views: 222 -

A980D8458553E82D85894BBCDB62C121.jpg303.2 KB · Views: 253

A980D8458553E82D85894BBCDB62C121.jpg303.2 KB · Views: 253 -

AA6CFE7219E6783827FFF8312AAA793C.jpg158.9 KB · Views: 263

AA6CFE7219E6783827FFF8312AAA793C.jpg158.9 KB · Views: 263

I'm not able to verify independently (i.e. better clock supply versus lower ripple that impacts the 5v reg) - but I tend to respect all your contributions and will take it at face value!

There is definitely a difference when supplying the 3.3V line separately.

Perhaps, as you say the main benefit of supplying the 3.3V line with the ADM7150 is the lower current draw which helps to lower ripple. FWIW, I'm getting good results from a smallish clclc filter (don't have the equipment to verify but ripple at the last PS cap according to psud2 is 0.2mV with a load as high as 360mA)... the voltages are also stable all day (no variations - though it's been awhile since I measured). In a way, my current setup is basically a clclc filter for high-freq stuff combined with the regulators onboard the DAM.

I'm not sure there are details of how the opamps derive the +-4V reference for the R2R ladder from the +-5v line to know how the 40uV noise impacts accuracy there.

When I get some time and obtain that SSR03 I'll hopefully be able to hear if a regulated low-noise supply has any gains (I don't have an AP that arthur has obviously - sigh).

You don't have to take my word for it... I don't base my opinions on someones reputation, and wouldn't expect anyone to do otherwise...

Check the Si514 Datasheet for the "Additive rms jitter due to Power Supply Noise" spec on page 7. The spec is with a 100mV sine wave added to the power supply voltage, and adds 3ps jitter at 10kHz. We are talking 40uV noise and the additive 3ps jitter spec is for 100000uV (100mV) ripple, I think it's fairly reasonable to expect the effect of noise at a level x2500 lower is going to be pretty minimal.

FWIW I've ordered a SSR04 board to replace the AC supply for mine...

Last edited:

http://item.taobao.com/item.htm?id=45511231093

http://item.taobao.com/item.htm?spm=...id=45834346272

this is my project. You can get it on Taobao. Can be mailed to China or Hong Kong.

http://item.taobao.com/item.htm?spm=...id=45834346272

this is my project. You can get it on Taobao. Can be mailed to China or Hong Kong.

The si570 doesn't have the on board LDO reg., so it's comparing apples with brioche...

Goddammit - I thought I finally had something useful!!!

Goddammit - I thought I finally had something useful!!!

All I'm saying is the results are not directly comparable. A XO/VCXO without an onboard regulator - like the Si570 - is going to be significantly more sensitive to power supply noise/ripple.

I'm not adverse to the idea of better clock power by any means... I have two x Si570 I bought about 4-5 years ago for a digital PLL project that got put into the "too hard" basket. The plan for that was to use Walt Jung's ultra low noise reference as a clock power supply...

http://item.taobao.com/item.htm?id=45511231093

http://item.taobao.com/item.htm?spm=...id=45834346272

this is my project. You can get it on Taobao. Can be mailed to China or Hong Kong.

Hello,

I am clueless how to order from this site. Despite my best effort to register, I cannot get it through. Any chance, someone who is more efficient in this matters, to help out and organize a group buy? I am sure there is a sufficient amount of people interested in these boards.

Thank you

AR2

Where do you order the salas shunt regulator board, i am guessing its the SSR04. I googled but could only find diyaudio links. Any help would be appreciated. thanks

The SSR04 is a Sjöström Super Reg (Sjöström Audio - SSR04 Sjöström Super Regulator Power Supply).

I've replaced 3v3 ldo with lt1763+lm317 prereg. It's hard to tell if there is any audible difference when there's no way to make before and after comparation.

Upgrading the 3.3V reg to give a cleaner supply for the clock and clock related portions of the FPGA is meant to give an reduction in jitter. The easiest thing to check if there is any benefit would be to test using JTEST before and after the mod, and compare the differences.

NwAvGuy: Jitter Does it Matter?

- Home

- Vendor's Bazaar

- Reference DAC Module - Discrete R-2R Sign Magnitude 24 bit 384 KHz