Hi

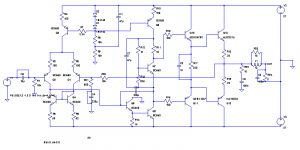

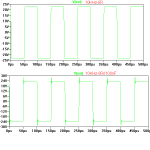

I simulated the amp Blameless-D.Self (output EF), with a load of 8R//100nF and the amp has overshoot with this load after measuring the Loop Gain and noticed that it is not PM <180° (Attached).

I am using in the output inductor with a shunt resistor (1uH-10R), output emitter follower, has no stability in capacitive load ?

The simulation is correct , anyone have any comments...

, anyone have any comments...

Thanks

I simulated the amp Blameless-D.Self (output EF), with a load of 8R//100nF and the amp has overshoot with this load after measuring the Loop Gain and noticed that it is not PM <180° (Attached).

I am using in the output inductor with a shunt resistor (1uH-10R), output emitter follower, has no stability in capacitive load ?

The simulation is correct

, anyone have any comments...

, anyone have any comments...Thanks

Attachments

Others know more than I, but your phase margin appears to be for unity gain ( 0db) while most amplifers have 26 to 40 db closed loop gain. Assuming dotted line is phase and solid is open loop gain. (26 db gives phase margin of about 95 and 100 respectively)

Hi sregor, I put the Loop Gain phase margin is in 0dB, if it graph were in Open Loop, the PM would +-26dB.

A few things you need to attend to here to improve your situation:-

1. you are running your LTP at far too low current. run it at minimum of 3mA - I prefer 10mA, but some people would say this is too high. 5mA is a good compromise.

2. The current source load in the VAS stage is far too low - you need to set this to about 30mA (on a triple emitter follower, you can get away with 15mA).

3. You need to add some emitter degeneration to your VAS transistor - you cannot run the VAS transistor like you have it without serious problems. Try about 33 Ohms to start off with.

4. I cannot read the value of your LTP mirror load resistors, but they look like 82 Ohms. These need to be about 22 Ohms each.

1. you are running your LTP at far too low current. run it at minimum of 3mA - I prefer 10mA, but some people would say this is too high. 5mA is a good compromise.

2. The current source load in the VAS stage is far too low - you need to set this to about 30mA (on a triple emitter follower, you can get away with 15mA).

3. You need to add some emitter degeneration to your VAS transistor - you cannot run the VAS transistor like you have it without serious problems. Try about 33 Ohms to start off with.

4. I cannot read the value of your LTP mirror load resistors, but they look like 82 Ohms. These need to be about 22 Ohms each.

Hi Bonsai

The values are the same as Blameless published by D.Self

LTP 3.5mA

VAS 5mA

Drivers 5mA

Bias +-110mA (RE 0,22)

The question is loss of PM, more 70° with only 100nF as load.

The values are the same as Blameless published by D.Self

LTP 3.5mA

VAS 5mA

Drivers 5mA

Bias +-110mA (RE 0,22)

The values are 68 Ohms.I cannot read the value of your LTP mirror load resistors, but they look like 82 Ohms. These need to be about 22 Ohms each.

The question is loss of PM, more 70° with only 100nF as load.

- Status

- Not open for further replies.