Hi Guys,

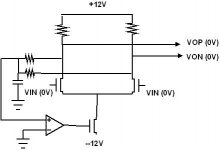

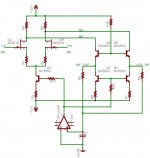

Got an idea on the preamp schematic attached. The objective are :

1) No capacitor in input and output

2) No feedback

3) Full differential I/O

4) Single stage

The opamp act as a common-mode feedback(CMFB) to null the output voltage to zero. Biasing is determined by the load resistor which is force to have 12V across it by the CMFB loop. Input transitor pair can be replace by Jfet or BJT.

Question :

1) The CMFB does not correct the differential offset voltage if it is present at the input pair.

2) The input transistor pair will always have Vgs=Vds. Will there by any problem?

3) I'm planning to use battery supply with 2X12V SLA battery connected in series. If the voltage of battery drops, the biasing will also drop. How to solve this?

Pls help.

Regards.

Got an idea on the preamp schematic attached. The objective are :

1) No capacitor in input and output

2) No feedback

3) Full differential I/O

4) Single stage

The opamp act as a common-mode feedback(CMFB) to null the output voltage to zero. Biasing is determined by the load resistor which is force to have 12V across it by the CMFB loop. Input transitor pair can be replace by Jfet or BJT.

Question :

1) The CMFB does not correct the differential offset voltage if it is present at the input pair.

2) The input transistor pair will always have Vgs=Vds. Will there by any problem?

3) I'm planning to use battery supply with 2X12V SLA battery connected in series. If the voltage of battery drops, the biasing will also drop. How to solve this?

Pls help.

Regards.

Attachments

Your design requires that the output and input voltages are both near 0. This means there isn't enough voltage on the active devices for them to work; to get in to the correct region of the device curves, you typically want at least 5 or 10V between drain and gate.

Sort of, but your Q5 and Q6 are not set up as folded cascodes.

You want PNP devices and have the Emitters looking at the

Drains of the input JFETs.

There are other ways to set up the circuit besides this. The

driving item is the desire for the requirements of the thread title.

😎

You want PNP devices and have the Emitters looking at the

Drains of the input JFETs.

There are other ways to set up the circuit besides this. The

driving item is the desire for the requirements of the thread title.

😎

- Status

- Not open for further replies.