I have a DAC based on the PCM1794.

I have a passive analog section using a transformer.

I was looking at the Zen I/V and wondering if I could use a single output and either:

A. Ground the unused input.

B. Place a small resistor to ground.

C. Place an "active load" on the pin and not use the output.

This was just a thought, it would avoid a balanced to Single Ended conversion, and allow a more standard volume control. The question is what do I give up for this?

Thanks in advance.

Doug

I have a passive analog section using a transformer.

I was looking at the Zen I/V and wondering if I could use a single output and either:

A. Ground the unused input.

B. Place a small resistor to ground.

C. Place an "active load" on the pin and not use the output.

This was just a thought, it would avoid a balanced to Single Ended conversion, and allow a more standard volume control. The question is what do I give up for this?

Thanks in advance.

Doug

Step up transformer and resistor. Started with a Edcor 1:2 and a 1k resistor, liked it so much I picked up the RAKK passive line stage, which is a Lundahl LL1674 and a 3K resistor.How are you doing a passive output stage?

Last edited:

I think can live with that. I was afraid that the output had a lot of second harmonic that needed the other output to cancel, or some other show stopper.You give up to 6dB of signal/noise ratio...

Doug

do you have a circuit or just playing with "audiophoolish" ideas?

transformers do diff to single ended

modern monolithic DACs use balanced output to reject large high frequency digital noise current in their substrate - its impossible to get decent S/N without differential output

balanced circuitry also gives even harmonic cancellation

the PCM1794 has large output DC current bias - your I/V has to balance this current with low Vos from gnd - otherwise you get nonlinearity as you start to have signal current shunted by internal protection diodes

the Zen I/V may not have low enough input Vos for the PCM1794, doesn't have DC current balancing so the circuit needs some modifications to be compatible with this chip

where ever you put it, your transformer must not have any net DC current in the windings - blocking C absolutely mandatory

any or all of these ideas will perform measurably worse in distortion than the datasheet 5534 I/V - and much better op amp I/V is possible

transformers do diff to single ended

modern monolithic DACs use balanced output to reject large high frequency digital noise current in their substrate - its impossible to get decent S/N without differential output

balanced circuitry also gives even harmonic cancellation

the PCM1794 has large output DC current bias - your I/V has to balance this current with low Vos from gnd - otherwise you get nonlinearity as you start to have signal current shunted by internal protection diodes

the Zen I/V may not have low enough input Vos for the PCM1794, doesn't have DC current balancing so the circuit needs some modifications to be compatible with this chip

where ever you put it, your transformer must not have any net DC current in the windings - blocking C absolutely mandatory

any or all of these ideas will perform measurably worse in distortion than the datasheet 5534 I/V - and much better op amp I/V is possible

Last edited:

I will leave you to judge that. I currently have a step up transformer and a resistor acting as my analog stage.do you have a circuit or just playing with "audiophoolish" ideas?

Yes, I have heard that.transformers do diff to single ended

Good to know.modern monolithic DACs use balanced output to reject large high frequency digital noise current in their substrate - its impossible to get decent S/N without differential output

Yes, but is it significant?balanced circuitry also gives even harmonic cancellation

What sort of modifications are you talking about?the Zen I/V may not have low enough input Vos for the PCM1794, doesn't have DC current balancing so the circuit needs some modifications to be compatible with this chip

Zin was quoted as 15 ohms, and the common source input should be self biasing, especially since the outputs are not DC coupled. It certainly might benifit from 2 pairs of FET in parallel.

Agreed.where ever you put it, your transformer must not have any net DC current in the windings

That's one way of accomplishing it.blocking C absolutely mandatory

Measurements aren't everything. I should put together an op-amp I/V and compare for myself.any or all of these ideas will perform measurably worse in distortion than the datasheet 5534 I/V - and much better op amp I/V is possible

too good to be true?

The Zen I/V does sim ridiculously well, IMD as low as -100dB – but who knows how good the jfet models are or how well any particular current out DAC performs with nonzero input impedance and offset

jfet parameter match dependance could be explored - I really expect the complete 2nd harmonic cancellation seen in sim with idendical models is impractical with real world device variation

There is offset of -124 mV at the I/V input with the nominal models and Nelson suggests a low Ohm pot V offset adjustment for mere mortals who don’t have hundreds of the fets to select the Idss matched pairs to get the 1 mV Vos he claims in his article, balanced I/V requires good matching of 4 fets

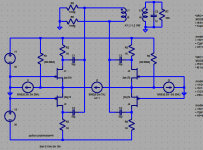

I show a sim with AC coupled xfmr (it could give selectable balanced or single ended output) to the degree that the caps match there is some psrr but filtered/regulated power is still a good idea

Cap physical size may be a challenge if you insist on film caps and low frequency response

Xfmr ratio, frequency response and Cload modification of the response are all details that need to be addressed

the current sources aproximate the PCM1794 +,- Iout, I show bias current cancellation R but not Vos adj

The Zen I/V does sim ridiculously well, IMD as low as -100dB – but who knows how good the jfet models are or how well any particular current out DAC performs with nonzero input impedance and offset

jfet parameter match dependance could be explored - I really expect the complete 2nd harmonic cancellation seen in sim with idendical models is impractical with real world device variation

There is offset of -124 mV at the I/V input with the nominal models and Nelson suggests a low Ohm pot V offset adjustment for mere mortals who don’t have hundreds of the fets to select the Idss matched pairs to get the 1 mV Vos he claims in his article, balanced I/V requires good matching of 4 fets

I show a sim with AC coupled xfmr (it could give selectable balanced or single ended output) to the degree that the caps match there is some psrr but filtered/regulated power is still a good idea

Cap physical size may be a challenge if you insist on film caps and low frequency response

Xfmr ratio, frequency response and Cload modification of the response are all details that need to be addressed

the current sources aproximate the PCM1794 +,- Iout, I show bias current cancellation R but not Vos adj

Attachments

Last edited:

I think can live with that. I was afraid that the output had a lot of second harmonic that needed the other output to cancel, or some other show stopper.

Doug

Actually, you only give up about 3dB in SNR.

Hi,

distortion- and noisewise You won´t give up much. The PCM1794A´s distortions are on par or even below the datasheets values in SE mode.

With noise figures of less than -110dB it would be hard to preserve such a low value through the analog output stages.

Cancelation of even harmonics will miss out in SE mode, but on the other hand this means a more natural spectrum of harmonics.

I´d terminate the 2nd unused DAC-output with an equal stage or at least with a similar impedance.

btw. the I-values in the Sim are not identical to the PCM1794A´s values (-6.2mA+-3.9mA, or in Mono-mode: -12.4mA+-7.8mA). The centre currents need to be sinked by dedicated current sinks or the circuit needs redesign.

What is the purpose of the I3 spanning the JFET´s sources?

As designed, check the power losses of the JFETs. With +-30V I doubt they will survive the burning

jauu

Calvin

ps: ...and yes an old NE5534 or other OP-amps will do the I/V-conversion job too....but will they sound well? My ears tell different.....very much different

distortion- and noisewise You won´t give up much. The PCM1794A´s distortions are on par or even below the datasheets values in SE mode.

With noise figures of less than -110dB it would be hard to preserve such a low value through the analog output stages.

Cancelation of even harmonics will miss out in SE mode, but on the other hand this means a more natural spectrum of harmonics.

I´d terminate the 2nd unused DAC-output with an equal stage or at least with a similar impedance.

btw. the I-values in the Sim are not identical to the PCM1794A´s values (-6.2mA+-3.9mA, or in Mono-mode: -12.4mA+-7.8mA). The centre currents need to be sinked by dedicated current sinks or the circuit needs redesign.

What is the purpose of the I3 spanning the JFET´s sources?

As designed, check the power losses of the JFETs. With +-30V I doubt they will survive the burning

jauu

Calvin

ps: ...and yes an old NE5534 or other OP-amps will do the I/V-conversion job too....but will they sound well? My ears tell different.....very much different

Calvin,

Thanks for the reply.

Doug

Thanks for the reply.

Good to hear.distortion- and noisewise You won´t give up much

Sounds good. I think I will terminate with an equal stage so I can try both SE and Balanced.I´d terminate the 2nd unused DAC-output with an equal stage or at least with a similar impedance

Won't the center current just produce a DC offset on the jfets that will be handled by the coupling caps? I can see for transformer out, a current imbalance might be very bad.The centre currents need to be sinked by dedicated current sinks or the circuit needs redesign

Doug

Hi,

the idle currrents in the positive branch will differ from that in the negative branch. In the best case this just means a DC-offset without generating greater probs, but in any case it means, that this complementary symmetrical circuit doesn´t work symmetrical any more and one of the branches could even be driven into clipping (the DAC´s centre current runs through the negative branch into the negative supply). Besides the fact that N- and P-type JFETs are not very complementary in first place, do different currents mean different working points, different temperature, etc.

The SK170/SJ74 come in TO92 casings and are rather lowcurrrent devices with less than 20mA Idss and less than 400mW heat power loss. If You run them on 30V supplies with sufficiently large idle currents.....well ..... the joy probabely won´t last long....but the heat is...bom bom bom....On

If You want to deal with the DAC´s idle current within the circuitry itself, You are probabely much better off with a SE- or asymmetrical design, e.g a simple SE-grounded base circuit like the Jocko. If You want to stay -for what reasons ever- with a complementary symmetrical circuit then better choose a dedicated current sink for the DAC´s centre current, so that the I/V converter is fed only with a smaller and DC-centered input current.

jauu

Calvin

the idle currrents in the positive branch will differ from that in the negative branch. In the best case this just means a DC-offset without generating greater probs, but in any case it means, that this complementary symmetrical circuit doesn´t work symmetrical any more and one of the branches could even be driven into clipping (the DAC´s centre current runs through the negative branch into the negative supply). Besides the fact that N- and P-type JFETs are not very complementary in first place, do different currents mean different working points, different temperature, etc.

The SK170/SJ74 come in TO92 casings and are rather lowcurrrent devices with less than 20mA Idss and less than 400mW heat power loss. If You run them on 30V supplies with sufficiently large idle currents.....well ..... the joy probabely won´t last long....but the heat is...bom bom bom....On

If You want to deal with the DAC´s idle current within the circuitry itself, You are probabely much better off with a SE- or asymmetrical design, e.g a simple SE-grounded base circuit like the Jocko. If You want to stay -for what reasons ever- with a complementary symmetrical circuit then better choose a dedicated current sink for the DAC´s centre current, so that the I/V converter is fed only with a smaller and DC-centered input current.

jauu

Calvin

Calvin,

I have been doing research. As far as I can tell from the data sheet in Fig 31, both Analog outputs have a -6.2 mA current at idle, inversely varying from -10.1 mA to -2.3 mA.

So a 6.2 V CSS to the negatives supply would take care of the center current.

I do not have any feel if the 3.2 mA current is too much for the jfet with a Idd of 10 mA.

Would you recommend I double up the jfets or try them single first.

Doug

I have been doing research. As far as I can tell from the data sheet in Fig 31, both Analog outputs have a -6.2 mA current at idle, inversely varying from -10.1 mA to -2.3 mA.

So a 6.2 V CSS to the negatives supply would take care of the center current.

I do not have any feel if the 3.2 mA current is too much for the jfet with a Idd of 10 mA.

Would you recommend I double up the jfets or try them single first.

Doug

- Status

- This old topic is closed. If you want to reopen this topic, contact a moderator using the "Report Post" button.

- Home

- Source & Line

- Digital Line Level

- What is the tradeoff to run a DAC single ended?