Hi all,

I have been trying to work out the power dissipation of transistors.

With a purely resistive load this can be calculated quite easily.

For peak power:

Ptrans = (Vsupply - Vpeak_output) / Ipeak_output

It gets trickier with adding a loudspeaker load, due to it having an electrical phase angle.

I read that a good worst case phase angle is 45° as this would double the transistors dissipation and half the power for the loudspeaker.

And I read that the worst case output voltage is 0.637 x the supply voltage.

So I simulated an amplifier driving a load that introduces a 45° lagging phase with a Z of 8.5 ohms.(960uH in series with 6ohms)

Vout = 0.637 x Vsupply = 19.11V

I then simulated a purely resistive 8.5 ohm load. I see that the transistor is dissipating about twice the power at a 45° phase angle but I don't see that the load power is being halved.

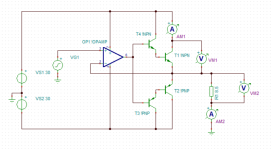

fig.1 Simulation.

fig.2 Transistor power dissipation with a reactive load.

fig.3 Transistor power dissipation with a resistive load.

I read most of the info I used on https://sound-au.com/patd.htm.

And because I know Rod must be right, my conclusion is that I must be doing something/everything wrong/stupid.

Thank you in advance!

I have been trying to work out the power dissipation of transistors.

With a purely resistive load this can be calculated quite easily.

For peak power:

Ptrans = (Vsupply - Vpeak_output) / Ipeak_output

It gets trickier with adding a loudspeaker load, due to it having an electrical phase angle.

I read that a good worst case phase angle is 45° as this would double the transistors dissipation and half the power for the loudspeaker.

And I read that the worst case output voltage is 0.637 x the supply voltage.

So I simulated an amplifier driving a load that introduces a 45° lagging phase with a Z of 8.5 ohms.(960uH in series with 6ohms)

Vout = 0.637 x Vsupply = 19.11V

I then simulated a purely resistive 8.5 ohm load. I see that the transistor is dissipating about twice the power at a 45° phase angle but I don't see that the load power is being halved.

fig.1 Simulation.

fig.2 Transistor power dissipation with a reactive load.

fig.3 Transistor power dissipation with a resistive load.

I read most of the info I used on https://sound-au.com/patd.htm.

And because I know Rod must be right, my conclusion is that I must be doing something/everything wrong/stupid.

Thank you in advance!