Nope. There are two, just hard to see. 200 ohms will not do it, so i have to use bigger pot or put resistor in series. Didnt feel like messibg with it after i couldnt get bias up, so i will finish tomorrow. All else is good, functioning as expected. Tomorrow should go quickly.

Ikebana!

Looks like my bench. But neater.

Don't be afraid to use clip leads....

😎

OK. Irritated now. Cant figure out what is wrong. Cannot bring bias up past about 1V. If I check the FE independent of the output transistors, all is fine. Attaching output transistors, I have 56V across Jfet until i bias it up and then everything levels up and I have 27V across both top and bottom fets. From there it goes nowhere. cat bring gate voltage pass about 1V. What is stealing my current? I have the negative input shorted to ground. Can get the offset close to zero, then it starts to wonder. Dont have the feedback point bypassed with cap, so ill try that to stop the wandering output.

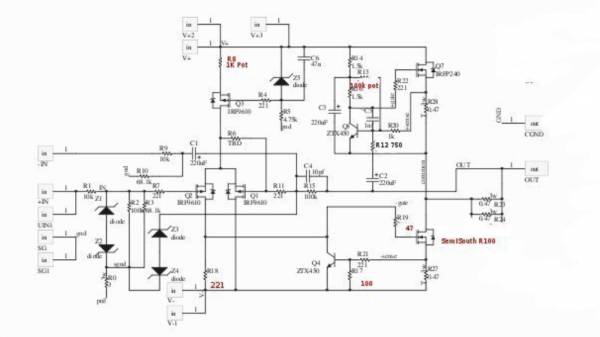

gimme exact schm which you're using , voltage across LTP drain resistor , voltages across Rs-es in output and output offset

it's wise to start troubleshooting with just one output pair , same as 9V1 zenners between G and S of outputs (you can pull it out later)

it's wise to start troubleshooting with just one output pair , same as 9V1 zenners between G and S of outputs (you can pull it out later)

Tea,

your schematic is too small to see.

ZM,

I am using the schematic from earlier in the thread given to 6L6. Fe is fine as far as I can tell. Found a little clue when testing bjt in ACS for Vdrop. When i connected one probe to the output and one to the gate of the bjt, all the sudden bias came up. I am assuming this points to bad bjt.

your schematic is too small to see.

ZM,

I am using the schematic from earlier in the thread given to 6L6. Fe is fine as far as I can tell. Found a little clue when testing bjt in ACS for Vdrop. When i connected one probe to the output and one to the gate of the bjt, all the sudden bias came up. I am assuming this points to bad bjt.

Attachments

Ok, so I got one side biased up, but new problem has presented it's self. With Vdrop at about 600mV, I get big negative offset at output of about-22V. It seems like top Hal is not matching bottom half in current. I can begin to trim it out, but bias gets way to high on SS.

replace R27 with fixed resistor of 47K + 47K trimpot

then set Aleph CCS current with it , then chase DC offset with trimpot in LTP drain

then set Aleph CCS current with it , then chase DC offset with trimpot in LTP drain

So simply adjusting contribution of ACS to output. Is this because SS hs higher gain than FQA?

100k pot should work fine, correct.

100k pot should work fine, correct.

with biasing , you're still in DC domain , strictly

I'm saying that , understanding "contribution of ACS to output" as AC thing

take it from this angle - you're gonna to adjust Aleph CCS for desired current ;

then - chasing 0 DC offset on out , you're gonna to adjust it's load ( lower half of amp ) ........ looking at it as on variable resistor ;

R too small - offset in neg

R too high - offset in pos

considering that A CCS is pumping same current in both cases

do not forget to gnd both inputs

I'm saying that , understanding "contribution of ACS to output" as AC thing

take it from this angle - you're gonna to adjust Aleph CCS for desired current ;

then - chasing 0 DC offset on out , you're gonna to adjust it's load ( lower half of amp ) ........ looking at it as on variable resistor ;

R too small - offset in neg

R too high - offset in pos

considering that A CCS is pumping same current in both cases

do not forget to gnd both inputs

Last edited:

Using pot does nothing. Now showing only 4V across MOSFET DS and 48V across SS DS. Bad MOSFET?

Last edited:

probably

whatever - you know the drill - how to pull it from circ and test

replace , and stick to just one output pair , while troubleshooting

whatever - you know the drill - how to pull it from circ and test

replace , and stick to just one output pair , while troubleshooting

Changed MOSFET, no difference.

Here are my numbers

SS Vgs - 1.295

Vds - 48V

FQA Vgs - 4.0

Vds - 4.0

Just to make sure I am right, I have negative input shorted to ground.

Here are my numbers

SS Vgs - 1.295

Vds - 48V

FQA Vgs - 4.0

Vds - 4.0

Just to make sure I am right, I have negative input shorted to ground.

Forgive me. Today was a dumb day. I have the transistors in the wron position. I have them in q6 and q8 and they have to be in q5 an q7.

both inputs shorted to gnd

it seems you made some other mistake there

without my presence right above your shoulder , or without pics - it's hard to say

edit : - you posted another one , while I typed

clarify

editedit:

got it - there is no connection to bjt base in A CCS , that way

it seems you made some other mistake there

without my presence right above your shoulder , or without pics - it's hard to say

edit : - you posted another one , while I typed

clarify

editedit:

got it - there is no connection to bjt base in A CCS , that way

Last edited:

- Status

- Not open for further replies.

- Home

- Amplifiers

- Pass Labs

- The Aleph Jango