I've been looking at ways to get output powers above 20W or so (the output of my TDA8932 implementation) for quite some time now and last week was getting quite close with my idea of stacking TDA1566 amps (putting them in series with isolated PSUs). The TDA1566 has the great feature of being able to drive down to 1R loads in mono mode which means it has a very generous output current capability. But several of my prototype builds of TDA1566 failed unexpectedly (before I even got to stack them) so I've become suspicious of the quality of chips I have been getting. The TDA1566s from Taobao are new, not recycled so I'm veering towards the conclusion of them being sub-par devices.

The other very nice feature of TDA1566 is it has a low-gain mode (16dB) with impressively low output noise (~22uV). No other chipamp I've seen delivers such low output noise, mostly because they don't have the capability to run such a low gain. Enter TDA1521, its unique in NXP's chipamp line-up in that there is the apparent capability to run it at a lower gain than stock (30dB) but how low it can go before it goes unstable is anyone's guess. Hence this project in which I hope to uncover how low it can be pushed. The ability to trim the gain channel by channel opens up the possibility of running these devices in parallel - to minimize cross-conduction the gains of the parallel elements do need to be very closely matched, much better than the DS gain variability (0.2dB typical).

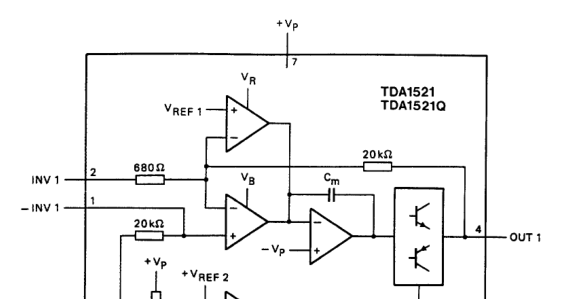

Here's the internal structure of the 1521, only one channel shown. The unusual feature here is that 'INV1' pin is brought out of the package rather than being returned directly to AC GND on-chip. Which means some extra series resistance can be added which will have the effect of lowering the gain. The resistors on-chip are not close tolerance so the 680R and 20k could be anywhere within 30% or so of their nominal value which means the external R needed for a particular gain will have quite a wide range of possible values. Therefore I'm going to use a multiturn trimpot to realize that. My initial target is to get down to 20dB gain and see if that's still sufficiently stable....

The other very nice feature of TDA1566 is it has a low-gain mode (16dB) with impressively low output noise (~22uV). No other chipamp I've seen delivers such low output noise, mostly because they don't have the capability to run such a low gain. Enter TDA1521, its unique in NXP's chipamp line-up in that there is the apparent capability to run it at a lower gain than stock (30dB) but how low it can go before it goes unstable is anyone's guess. Hence this project in which I hope to uncover how low it can be pushed. The ability to trim the gain channel by channel opens up the possibility of running these devices in parallel - to minimize cross-conduction the gains of the parallel elements do need to be very closely matched, much better than the DS gain variability (0.2dB typical).

Here's the internal structure of the 1521, only one channel shown. The unusual feature here is that 'INV1' pin is brought out of the package rather than being returned directly to AC GND on-chip. Which means some extra series resistance can be added which will have the effect of lowering the gain. The resistors on-chip are not close tolerance so the 680R and 20k could be anywhere within 30% or so of their nominal value which means the external R needed for a particular gain will have quite a wide range of possible values. Therefore I'm going to use a multiturn trimpot to realize that. My initial target is to get down to 20dB gain and see if that's still sufficiently stable....

I set up my signal gen with its squarewave output to have a look at how the step response varies with different gains.

At 30dB, the response is essentially perfect with zero overshoot. At 20dB there's some overshoot, I estimate (just by eye) it's below 10% and there are a couple of damped half-cycles of ringing. I'm not sure how close to unstable this would be but seems from one or two articles I found tying together step response with phase margin that it could be the phase margin is of the order of 40 degrees with this kind of response.

I then took a different tack - see what resistor values lead to permanent oscillation. For this I fitted a 20k trimpot between pin2 and AC GND and started with it at max. Sure enough, oscillation begins (at a frequency somewhere between 600kHz and 1MHz) at very low supply voltage (4V total). This ability to work as an oscillator at low voltage is reassuring as I was hoping not to blow the chip up from its self-oscillation. I found at ~6k8 the oscillation stopped when at 4V supply but returned when the supply volts were raised higher. In order not to have oscillation at a normal supply (15V and up) the preset needs to be 4k4 or lower.

To set these values in some kind of context, I attempted to measure the total resistance of the feedback R (20k) plus the 680R by applying my ohmmeter between pins 4 and 2. However I got two different readings, depending on which polarity I applied so I guess my meter applies too high a voltage and forward biasses some internal junctions. So a second try I made with my LCR meter which has the feature of limiting the test voltage to 0.1V. This also wouldn't give a stable reading and it was somewhat dependent on frequency. The 20k input resistor though can be measured directly (pin1 to pin3) with the DMM. I don't know enough about on-chip resistors to know if all the values scale together or if only explicitly matched ones (feedback and -ve input) do. These latter two have to match a lot better than the usual 30% to set the gain within 0.2dB.

So given I have no way to determine those internal resistors accurately, I'll for now go with nominal. With the 4k4 at the edge of oscillation the gain works out nominally as 1+(20/(4.4+0.68)) = 4.9 or ~14dB. This suggests at my target 20dB gain I'll have 6dB gain margin.

At 30dB, the response is essentially perfect with zero overshoot. At 20dB there's some overshoot, I estimate (just by eye) it's below 10% and there are a couple of damped half-cycles of ringing. I'm not sure how close to unstable this would be but seems from one or two articles I found tying together step response with phase margin that it could be the phase margin is of the order of 40 degrees with this kind of response.

I then took a different tack - see what resistor values lead to permanent oscillation. For this I fitted a 20k trimpot between pin2 and AC GND and started with it at max. Sure enough, oscillation begins (at a frequency somewhere between 600kHz and 1MHz) at very low supply voltage (4V total). This ability to work as an oscillator at low voltage is reassuring as I was hoping not to blow the chip up from its self-oscillation. I found at ~6k8 the oscillation stopped when at 4V supply but returned when the supply volts were raised higher. In order not to have oscillation at a normal supply (15V and up) the preset needs to be 4k4 or lower.

To set these values in some kind of context, I attempted to measure the total resistance of the feedback R (20k) plus the 680R by applying my ohmmeter between pins 4 and 2. However I got two different readings, depending on which polarity I applied so I guess my meter applies too high a voltage and forward biasses some internal junctions. So a second try I made with my LCR meter which has the feature of limiting the test voltage to 0.1V. This also wouldn't give a stable reading and it was somewhat dependent on frequency. The 20k input resistor though can be measured directly (pin1 to pin3) with the DMM. I don't know enough about on-chip resistors to know if all the values scale together or if only explicitly matched ones (feedback and -ve input) do. These latter two have to match a lot better than the usual 30% to set the gain within 0.2dB.

So given I have no way to determine those internal resistors accurately, I'll for now go with nominal. With the 4k4 at the edge of oscillation the gain works out nominally as 1+(20/(4.4+0.68)) = 4.9 or ~14dB. This suggests at my target 20dB gain I'll have 6dB gain margin.

Hi Jan - thanks for the suggestion. I have given that some thought but not gotten any further with the idea than just thinking. I did try a cap between INV1 terminal and AGND but that made the overshoot much worse so it came out again proto.

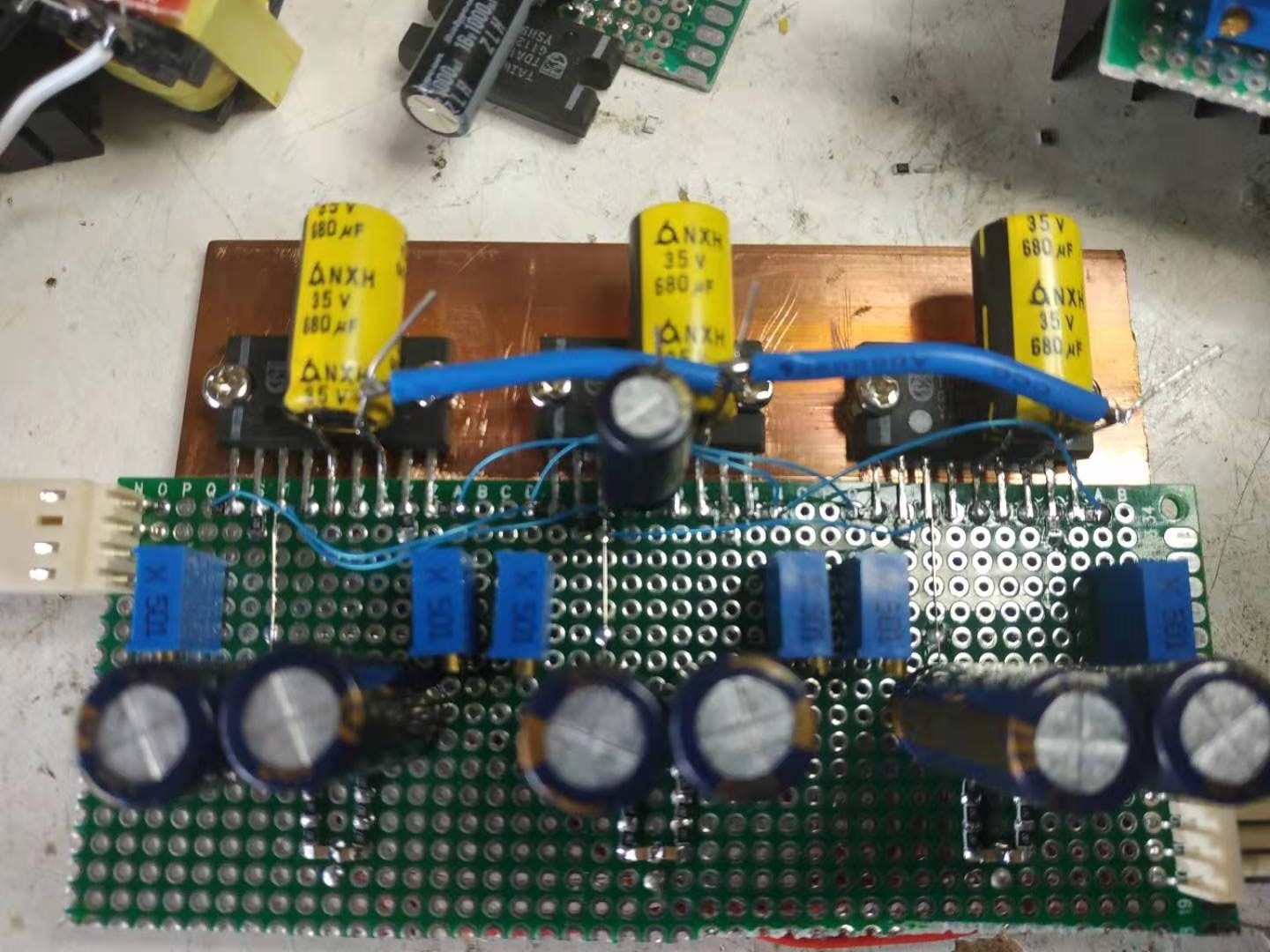

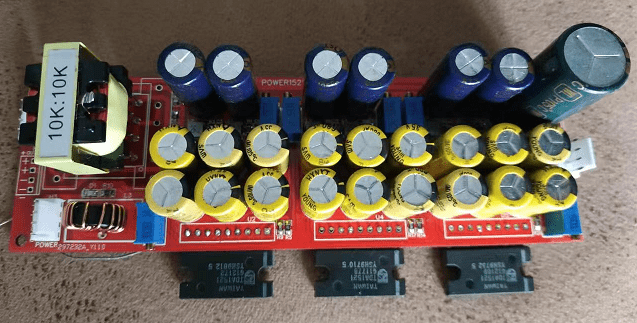

Here's my first three-paralleled amp prototype lash-up. Now I'm in process of building a second one to have a proper listen but in mono its sounding promising, plenty of background ambience. I found I can trim the gains by just watching the supply current (no load connected) and tweaking to minimize that while playing out a test sine. My bench power supply only resolves 10mA, probably I'll do better by finding an ammeter which has 1mA resolution. Due to the significant variation in DC offset between, I'm paralleling via caps at present rather than trying to trim that out with another array of trimmers. The heatsink's some copper bar I found lying around, its more a heatspreader than a heatsink. Phase splitting is done by a Taobao 10k:10k CT permalloy trafo.

Here's my first three-paralleled amp prototype lash-up. Now I'm in process of building a second one to have a proper listen but in mono its sounding promising, plenty of background ambience. I found I can trim the gains by just watching the supply current (no load connected) and tweaking to minimize that while playing out a test sine. My bench power supply only resolves 10mA, probably I'll do better by finding an ammeter which has 1mA resolution. Due to the significant variation in DC offset between, I'm paralleling via caps at present rather than trying to trim that out with another array of trimmers. The heatsink's some copper bar I found lying around, its more a heatspreader than a heatsink. Phase splitting is done by a Taobao 10k:10k CT permalloy trafo.

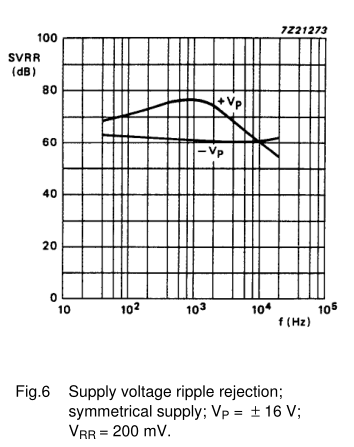

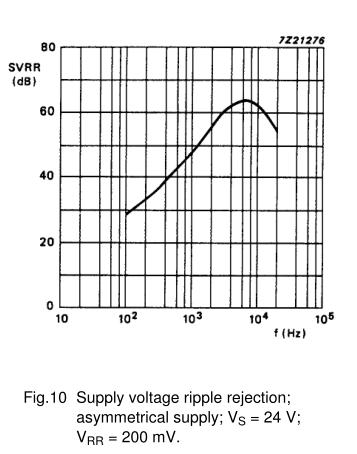

Doing some calculations as to how many caps to have on the supply rails, I came across the discrepancy between the PSRR in symmetrical vs asymmetrical mode :

I figured the difference would be down to the recommended cap on pin3 (AC GND) which is 100uF. In turn, this cap is fed from VP via 10k. So attenuation of PS noise @100Hz is 56dB, resulting in -26dB at the output after 30dB of gain. To reach the 60dB PSRR figure at 100Hz the cap is wildly too small. To gain an extra 30dB PSRR needs 32X the value, so 3,300uF. But then how long after power-up before the amp un-mutes itself?

I figured the difference would be down to the recommended cap on pin3 (AC GND) which is 100uF. In turn, this cap is fed from VP via 10k. So attenuation of PS noise @100Hz is 56dB, resulting in -26dB at the output after 30dB of gain. To reach the 60dB PSRR figure at 100Hz the cap is wildly too small. To gain an extra 30dB PSRR needs 32X the value, so 3,300uF. But then how long after power-up before the amp un-mutes itself?

I'm very happy with how the three-paralleled chip amp sounds. Now how to arrange a power supply for it?

The simplest route would be to buy a switching brick off the shelf. Trouble is, in order to accommodate the peak current requirements the brick usually ends up well over-specified. Let's go through the math....

In order that the TDA1521 is the bottleneck (not the supply) we need a 6.6A peak current per channel, so 13.2A total. With a 36V output brick this calls for a power rating close to 500W. If we adopt the traditional 1/8th power white noise scenario as the torture test then the power draw in such circumstances is about 2/3 of the max amp output. So the switching brick will see a load around 30% of its power rating. Also such supplies generate nasty common-mode noise which is really hard to filter out.

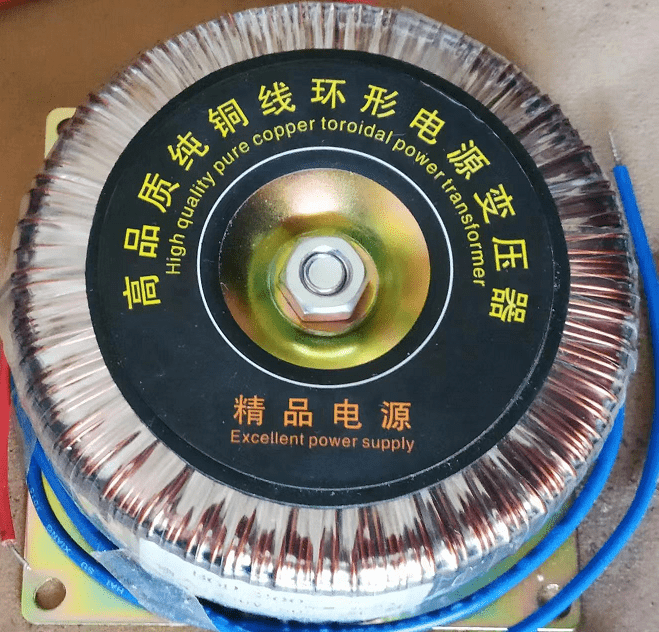

To get around the common-mode noise issue, I could use a traditional mains-fed toroidal to give me raw and ripply DC and then follow that with a switching regulator. Since trafos are thermally (rather than current) limited that should mean I could go for a 250VA type and hope that my switching regulator can deliver the required current. There does seem to be a good choice of cheap switching modules available nowadays, for example : https://www.aliexpress.com/item/4001231231815.html This is a 12A rated buck reg with an input voltage up to 55V max so I imagine driving it from a full-wave rectified 35VAC secondary.

The simplest route would be to buy a switching brick off the shelf. Trouble is, in order to accommodate the peak current requirements the brick usually ends up well over-specified. Let's go through the math....

In order that the TDA1521 is the bottleneck (not the supply) we need a 6.6A peak current per channel, so 13.2A total. With a 36V output brick this calls for a power rating close to 500W. If we adopt the traditional 1/8th power white noise scenario as the torture test then the power draw in such circumstances is about 2/3 of the max amp output. So the switching brick will see a load around 30% of its power rating. Also such supplies generate nasty common-mode noise which is really hard to filter out.

To get around the common-mode noise issue, I could use a traditional mains-fed toroidal to give me raw and ripply DC and then follow that with a switching regulator. Since trafos are thermally (rather than current) limited that should mean I could go for a 250VA type and hope that my switching regulator can deliver the required current. There does seem to be a good choice of cheap switching modules available nowadays, for example : https://www.aliexpress.com/item/4001231231815.html This is a 12A rated buck reg with an input voltage up to 55V max so I imagine driving it from a full-wave rectified 35VAC secondary.

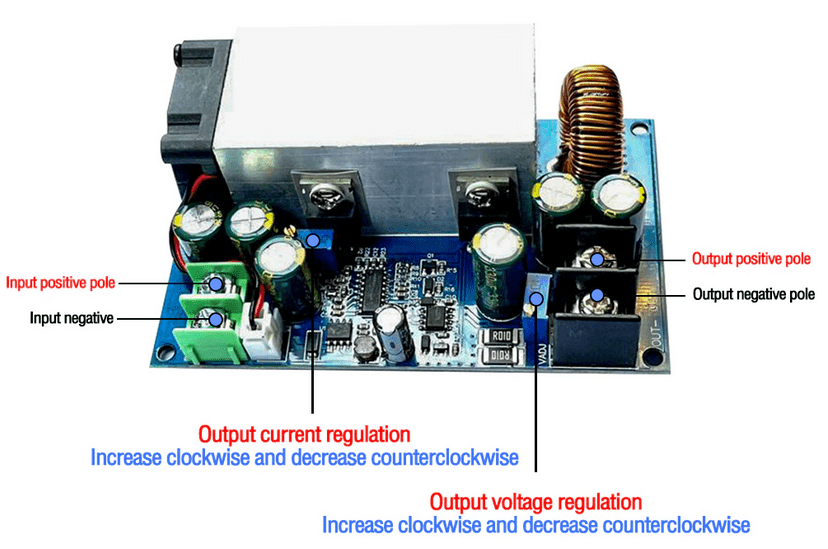

Having looked around a bit more and simulated a toroidal PSU, a bit more voltage headroom at the buck input would be very useful. I found this one, which has input voltage capability up to 75V and even more current capability. At $8 its a snip, that is assuming its fan doesn't run all the time. If it does, I might just risk disconnecting it as I'm barely going to use 25% of its claimed power rating :

https://www.aliexpress.com/item/1005005450194755.html

https://www.aliexpress.com/item/1005005450194755.html

The buck board arrived - no markings visible on any of the 3 ICs, all identification carefully scored out. The two TO220 devices on the heatsinks are almost certainly MOSFETs and these drive the output inductor (Sendust cored) in a half-bridge. Switching rate looks to be around 80kHz so filtering the output ripple shouldn't present too big a challenge.

Yeah thanks for that, I also have been rather doubtful about green/yellow sleeved caps in the past as I found their voltage ratings substantially too optimistic.

The output caps are 330uF/63V which, when you get that value/voltage from a reputable Japanese manufacturer like Nichicon come in a 10*25 case size. These ChongX are 10*20 so chances are they're only 50V. I'm not planning on going over 40V for the output so I'll keep them in for the time being but maintain a watchful eye. Input caps are 100u/100V and I'm only planning on going up to ~70V.

The output caps are 330uF/63V which, when you get that value/voltage from a reputable Japanese manufacturer like Nichicon come in a 10*25 case size. These ChongX are 10*20 so chances are they're only 50V. I'm not planning on going over 40V for the output so I'll keep them in for the time being but maintain a watchful eye. Input caps are 100u/100V and I'm only planning on going up to ~70V.

@abraxalito is there any turn on/off thump prevention feature in your design?

@abraxalito is there any turn on/off thump prevention feature in your design?

None beyond what's already designed into the TDA chips themselves. I've not noticed significant issues with the prototypes so far, but its early days. I quite like hearing a gentle turn on 'plop' as confirmation the amp's working, reminds me of my old NAD3020 amp.

What will the estimated/target output power into 8R speakers?

It depends on the supply voltage - at the max (42V) it will be about 100W/8R but I'm not sure that there's short-circuit protection for the outputs at the maximum chip voltage. The DS says for short-circuit protection the max supply is 28V however their short circuit test lasts for 1hr which I think is rather too pessimistic.

The toroidal trafo came in too, forgot to mention that. I've run some LTSpice simulations and although this is only 200VA (2.4kg) it should be able to handle 2 * 100W short-term output power (~300W from the trafo) without difficulty in conjunction with the buck regulator. Of course, long-term it'll overheat if subjected to continuous sinewave testing but I don't intend to do that.

I've stuffed enough components on the first PCB to begin some testing. Gain setting is the first stage, adjust each channel individually to 23dB before fitting the paralleling caps (purple ones at the top). From experience with the first prototype, the gain is best tweaked further later on whilst watching the quiescent current (nominally 100mA) once all three channels are in order.

Before I'll play it at any volume into a real load, it needs some heatsinking...

Before I'll play it at any volume into a real load, it needs some heatsinking...

- Home

- Amplifiers

- Chip Amps

- TDA1521 - possibility of reduced gain?