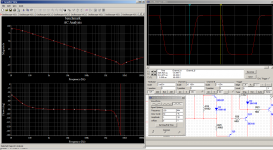

The slew rate looks like it is around 20V/µs.

The phase margin is almost 90°.

Could the 330pF be reduced slightly, to give some performance benefit?

There is only 1/3 of the output voltage between each 330pF. The slew rate is about the same if you remove all the resistors around the capacitors. In my case, if you remove all the resistor, the equivalent miller cap is about 100pF.

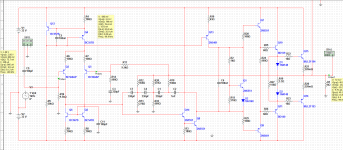

This is very unlikely to be stable.

I haven't investigated the stability yet.

I am afraid I am not able to do that with my crappy math.

Use LTSpice and not Multisim to investigate loop gain.

I will take some time to try LTSpice. Never tried LTSpice before.

I will appreciate that if some one simulate this extreme TMC version before I get the results.

- Status

- This old topic is closed. If you want to reopen this topic, contact a moderator using the "Report Post" button.

- Home

- Amplifiers

- Solid State

- Super TMC