Ok, thanks for info, I am trying to understand the logic at the moment.oo, yes, i missed. But is same F7 series, just H7 is newer and faster - and only 2 or 3 € more. (if can get any STM32xx, this time )

#oldjack i looked at

https://github.com/PaulStoffregen/Audioand this looks good, maybe you can realize your digital crossover in short time with a Teensy 4.1 this way.

But you have to try it with real parts, to see, it works as you want and how is the sound then....

With the clock recovery I understand about the phase locked loop, when I have clock recovery do I feed the signal to the processor with an integer multiplier.

Thanks, my intention was to decode the SPDIF into a usable code then implement the digital filter so that I have three frequency streams followed by digital attenuation for each stream.Regarding timing information in SPDIF type signals, the least jittery solution for a DAC is FIFO buffering (at the cost of some time-delay), the next best is ASRC (if referenced to a local low-jitter crystal clock, which also serves as the MCLK source for the dac), the worst performer is PLL recovery of MCLK from the SPDIF stream (since the dac is then forced to use a more jittery MCLK time reference).

A good SPDIF receiver chip such as SRC4392 can do both ASRC, and PLL MCLK recovery. Either way some kind of a PLL is involved. In the case of ASRC there is a PPLL (polyphase locked loop) used to estimate selection of correct resampling filter coefficients on the fly. While neither type of PLL can perfectly correct for SPDIF jitter, the advantages of a local crystal clock weigh in favor of ASRC.

One other thing to perhaps to consider, IME typical audio FFT analysis of jitter effects on audio is of limited utility. It works pretty well for seeing deterministic jitter in a SPDIF stream (using J-Test), but it doesn't make it so easy to visualize potential audible effects of nondeterministic jitter and or of close-in phase noise. Therefore some people assume the latter two factors do not matter. Out of sight out of mind, I guess.

Finally each stream would have a dac unit for input to each of the three analogue amps.

So I guess I would have to install my own dac units within the amplifier casing.

I will have a look at the SPDIF receiver unit that you mention.

If the input incorporates adaptive resampling, no HW clock recovery is required, of course. The question is quality of the resampling and quality of measuring the input/output rates ratio, so that the resampling fractional ratio deviates minimally. But since nothing else would run on the single core, maybe the IRQ routines may face more or less constant delays and the ratio measuring could be OK.

There's some talk of doing S/PDIF decoding on a RPi Pico : https://forums.raspberrypi.com/viewtopic.php?p=1945552&hilit=spdif#p1945552

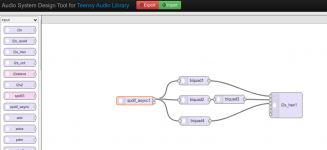

Thanks for thatwith the Teensy audio lib you would setup something like this: (one channel shown)

View attachment 1029664

and connect 3 dacs to the I2S output, i would begin with 3 x TDA1387 , can get at 20ct from Ali...

so it will cost about 30 $ to make the real test. (no drama - right?)