Actually I wrote a set of mini-floating point routines for PIC16, in order to use 8 bit exponent and 8 bit mantissa, for best speed/accuracy ratio in multiplication, squaring, square root, and division. I used to disassemble computer games in the old times, including 8-bit 3D games, fascinated about how these calculations were possible in modest CPUs.

You are crazy in a nice way. 😀

I have over stayed my visit here, lets get back to topic I'm sure others are waiting for audio related questions.

Power supply discussion is closely related to audio, because audio optimally needs a different type of SMPS compared to applications like computing or lighting, two usual sources of SMPS resources used in audio, but audio needs higher short term power and faster response, and also overload handling without shutdown. I conducted extensive research about how to reduce the use of natural resources and maximize power efficiency in audio PFC SMPS, using the most general-purpose parts available, reaching results like the theoretical limit in bulk capacitance reduction without degradation in power response. Not just satisfied with the first valid schemes I could implement.

Two worlds colliding 😀

Hardware oriented & resource minimized

vs

Throw with uC resources because they are there for cheap & small in size

Seeing growing amounts of powerful uC for cheap with plenty of integrated ADC, comparators, OP amps ...almost anything you wish - the break even between both approaches moves from high power & and high complexity power electronics towards less demanding applications.

The last big step which I noticed was about 2-3 years ago when suddenly multiple manufacturers decided to throw their ARM Cortex-M0 with lots of integrated peripherals and pretty some flash into the market for prices just moderately above the level people were used for 8-Bit devices that time.

And it is likely that the trend of powerful uC for little money will go on.

The growing amount of useful standard functions in the libraries of the IDEs is also going to make things more and more attractive for people with limited knowledge in power electronics and limited knowledge in uC details as well.

But if the power stage is messed, then it will remain hard to achieve high efficiency, reliability and meeting regulations.

For this reason companies like TI spend more and more efforts on standard integrated power stages and reference designs. ==> Drawing more of the value chain into their house, but at the same time keeping the product liability for the power electronics at customer side.

Valid business model, no matter if I like it or not.

P.S:

Thanks Eva, for telling at least a rough overview of your design.

Hardware oriented & resource minimized

vs

Throw with uC resources because they are there for cheap & small in size

Seeing growing amounts of powerful uC for cheap with plenty of integrated ADC, comparators, OP amps ...almost anything you wish - the break even between both approaches moves from high power & and high complexity power electronics towards less demanding applications.

The last big step which I noticed was about 2-3 years ago when suddenly multiple manufacturers decided to throw their ARM Cortex-M0 with lots of integrated peripherals and pretty some flash into the market for prices just moderately above the level people were used for 8-Bit devices that time.

And it is likely that the trend of powerful uC for little money will go on.

The growing amount of useful standard functions in the libraries of the IDEs is also going to make things more and more attractive for people with limited knowledge in power electronics and limited knowledge in uC details as well.

But if the power stage is messed, then it will remain hard to achieve high efficiency, reliability and meeting regulations.

For this reason companies like TI spend more and more efforts on standard integrated power stages and reference designs. ==> Drawing more of the value chain into their house, but at the same time keeping the product liability for the power electronics at customer side.

Valid business model, no matter if I like it or not.

P.S:

Thanks Eva, for telling at least a rough overview of your design.

higher short term power and faster response: that is exactly what dc rail capacitors are for.

How much capacitance would we need to double the power output of a 1KW brick for 2~3 seconds within a 10~20% voltage drop? This is not even a job for capacitors, but for batteries, math will tell. But when imagination is not trained doing math and prototypes, and instead it is trained reading and telling stories, everything feels possible but the power of optimization is lost.

no stories eva, i can do math, believe me. i do have a masters degree in power electronics.

EIAJ is a standard test, it is 8 cycles of 1khz. many musical transients are even shorter. 2 - 3 secs power budget of any amp is usually much lower than the burst rms capability. reason 1 cost is not justified to have several second long full power sine waves, reason 2 cooking the voice coil is not intended anyway.

there is many different power levels that can be sustained for every amp. they get lower and lower as the duration increases. look at older amps that were considered high end once high end, like fp6400 (google: "bench test comparison") . continuous power just needs only to be quite low in comparison to EIAJ, so what? your power supply need not have a super fast response as the capacitors are able to sustain some milliseconds.

btw: the "output of a 1kW brick" even just below clipping on typical speakers is usually far less than 1KW, since speakers tend to be higher ohmic, and in addition, a class D amp can recycle reactive power by it s nature in contrast to class AB or H. So even 1KVA apparent power at the output (what is rms voltage times rms current) would maybe draw down the capacitors with a real load of, say 500W or less...

EIAJ is a standard test, it is 8 cycles of 1khz. many musical transients are even shorter. 2 - 3 secs power budget of any amp is usually much lower than the burst rms capability. reason 1 cost is not justified to have several second long full power sine waves, reason 2 cooking the voice coil is not intended anyway.

there is many different power levels that can be sustained for every amp. they get lower and lower as the duration increases. look at older amps that were considered high end once high end, like fp6400 (google: "bench test comparison") . continuous power just needs only to be quite low in comparison to EIAJ, so what? your power supply need not have a super fast response as the capacitors are able to sustain some milliseconds.

btw: the "output of a 1kW brick" even just below clipping on typical speakers is usually far less than 1KW, since speakers tend to be higher ohmic, and in addition, a class D amp can recycle reactive power by it s nature in contrast to class AB or H. So even 1KVA apparent power at the output (what is rms voltage times rms current) would maybe draw down the capacitors with a real load of, say 500W or less...

Two worlds colliding 😀

Hardware oriented & resource minimized

vs

Throw with uC resources because they are there for cheap & small in size

Seeing growing amounts of powerful uC for cheap with plenty of integrated ADC, comparators, OP amps ...almost anything you wish - the break even between both approaches moves from high power & and high complexity power electronics towards less demanding applications.

The last big step which I noticed was about 2-3 years ago when suddenly multiple manufacturers decided to throw their ARM Cortex-M0 with lots of integrated peripherals and pretty some flash into the market for prices just moderately above the level people were used for 8-Bit devices that time.

And it is likely that the trend of powerful uC for little money will go on.

The growing amount of useful standard functions in the libraries of the IDEs is also going to make things more and more attractive for people with limited knowledge in power electronics and limited knowledge in uC details as well.

But if the power stage is messed, then it will remain hard to achieve high efficiency, reliability and meeting regulations.

For this reason companies like TI spend more and more efforts on standard integrated power stages and reference designs. ==> Drawing more of the value chain into their house, but at the same time keeping the product liability for the power electronics at customer side.

Valid business model, no matter if I like it or not.

P.S:

Thanks Eva, for telling at least a rough overview of your design.

Try to control something more complex than a fixed frequency "buck" or "boost" through the brute force ADC/math/PWM approach. Lets say a resonant flyback simulating resistive input, or a cuk, a sepic, something with several poles and zeros, something where the reactive elements dictate variable switching frequency to keep resonant operation and/or good mains conduction angle, some converter where the size of the capacitors and coils has to be minimized and no concessions can be made towards simpler control with bigger parts for more distant poles and zeros.

At the beginning of the thread you were asking about the transition between discontinuous and continuous mode. You know this transition is difficult, or you would not be asking. Actually the DSP method obfuscates this transition because this is not the optimum way to control converters at all. The comparator method makes the transition unnoticeable, it cancels all the non-linearity and makes a linear loop.

Do you want to solve 100.000 systems of differential equations per second in real time? What math functions do you think "comparing two resettable integrators over time" is calculating? "a+b*c"? Something easy to calculate with DSP? No.

Oh, wait. Then there is latency. DSP methods have latency that result in much higher MIPS and MSPS requirements for same phase margin as analog. In "tight" control loops there is always a penalty for the DSP method preventing to get close to theoretical limits. The DSP method is naturally flawed for "tight" control loops, despite being the way to go for most other purposes. That's the secret behind the lack of real progress in the SMPS field.

Now continue trying to buy the solution from sources that, apart from not having the solution, have to recover the expense of trying to find the solution the wrong way. Like: "Someone wants free Asbestos? We are just about to ban Asbestos, but first we must clean stocks and recover investments".

Last edited:

Thanks Eva, for telling at least a rough overview of your design.

+1 this is a really fascinating thread, keep the insights coming Eva. Subscribed.

Hi Eva,

don t panic and be aware that the available integrated peripherals like like comparators are a key feature of growing uC power.

And also extensive timer hardware which can be configured to work as a fast cycle by cycle control, running independend from the MCU. It seems you are already using your uC this way, why do you fight this reasoning?

Hi Tom,

regarding power peaks: It is a trade off between required pulse power, time, costs, psu architecture and size. Moving more and more away from large caps towards improved architecture and control of the power electronics is the natural design direction. I guess you wanted to say this, but somehow said something else...?

don t panic and be aware that the available integrated peripherals like like comparators are a key feature of growing uC power.

And also extensive timer hardware which can be configured to work as a fast cycle by cycle control, running independend from the MCU. It seems you are already using your uC this way, why do you fight this reasoning?

Hi Tom,

regarding power peaks: It is a trade off between required pulse power, time, costs, psu architecture and size. Moving more and more away from large caps towards improved architecture and control of the power electronics is the natural design direction. I guess you wanted to say this, but somehow said something else...?

I would like to R&D more uC projects in this area, such as real time monitoring and power conversion, but life, on my side is hell busy so I can only play the observer role at moment in time.

Perhaps we should start a open source project here?, I have already made a plan to replace ChocoHolic gain stage for he`s D amplifier and use a signal controller to perform misc tasks such as limiting, supervision monitoring such as temp, osc frequency and other supervisory tasks in code, its really really easy, and can do done with a *any* uC take your pic, and the ticks employed are far from esoteric... at the moment I have a 8-channel SHARC dsp project on my desk I want to complete first, so far I successfully booted the device, made a PCB however my relationship with it is occasional.

ChocoHolic

About the comparators, some have internal vref and others don`t, Eva does have a point in this regard, however it depends what the problem is one is trying to solve. The Ti modules have eCap modules that offers extremely tight pulse control and various pwm counter ticks and ramp detection features (its very feature rich and eons ahead of any PIC), I only had a few weeks to flirt with it, I was VERY impressed with the signal controllers capability.

Perhaps we should start a open source project here?, I have already made a plan to replace ChocoHolic gain stage for he`s D amplifier and use a signal controller to perform misc tasks such as limiting, supervision monitoring such as temp, osc frequency and other supervisory tasks in code, its really really easy, and can do done with a *any* uC take your pic, and the ticks employed are far from esoteric... at the moment I have a 8-channel SHARC dsp project on my desk I want to complete first, so far I successfully booted the device, made a PCB however my relationship with it is occasional.

ChocoHolic

About the comparators, some have internal vref and others don`t, Eva does have a point in this regard, however it depends what the problem is one is trying to solve. The Ti modules have eCap modules that offers extremely tight pulse control and various pwm counter ticks and ramp detection features (its very feature rich and eons ahead of any PIC), I only had a few weeks to flirt with it, I was VERY impressed with the signal controllers capability.

Attachments

Last edited:

"Hi Tom,

regarding power peaks: It is a trade off between required pulse power, time, costs, psu architecture and size. Moving more and more away from large caps towards improved architecture and control of the power electronics is the natural design direction. I guess you wanted to say this, but somehow said something else...?"

A trade-off, yes, but most designers are greedy and do not spend some extra dollars for electrolytics. You cannot really move away from large caps because there is always the zero crossing of the AC, where you have to have some significant caps somewhere, be it primary-side or secondary-side. The more storage you have, the easier it gets to make the consumption current more sinusoidal even in case of load steps, e. g. keeping good PF.

Remember that the class D inverter will always draw power at twice the signal frequency and that the peak power is 2 times average power in case of resistive load and even more times in case of general, not purely-resistive load).

If the peaks are covered by the electrolytics (down to a certain sensible "trade-off" frequency of course), you can get away with a PSU supplying average powe., If not, the PSU must in addition be able to cover the peak power. Better still, if the PSU is able to cover the peak power and is most times not even requested to do so (power headroom).

A power supply optimized to be kept mostly at a certain "medium" load range with rare occasions of full load or no load will usually have less overall losses (heat) than a PSU that has to jump between no load and full load constantly.

regarding power peaks: It is a trade off between required pulse power, time, costs, psu architecture and size. Moving more and more away from large caps towards improved architecture and control of the power electronics is the natural design direction. I guess you wanted to say this, but somehow said something else...?"

A trade-off, yes, but most designers are greedy and do not spend some extra dollars for electrolytics. You cannot really move away from large caps because there is always the zero crossing of the AC, where you have to have some significant caps somewhere, be it primary-side or secondary-side. The more storage you have, the easier it gets to make the consumption current more sinusoidal even in case of load steps, e. g. keeping good PF.

Remember that the class D inverter will always draw power at twice the signal frequency and that the peak power is 2 times average power in case of resistive load and even more times in case of general, not purely-resistive load).

If the peaks are covered by the electrolytics (down to a certain sensible "trade-off" frequency of course), you can get away with a PSU supplying average powe., If not, the PSU must in addition be able to cover the peak power. Better still, if the PSU is able to cover the peak power and is most times not even requested to do so (power headroom).

A power supply optimized to be kept mostly at a certain "medium" load range with rare occasions of full load or no load will usually have less overall losses (heat) than a PSU that has to jump between no load and full load constantly.

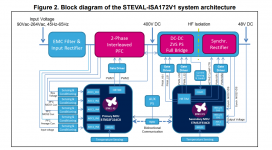

Here is an example of a open 2 kW fully digital AC - DC power supply using two 32-bit STM32F3 microcontrollers. The information serves a good literature one of many on the net on this topic.

http://www.st.com/st-web-ui/static/...ical/document/application_note/DM00241974.pdf

http://www.st.com/st-web-ui/static/...ical/document/application_note/DM00241974.pdf

Attachments

Choco:

In non-trivial converters the comparators also need DACs with flexible I/O wiring for scaling reference voltages. Op-amps are usually required to buffer the DACs and make current sources. In a PFC the conductance adjustment usually ends up needing a DAC. In most chips there are no such features. Particularly some chips are designed from the assumption that everything must go through ADC/math/PWM. Re-reading may be useful. Additionally, in complex converters with more than 2 strokes (switch states) there is a need for sequencing PWM control modules, each module allowing to blank the comparators or timers of others, that in some chips is just not possible at all without lots of external masking logic. The people designing the chips have little or no idea of the problems that have to be solved to control converters really optimized for low part count and low natural resource usage.

Reactance:

During development I thought my solution was a bit high on the part count side, since the control circuit uses about 70 parts and the power section about another 30, all mostly small parts, only 2 big magnetics, but then I saw this PDF and noticed that they use far more parts, particularly more big and costly parts, 7 big magnetics.

This is a great example that proves my point of view. No real improvement in SMPS with these new DSP chips, not even cost improvement. No advantage at all in using a DSP to simulate an op-amp and a comparator doing an average current loop. And simulating more complex control eats MSPS and MIPS far above the capability of low cost chips.

In non-trivial converters the comparators also need DACs with flexible I/O wiring for scaling reference voltages. Op-amps are usually required to buffer the DACs and make current sources. In a PFC the conductance adjustment usually ends up needing a DAC. In most chips there are no such features. Particularly some chips are designed from the assumption that everything must go through ADC/math/PWM. Re-reading may be useful. Additionally, in complex converters with more than 2 strokes (switch states) there is a need for sequencing PWM control modules, each module allowing to blank the comparators or timers of others, that in some chips is just not possible at all without lots of external masking logic. The people designing the chips have little or no idea of the problems that have to be solved to control converters really optimized for low part count and low natural resource usage.

Reactance:

During development I thought my solution was a bit high on the part count side, since the control circuit uses about 70 parts and the power section about another 30, all mostly small parts, only 2 big magnetics, but then I saw this PDF and noticed that they use far more parts, particularly more big and costly parts, 7 big magnetics.

This is a great example that proves my point of view. No real improvement in SMPS with these new DSP chips, not even cost improvement. No advantage at all in using a DSP to simulate an op-amp and a comparator doing an average current loop. And simulating more complex control eats MSPS and MIPS far above the capability of low cost chips.

Last edited:

Reactance:

During development I thought my solution was a bit high on the part count side, since the control circuit uses about 70 parts and the power section about another 30, mostly small parts, only 2 big magnetics, but then I saw this PDF and noticed that they use far more parts, particularly more big and costly parts, 7 big magnetics.

This is a great example that proves my point of view. No real improvement in SMPS with these new DSP chips, not even cost improvement. No advantage at all in using a DSP to simulate an op-amp and a comparator doing an average current loop. And simulating more complex control eats MSPS and MIPS far above the capability of low cost chips.

Don`t you think these companies deliberately force extra complexity to market their parts, don`t forget that aspect as well.

Essentially I think they are running ahead without a head.

Just a question: the device measuring power what instrument is that? I still see you using that old hantek scope.. how do you even do real time serial protocol decoding ? dont tell me you eye balling the scope? you using a HV differential probe for your scope if not what probe, I am unable to find a cheap probe to experiment with offline mains smps.

You need a realtime serial decoding scope to design a SMPS?

Damn, all this time I've done it, I've been just doing things like probing switching nodes and control loop bits.

Damn, all this time I've done it, I've been just doing things like probing switching nodes and control loop bits.

You need a realtime serial decoding scope to design a SMPS?

Damn, all this time I've done it, I've been just doing things like probing switching nodes and control loop bits.

no silly, she probably does comms stuff, like supervisory analysis, she did say she wrote custom protocols ... nothing to do with. SMPS design. 😛..

Last edited:

And there are reasons how and where and with which topologies it is more fortunate to handle this storage.... there is always the zero crossing of the AC, where you have to have some significant caps somewhere...

Please don't get me wrong, for multiple reasons I am not voting for exzessively small caps, but it is worth to spend some efforts in loop control and catching the demand of lower frequency contents of the music signal with the power electronics, not with the caps.

For reference I am attaching a load step measurement of one of my early DIY PSU designs.

It was a trade off and had significant amount of output caps. In fact 2x3300uF at +/-59V for a max. power of 1400W for 10s and continuosly allowing a 33% load duty cycle with 1kW.

In case of a 1kW load step the output voltage drops just 0.7%, with an undershoot of just 0.2% for roughly 300us. Stepping back to zero load results in a blameless 200us slope.

At the same time this design can compensate an input voltage drop to approx. 50% of its nominal value. For such a behavior already a simple linear first order control loop does the job.

For comparison: Catching the low frequencies by the caps with just 0.7% voltage drop would ask for approximately 2x 250 000 uF instead of 2x 3300uF. Reducing cap size almost by factor 100 with just moderate efforts in the power electronics and very low efforts in the control loop - that's worth it and usually will overrule some few single % difference in efficacy.

The screen shot is showing multiple load steps between zero load and 1kW.

White trace is the +59V rail, measurement DC coupled: 20V / Grid

Red trace is the AC component of +59V rail: 200mV / Grid

Time base: 1ms / Grid

Nice try in social engineering..Choco:

In non-trivial converters the comparators also need ...

But you won't get me to the point that I specify here my uC needs and reasonings why I need which specific feature.

But you won't get me to the point that I specify here my uC needs and reasonings why I need which specific feature.Attachments

For reference I am attaching a load step measurement of one of my early DIY PSU designs.

feature.

This thread is going crazy with all kinds of things. nothing on point but at the same time interesting stuff show up every where....

- Status

- Not open for further replies.

- Home

- Amplifiers

- Class D

- Some people wonders: Can class D do the power advertised?