Hi everyone,

I'm designing a new dac for my cd-pro2 drive. I will feed the dac directly with i2s coming out from the cd-pro2, thus avoiding the i2s/spdif and spdif/i2s conversion.

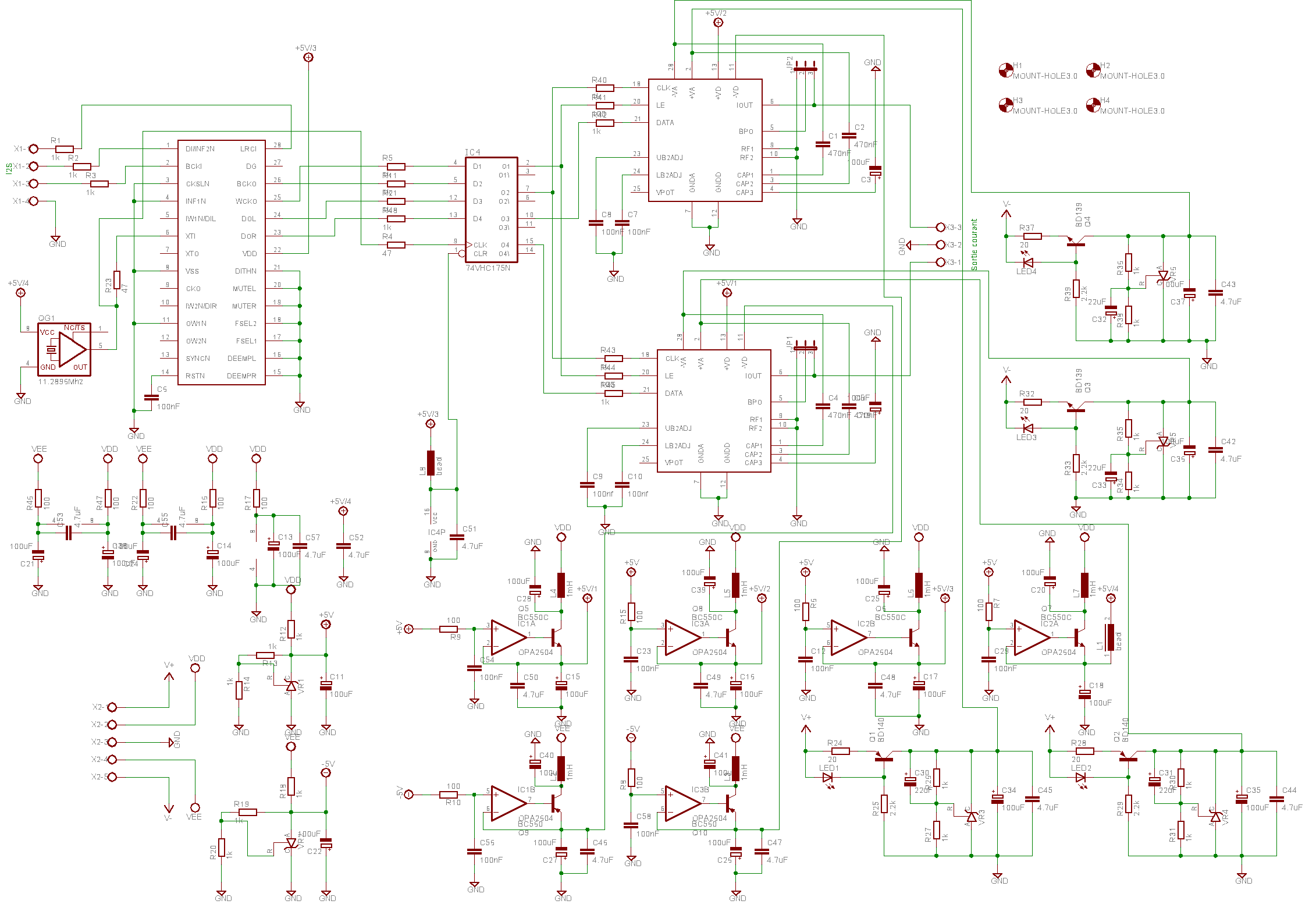

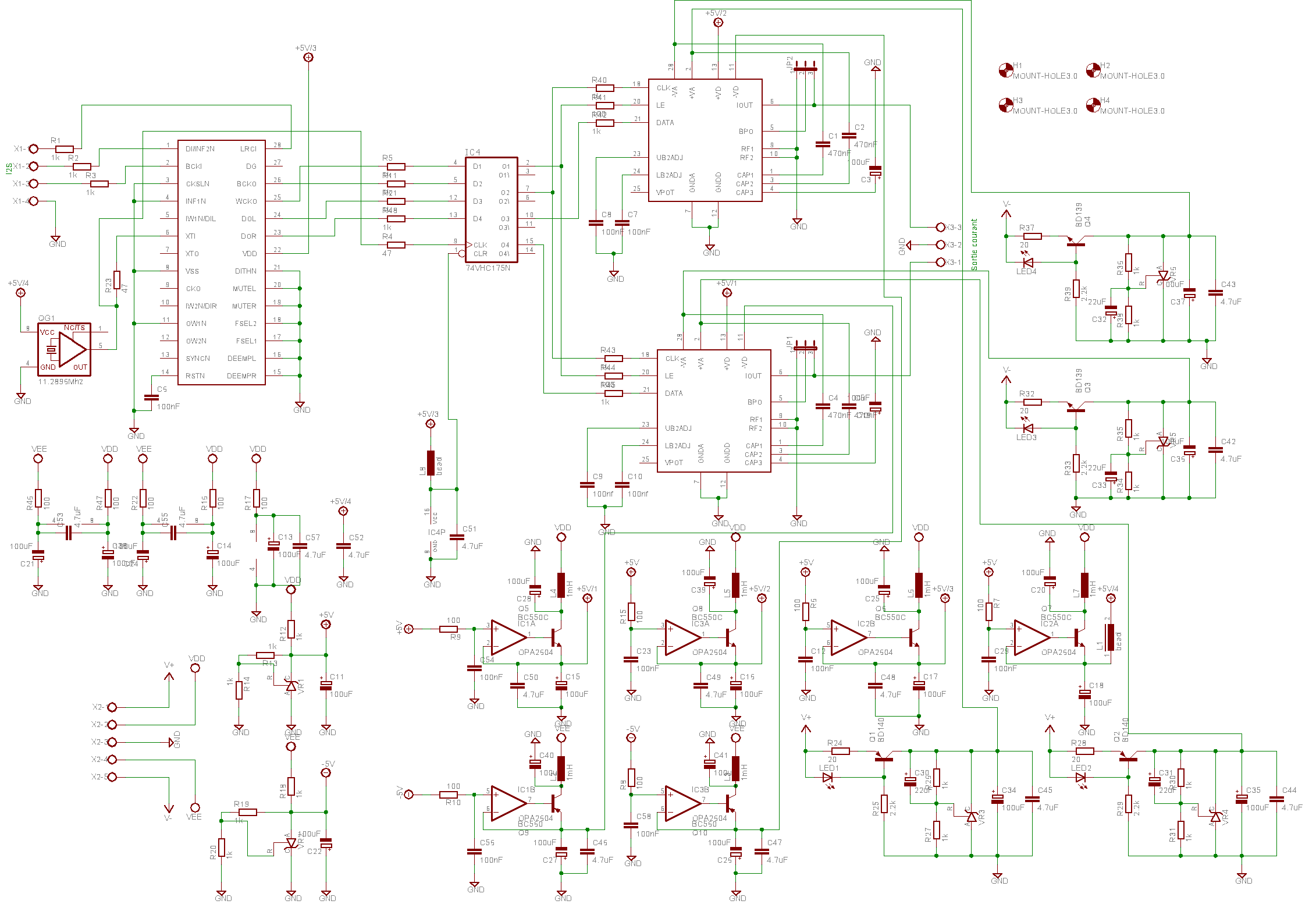

here's the schematic:

http://belinfabien.free.fr/dac/pcm63/pcm63.png

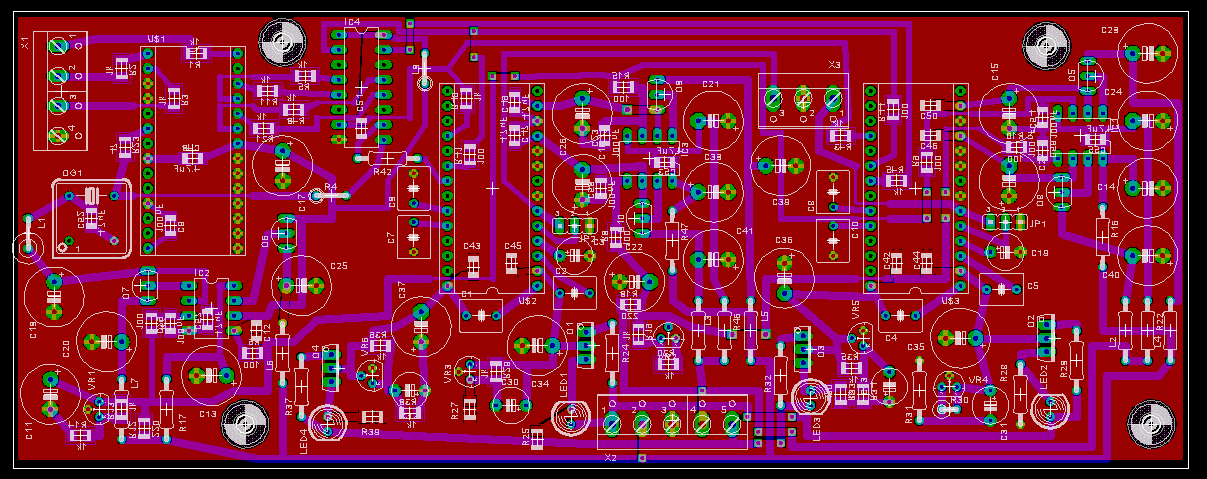

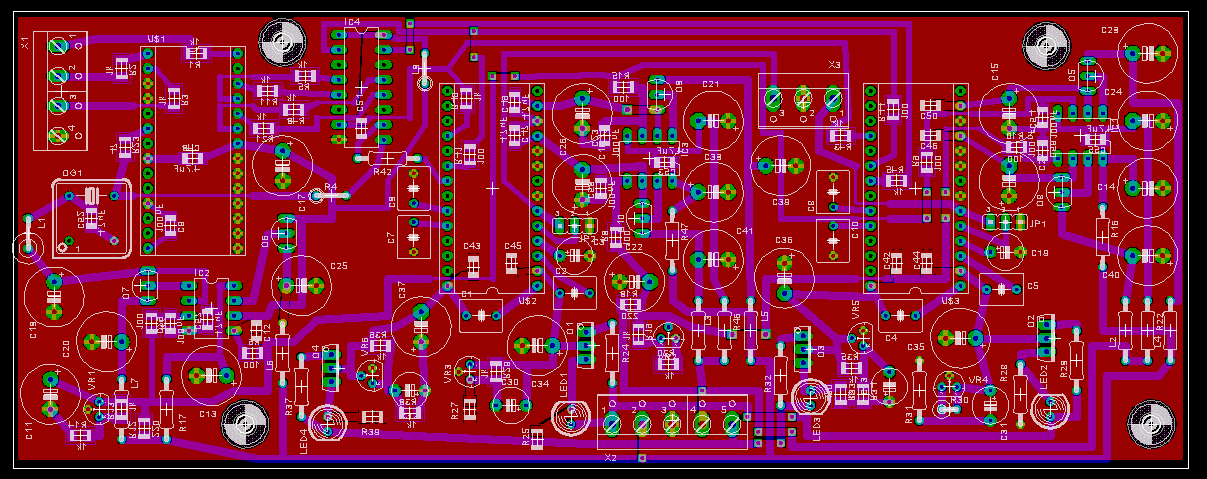

the pcb:

http://belinfabien.free.fr/dac/pcm63/typon pcm63.png

the eagle files:

http://belinfabien.free.fr/dac/pcm63/eagle/

please comment. I took example on doede dac1 but using pcm63, like in guido tent's dac.

I'm designing a new dac for my cd-pro2 drive. I will feed the dac directly with i2s coming out from the cd-pro2, thus avoiding the i2s/spdif and spdif/i2s conversion.

here's the schematic:

http://belinfabien.free.fr/dac/pcm63/pcm63.png

the pcb:

http://belinfabien.free.fr/dac/pcm63/typon pcm63.png

the eagle files:

http://belinfabien.free.fr/dac/pcm63/eagle/

please comment. I took example on doede dac1 but using pcm63, like in guido tent's dac.

You might wonder why no body is reacting here 😕

There are many threads with hundreds of dicussions on many parts of the design you showed us here, like power supply, the way you designed your pcb, the digital filter vs NOS etc etc....

Still no reactions. I am puzzled too. I did look at the design and what came to mind is that it is evident you have spent a great deal on the power supply, which I think is important too.

Though a few questions:

You are using small coils to filter thze power supply. Have you considered to use them at the output to the IC's to make sure the IC sees high impedance towards to the power supply?

Are you using a low Jitter clock, like the Tent or so? This makes a difference too.

I see no termination of the Output from the PCM63. How are you terminating? I expect passive I/V ?

What type of Electrolytes are you using ? BG's or similar or normal stock ? Here gain is to be made...

For the rest this for sure will be a good sounding DAC, regardless of small details, my experience is, that this combination just sound very good.

Hope you will get some other inputs too 😎

Doede

There are many threads with hundreds of dicussions on many parts of the design you showed us here, like power supply, the way you designed your pcb, the digital filter vs NOS etc etc....

Still no reactions. I am puzzled too. I did look at the design and what came to mind is that it is evident you have spent a great deal on the power supply, which I think is important too.

Though a few questions:

You are using small coils to filter thze power supply. Have you considered to use them at the output to the IC's to make sure the IC sees high impedance towards to the power supply?

Are you using a low Jitter clock, like the Tent or so? This makes a difference too.

I see no termination of the Output from the PCM63. How are you terminating? I expect passive I/V ?

What type of Electrolytes are you using ? BG's or similar or normal stock ? Here gain is to be made...

For the rest this for sure will be a good sounding DAC, regardless of small details, my experience is, that this combination just sound very good.

Hope you will get some other inputs too 😎

Doede

Hi dddac,

Thanks for your reply !

for the psu I'll use coils between the global psu (about 10-12v) and the regulators to avoid switching noise to polluate it. Since I have a regulator per IC, I thought it wasn't necessary to put coils in it. If you say it'll better, I'll add it.

At least I can make place for it on the pcb and strap if it isnt't better.

For the clock, I will use a tentlabs XO.

for the I/V stage, I have 2 separates boards to test. One is super-pair I/V and the other is a tntaudio output stage with passive I/V + amplification.

the schematic is here: http://www.tnt-audio.com/clinica/tnt1541_e.html

The electrolytics will be bc136 or os-con I think.

I saw that you've build a pcm63p dac too. How does it sound compared to tda1541 ?

thanks

Thanks for your reply !

for the psu I'll use coils between the global psu (about 10-12v) and the regulators to avoid switching noise to polluate it. Since I have a regulator per IC, I thought it wasn't necessary to put coils in it. If you say it'll better, I'll add it.

At least I can make place for it on the pcb and strap if it isnt't better.

For the clock, I will use a tentlabs XO.

for the I/V stage, I have 2 separates boards to test. One is super-pair I/V and the other is a tntaudio output stage with passive I/V + amplification.

the schematic is here: http://www.tnt-audio.com/clinica/tnt1541_e.html

The electrolytics will be bc136 or os-con I think.

I saw that you've build a pcm63p dac too. How does it sound compared to tda1541 ?

thanks

I've updated schematic and pcb. I made a ground plate on top with max surface and route the signals on the bottom.

it should be ok now...

any comments ?

it should be ok now...

any comments ?

apolon34 said:Hi everyone,

I'm designing a new dac for my cd-pro2 drive. I will feed the dac directly with i2s coming out from the cd-pro2, thus avoiding the i2s/spdif and spdif/i2s conversion.

Do you have a controller for the CD Pro2 DSA interface ?

apolon34 said:yes, i use a pic 18f452 to control the cd-pro2, IR and a VFD display.

I assume then you can change the default digital audio format of the module as the SM5842 does not accept I2S as an input format.

I thought it would take I2S directly...

the sm5842 datasheet says, when inf1n is low, that it accepts "LR alternating, trailing data".

IW1n and IW2N are high so it accepts 16 bits input.

i2s seems right or did I made a mistake ?

thanks

the sm5842 datasheet says, when inf1n is low, that it accepts "LR alternating, trailing data".

IW1n and IW2N are high so it accepts 16 bits input.

i2s seems right or did I made a mistake ?

thanks

I looked deeper and it seems that you're right.

According to the sm5842 datasheet, it can input i2s (LR alternating, leading data) by puting Inf1n high and inf2n low.

After that, I should hook up the input data to DIL and DIR simultaneously, right ?

If I do so, the input length goes to 24 bits. If the cd-pro2 outputs only 16 bits data, is it a problem as, if I remember well, i2s always outputs 32 bits, filling with zeros ?

thanks rboer for finding this out, I didn't looked at it enough !

According to the sm5842 datasheet, it can input i2s (LR alternating, leading data) by puting Inf1n high and inf2n low.

After that, I should hook up the input data to DIL and DIR simultaneously, right ?

If I do so, the input length goes to 24 bits. If the cd-pro2 outputs only 16 bits data, is it a problem as, if I remember well, i2s always outputs 32 bits, filling with zeros ?

thanks rboer for finding this out, I didn't looked at it enough !

I2S Bus specification. http://www.semiconductors.philips.com/acrobat/various/I2SBUS.pdf

The SM5842 will not accept the above and it is also limited to 32/44/48 samples rates. That leaves three options, EIAJ CDROM mode, EIAJ 16bit and EIAJ 18bit. The EIAJ format is LSB justified or trailing data in the SM5842 datasheet. The SM5842 also allows one to select the input data wordlength. In your position, I would set the CD Pro to EIAJ 16bit and set the SM5842 to 16bit input data wordlength and LR alternating trailing data. If you are not using any of the digital processing functions the data should remain at 16bits.

The SM5842 will not accept the above and it is also limited to 32/44/48 samples rates. That leaves three options, EIAJ CDROM mode, EIAJ 16bit and EIAJ 18bit. The EIAJ format is LSB justified or trailing data in the SM5842 datasheet. The SM5842 also allows one to select the input data wordlength. In your position, I would set the CD Pro to EIAJ 16bit and set the SM5842 to 16bit input data wordlength and LR alternating trailing data. If you are not using any of the digital processing functions the data should remain at 16bits.

I'll use only 44.1khz as it's the sm5842 who'll do the oversampling.

I'll make a veroboard to test the different configurations cause I wanted to use it in i2s mode. If I can't, i'll just setup the cd-pro2 to output 16 bits eiaj

I'll make a veroboard to test the different configurations cause I wanted to use it in i2s mode. If I can't, i'll just setup the cd-pro2 to output 16 bits eiaj

apolon34 said:

I'll make a veroboard to test the different configurations cause I wanted to use it in i2s mode.

The SM5842 doesn't do I2S.

seems like you're right. Anyway, i'll just setup my cdpro2 to output 16 bits eiaj.

As suggested by guido, I added some reclocking on LE between the digital filter and the dacs.

I've updated schematic/pcb

As suggested by guido, I added some reclocking on LE between the digital filter and the dacs.

I've updated schematic/pcb

I've just finished the 2nd board version

here it is:

I've added some 100R/100nF filtering on the psu opamp's vref.

here it is:

I've added some 100R/100nF filtering on the psu opamp's vref.

I up the thread because I need some help with my dac.

here's the latest schematic:

the dac works well with my cd-pro2 drive, except that I got a click regularly, like an old turntable.

If I set the jitter free mode of the sm5842 off, the click comes more often.

Apart from that, it works well.

the psu's are ok, well regulated at 5v, without excessive noise.

To be sure, I removed the vhc175 and shunt the signals passing through. I also removed the series resistor but it's the same.

here's the latest schematic:

the dac works well with my cd-pro2 drive, except that I got a click regularly, like an old turntable.

If I set the jitter free mode of the sm5842 off, the click comes more often.

Apart from that, it works well.

the psu's are ok, well regulated at 5v, without excessive noise.

To be sure, I removed the vhc175 and shunt the signals passing through. I also removed the series resistor but it's the same.

Hi,

I can't do any of these, since the dac works in 11.2896 mhz and the drive with 33.8688.

The drive outputs 11.2896Mhz clock derivated from 33.8688, I could use it but I think it won't be optimum regarding to jitter.

a better solution is probably to multiply by 3 the dac clock to feed the drive, isn't it ?

what pll could I use to achieve this ?

thanks

I can't do any of these, since the dac works in 11.2896 mhz and the drive with 33.8688.

The drive outputs 11.2896Mhz clock derivated from 33.8688, I could use it but I think it won't be optimum regarding to jitter.

a better solution is probably to multiply by 3 the dac clock to feed the drive, isn't it ?

what pll could I use to achieve this ?

thanks

- Status

- Not open for further replies.

- Home

- Source & Line

- Digital Source

- sm5842 + 2xpcm63 dac