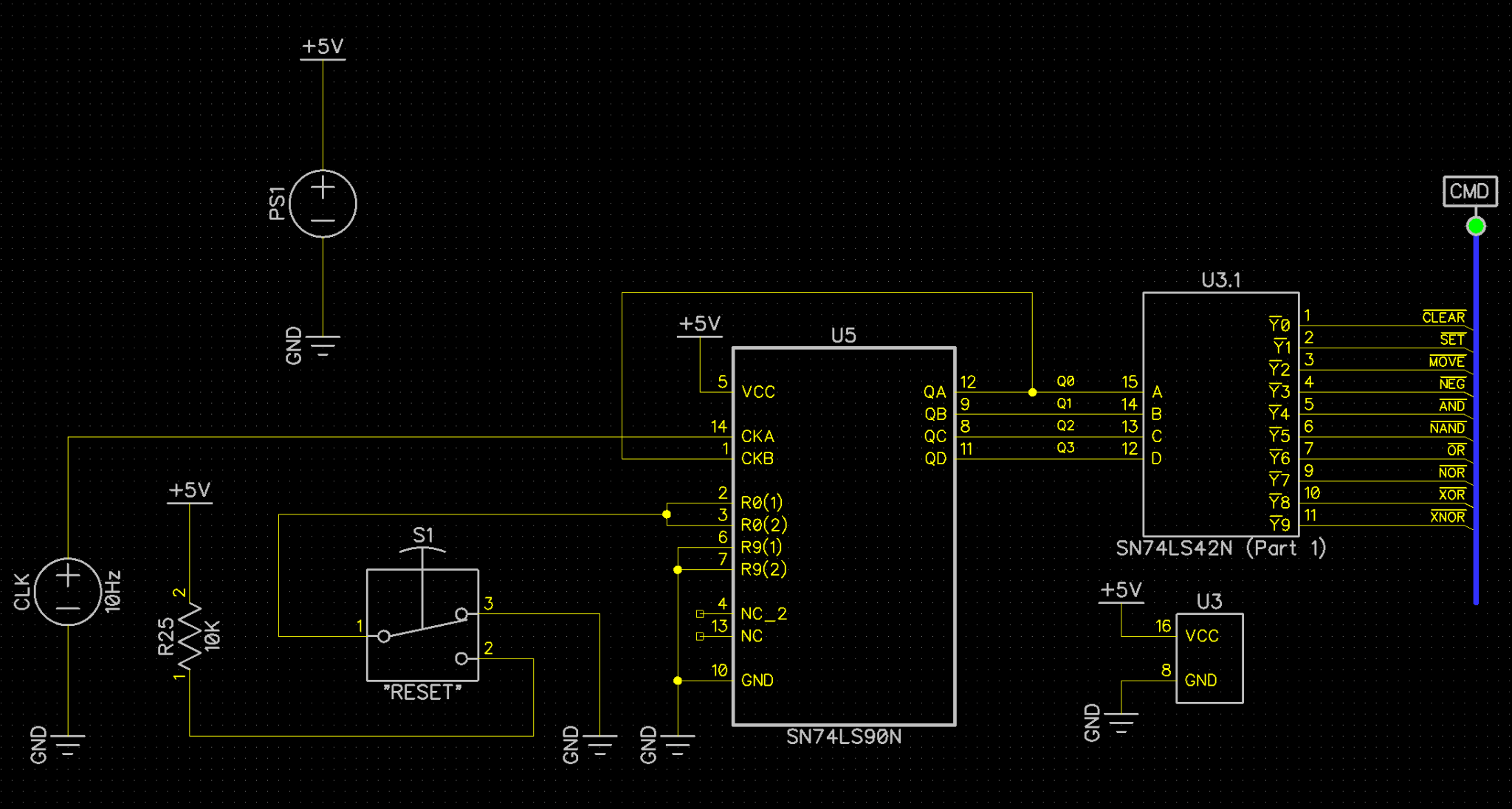

I have created a schematic, see the attached screenshot. Now I am trying to simulate how it works in a digital SPICE simulator (built-in DipTrace 5.0 beta).

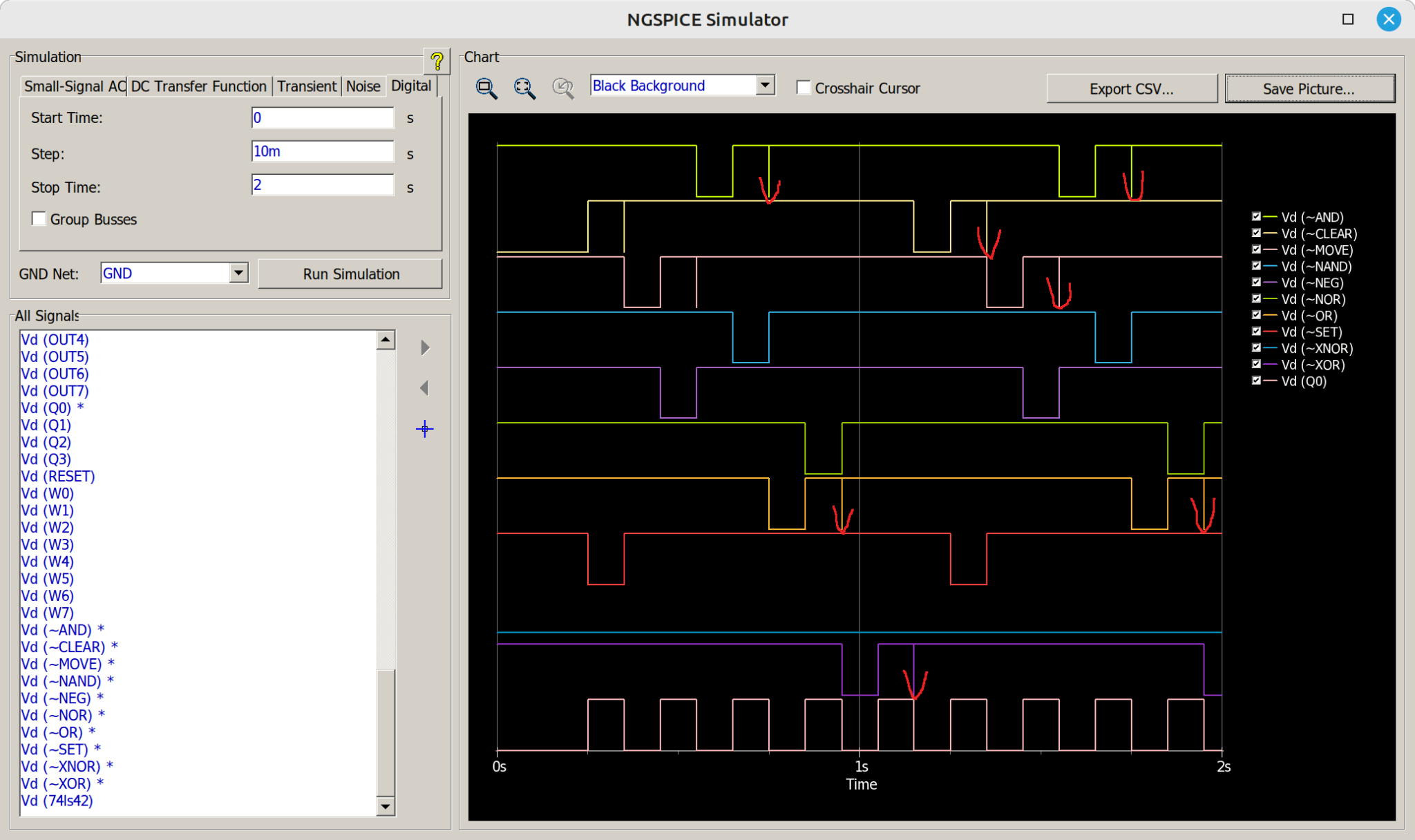

In general, it works almost reasonably. But there are strange signal distortions on some outputs of U3 on each falling edge of the clock coming to the input of decade counter U5. I have shown the problem with red marks.

What I am doing wrong? Is it a simulator issue or the schematic is incorrect?

In general, it works almost reasonably. But there are strange signal distortions on some outputs of U3 on each falling edge of the clock coming to the input of decade counter U5. I have shown the problem with red marks.

What I am doing wrong? Is it a simulator issue or the schematic is incorrect?

It seems that these are what is called glitches, when edges on one signal line cause crosstalk on another line.

I don't know this particular simulator, but if there is the option to set clock risetime or propagation delay, slow it down just a bit and it may be gone.

But note that if you build it, the construction, layout, PCB etc have a huge impact.

Maybe it does not appear in the real build, or you may be able to reduce it in simulation to get it re-appear when you build it.

Jan

I don't know this particular simulator, but if there is the option to set clock risetime or propagation delay, slow it down just a bit and it may be gone.

But note that if you build it, the construction, layout, PCB etc have a huge impact.

Maybe it does not appear in the real build, or you may be able to reduce it in simulation to get it re-appear when you build it.

Jan

Does the sim automatically add internal resistance to the 5 volt power source.

So considered non ideal source and would need power rail decoupling capacitor

like real world.

wild guess , unless sim settings.

Very nice you can sim the layout.

Need to try this software

So considered non ideal source and would need power rail decoupling capacitor

like real world.

wild guess , unless sim settings.

Very nice you can sim the layout.

Need to try this software

7490 is not a synchronous counter but an async where clock is mostly cascaded. In your implementation 10Hz ck is first divided by two by a Flip-Flop (CKA to QA) the QA is cascaded to CKB for by 5 divider whose outputs are QB, QC and QD. Internally, ck is cascaded from QB to CKC.

On an async counter outputs are not changing at the same time regarding the clock but after a small delay following the clock of the FF of each output. If clocks are cascaded, outputs will change in a cascaded way: one after one.

If time resolution of ngspice is low enough, it can catch those delays and display the corresponding glitch. You'll notice that your ~SET output (Red trace) is clean, red is QA which the output of the first FF clocked by 10HZ : there's no clock cascade on this signal.

To confirm or infirm this assumption, try a synchronous decade counter, such as 74LS160.

For digital logic (without HDL) simulations this software is very useful : https://github.com/logisim-evolution/logisim-evolution

On an async counter outputs are not changing at the same time regarding the clock but after a small delay following the clock of the FF of each output. If clocks are cascaded, outputs will change in a cascaded way: one after one.

If time resolution of ngspice is low enough, it can catch those delays and display the corresponding glitch. You'll notice that your ~SET output (Red trace) is clean, red is QA which the output of the first FF clocked by 10HZ : there's no clock cascade on this signal.

To confirm or infirm this assumption, try a synchronous decade counter, such as 74LS160.

For digital logic (without HDL) simulations this software is very useful : https://github.com/logisim-evolution/logisim-evolution

Attachments

Last edited: