Asgard said:

Yes that is true, but we are talking about sine waves and it's odd overtones. The steaper the rise time the higher the odd multiple, so you could say that only the really highest spectral components are subject to problems with impedance matching, the lower ones have long enough wavelength to not be subject to the workings of a transmission line (~1/4 wavelength according to textbooks). This is how I am educated, but I am always open for suggestions 🙂

Hi

reflections caused by higher frequency components affect the lower ones, including the SPDIF signal (timing)

EC8010 said:And, as was pointed out earlier, RCA phonos are not a terribly accurate 75 Ohm. A correctly fitted 75 Ohm BNC is better.

An RCA/cinch/phono is in the range of 35 ohm. I always propose to my customers to mount a 75 ohm BNC.

best

anatech said:Hi BlackCatSound,

Well then, if jitter is all that remains then a good PLL should take care of it, taking into account that the PLL itself does not generate jitter och that the clock would be bad. The only jitter-frequencies that a PLL has problems with (as I'm shure you know) are really low ones wich are least harmful.

I guess that the search goes on if you can blindly identifiy a SPDIF with low jitter after the receiver, I dont think I can anyway

hi,

Indeed, first of all the intrinsic jitter should be low. Then the PLL should do its job, and not add jitter above the cutoff frequency.

Low frequency jitter is very audible in my ears: What do you call "low" and what are your observations ?

best

Guido Tent said:

Low frequency jitter is very audible in my ears: What do you call "low" and what are your observations ?

You mean so called 'wander'? I always thought phase flustuations of say below 2Hz are completely insignificant. How does it affect sound in your view?

darkfenriz said:

You mean so called 'wander'? I always thought phase flustuations of say below 2Hz are completely insignificant. How does it affect sound in your view?

tonal stability (listening to a single piano tone will review these artifacts)

we are so used to listening to these using jittery converters that it is a revelation when you hear it done well (recording and playback !) you'll be amazed....

A good recording to try this is Channel Classics CCS SA 22605

best

PMA:

1kHz is very typical for PLLs, true, but not for all! A receiver like the CS8416 has a very poor jitter attenuation filter, with a cutoff starting at 4kHz and having a very flat slope from there (and actually has a GAIN of 2dB at 2-3kHz). Compare that with the popular ASRC AD1896 that many place after their SPDIF-receiver, it has a cutoff at 2Hz with high order attenuation.

Guido:

I don't have any exact figures but low frequency jitter should be very easy to simulate. Wouldn't such a plot confirm or sink your theory on "tonal balance" due to 1-10Hz jitter? Would be nice to verify this through simulation

1kHz is very typical for PLLs, true, but not for all! A receiver like the CS8416 has a very poor jitter attenuation filter, with a cutoff starting at 4kHz and having a very flat slope from there (and actually has a GAIN of 2dB at 2-3kHz). Compare that with the popular ASRC AD1896 that many place after their SPDIF-receiver, it has a cutoff at 2Hz with high order attenuation.

Guido:

I don't have any exact figures but low frequency jitter should be very easy to simulate. Wouldn't such a plot confirm or sink your theory on "tonal balance" due to 1-10Hz jitter? Would be nice to verify this through simulation

Asgard said:PMA:

1kHz is very typical for PLLs, true, but not for all! A receiver like the CS8416 has a very poor jitter attenuation filter, with a cutoff starting at 4kHz and having a very flat slope from there (and actually has a GAIN of 2dB at 2-3kHz). Compare that with the popular ASRC AD1896 that many place after their SPDIF-receiver, it has a cutoff at 2Hz with high order attenuation.

Guido:

I don't have any exact figures but low frequency jitter should be very easy to simulate. Wouldn't such a plot confirm or sink your theory on "tonal balance" due to 1-10Hz jitter? Would be nice to verify this through simulation

Hi

The analog PLL in our DAC has a cutoff of about 3Hz (first pole), the digital PLLs are much slower.

Yes, simulation is nice, but what would you do with the result ?

best

Guido Tent said:

The analog PLL in our DAC has a cutoff of about 3Hz (first pole), the digital PLLs are much slower.

Yes, simulation is nice, but what would you do with the result ?

best

Hehe, not much I guess since not many people would care about it. But personally it would give some more intuition to what actually matters and what doesn't in HiFi 😀

By the way, AD1896 uses a digital PLL with 2Hz cutoff with -20dB supression @ 10Hz, -60dB @ 100Hz, -100dB @ 1kHz, -160dB @ 10kHz

Sounds stable as hell

Asgard said:

Hehe, not much I guess since not many people would care about it. But personally it would give some more intuition to what actually matters and what doesn't in HiFi 😀

By the way, AD1896 uses a digital PLL with 2Hz cutoff with -20dB supression @ 10Hz, -60dB @ 100Hz, -100dB @ 1kHz, -160dB @ 10kHz

Sounds stable as hell

Hi

SRCs are not my cup of tea. By the way our Grimmaudio CC1 achieves better results

http://www.grimmaudio.com/cc1grimm.htm

best

Guido Tent said:

Yes, a whopping -60dB @ 10Hz, that's a more narrow PLL than AD1896, good work! (Stylish chassi too 😉.

Still, regarding DIY and low cost, an SO-28 IC for a couple of $ isn't that bad 😀 (and perhaps overkill for my non-golden ears)

Having an uber stable worldclock is only half way there, you're still relying on the PLLs in everything else to sync to this magic clock.

-160dBc at 10k is good, I'm more used to -90dBc at 10k, but then that is at 2.5GHz 🙂

-160dBc at 10k is good, I'm more used to -90dBc at 10k, but then that is at 2.5GHz 🙂

BlackCatSound said:Having an uber stable worldclock is only half way there, you're still relying on the PLLs in everything else to sync to this magic clock.

-160dBc at 10k is good, I'm more used to -90dBc at 10k, but then that is at 2.5GHz 🙂

Tom

The spec is about the suppression of the PLL, the units are dB, bot dBc

Yes, internal PLLs can decrease performance when the internal clock isn't as good as the external. in that case a wide bandwidth in the everything else equipment helps.

best

BlackCatSound said:So whats the dBc of your actual clock at 10khz?

I don't measure that, I measure the jitter.

best

BlackCatSound said:Do you do any phase noise measurements?

you've asked me that before

best

Guido:

Should I take your answer to BlackCatSound as:

1. You don't have any measurements

2. You have measurements but don't want to share them

?

I too would be interesting in the numerical values of your experiments/findings

Should I take your answer to BlackCatSound as:

1. You don't have any measurements

2. You have measurements but don't want to share them

?

I too would be interesting in the numerical values of your experiments/findings

Asgard said:Guido:

Should I take your answer to BlackCatSound as:

1. You don't have any measurements

2. You have measurements but don't want to share them

?

I too would be interesting in the numerical values of your experiments/findings

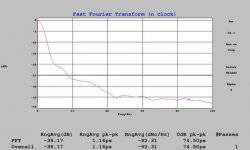

I don't measure phase noise. Here are my jitter results.

best

Attachments

BlackCatSound said:So whats the dBc of your actual clock at 10khz?

Cannot understand why dBC is used. This attenuates hf.

- Status

- Not open for further replies.

- Home

- Source & Line

- Digital Source

- S/PDIF Jitter: Myth or Reality?