Hi all,

I do dot know if this has been already done...

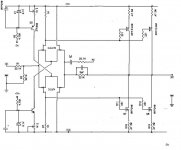

Derivated from the Aleph j schematic:

Taking the lower half of it and drawing its symetrical as upper half.

I think it should work, though a question remains to me about the feedback: Do we need a leg to ground at the inverting input? (Jfets gate)

I do dot know if this has been already done...

Derivated from the Aleph j schematic:

Taking the lower half of it and drawing its symetrical as upper half.

I think it should work, though a question remains to me about the feedback: Do we need a leg to ground at the inverting input? (Jfets gate)

Attachments

Last edited:

already done , and even not just by Papa

dunno where was that posted , few years ago

anyway - F5 is practically same ........ with Spice ( and I'm not meaning on sim prog )

dunno where was that posted , few years ago

anyway - F5 is practically same ........ with Spice ( and I'm not meaning on sim prog )

To answer the question, a matching resistor to ground would

give the circuit a better CMRR on the balanced input.

😎

give the circuit a better CMRR on the balanced input.

😎

- Status

- Not open for further replies.