Kuei Yang Wang said:Hi,

Doubtful.

AN has used Non-OS AD1865 in their CD Players and DAC's since the late 90's and they put quite a bit of volume, especially of the cheaper stuff.

Nos, albeit for rather more pragmatic reasons, was around long before AN's efforts.

Audible it is not, under normal conditions.

Well, thats one view.

I've had some experience with this topic over the last few days. I've been trying different DAC chips with the I2S output from a 2706 USB chip, one thing I wanted t try was NOS with 56 and 1704s.

The first approach used some shift registers and the inverter to drive the 56s, this gives the infamous 1/2 sample offset. The circuit is not nearly as simple as with a 8412 because the I2S is left justified and the DAC chips are right justified, some shifting has to be done.

I then tried a full blown shifter implemented in a small FPGA that properly aligned both channels so they were clocked into the DACs at the same time. In this case I resynched the signals with 74HC flops using the sysclock from the 2706.

The second implementation using the FPGA sounds significantly better than the first. I'm not sure if its because of the allignment or the reclocking though.

BTW in both circuits the 1704s sound much better than the 56s, and thats feeding 16bit data into both, seems kind of a waste for the 1704, but it really does sound better.

John S.

The first approach used some shift registers and the inverter to drive the 56s, this gives the infamous 1/2 sample offset. The circuit is not nearly as simple as with a 8412 because the I2S is left justified and the DAC chips are right justified, some shifting has to be done.

I then tried a full blown shifter implemented in a small FPGA that properly aligned both channels so they were clocked into the DACs at the same time. In this case I resynched the signals with 74HC flops using the sysclock from the 2706.

The second implementation using the FPGA sounds significantly better than the first. I'm not sure if its because of the allignment or the reclocking though.

BTW in both circuits the 1704s sound much better than the 56s, and thats feeding 16bit data into both, seems kind of a waste for the 1704, but it really does sound better.

John S.

Easy answer, if both channels sound equally better is is because you improved the clock - if only one channel is better is is due to the alignment, since by the logic of those that believe the time alignment is the culprit in a degredation in the sound, the other channel was already fine.

hi all,

so sorry to disturb U.

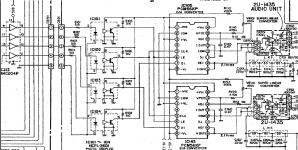

this was my old job before I sick. I will start to produce for it. I hold this will be another cheap version, slim size dac for diyers.

take a look for the PCB,

upgrade for this dac was

8414 to Dir9100.

large value electro-caps

upgrade better oscillator & 74HC04.

parallel PCM 56 chips.

very small size because power supply will use note book transformer power supply 18V.

thx

thomas

so sorry to disturb U.

this was my old job before I sick. I will start to produce for it. I hold this will be another cheap version, slim size dac for diyers.

take a look for the PCB,

upgrade for this dac was

8414 to Dir9100.

large value electro-caps

upgrade better oscillator & 74HC04.

parallel PCM 56 chips.

very small size because power supply will use note book transformer power supply 18V.

thx

thomas

Attachments

The PCM56, if MJ is anything to go by, is indeed very common in Japan but the TDA based nos dacs, commercially at any rate, outnumber the AD1865 ones, but I digress. The point is that removing the delay is not inherently a bad thing or as deleterious as portrayed not to mention the fact the stopped clock method has considerably less data jitter than any other method.

The stopped clock circuit is in the AD1856 datasheet. figure 14.

ad1856 datasheet and Application Note, Data Sheet, Circuit, PDF, Pinout | Datasheet Archive

- Status

- Not open for further replies.