Hi all,

After lurking a lot and being overwhelmed by the strong knoledge of the users of this forum, I'm going to ask you a question 🙂

I am designing my first DAC and I have a 24 bit Right-Justified stream as PCM1704 likes to see at its input. Data come from an AD1896 through an insulator from digital to analog section.

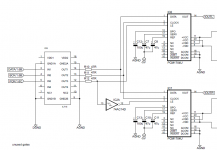

Now I am going to split the DOL and DOR with a quite rought way using a Schmitt-Trigger (does it make sense to use a S-T?) inverter. Please refer to my schematic.

My big question is: due to the fact that the inverter is only on the frame clock I am going to add a propagation delay only on this line. Assuming to use Potato inverters we are speaking about 1.8nS in 15pF. Only on one channel.

Now I see that Potato also produce quite simple things like "delay elements": not inverting inverters LMAO.

http://www.potatosemi.com/potatosemiweb/datasheet/PO74G34A.pdf

Do you think it could be useful to place that delay elements thingy on all the lines to DACs in order to keep all the signals time-aligned? 😕

Many thanks guys and sorry for my bad English!

After lurking a lot and being overwhelmed by the strong knoledge of the users of this forum, I'm going to ask you a question 🙂

I am designing my first DAC and I have a 24 bit Right-Justified stream as PCM1704 likes to see at its input. Data come from an AD1896 through an insulator from digital to analog section.

Now I am going to split the DOL and DOR with a quite rought way using a Schmitt-Trigger (does it make sense to use a S-T?) inverter. Please refer to my schematic.

My big question is: due to the fact that the inverter is only on the frame clock I am going to add a propagation delay only on this line. Assuming to use Potato inverters we are speaking about 1.8nS in 15pF. Only on one channel.

Now I see that Potato also produce quite simple things like "delay elements": not inverting inverters LMAO.

http://www.potatosemi.com/potatosemiweb/datasheet/PO74G34A.pdf

Do you think it could be useful to place that delay elements thingy on all the lines to DACs in order to keep all the signals time-aligned? 😕

Many thanks guys and sorry for my bad English!

Attachments

Hi all,

After lurking a lot and being overwhelmed by the strong knoledge of the users of this forum, I'm going to ask you a question 🙂

I am designing my first DAC and I have a 24 bit Right-Justified stream as PCM1704 likes to see at its input. Data come from an AD1896 through an insulator from digital to analog section.

Now I am going to split the DOL and DOR with a quite rought way using a Schmitt-Trigger (does it make sense to use a S-T?) inverter. Please refer to my schematic.

My big question is: due to the fact that the inverter is only on the frame clock I am going to add a propagation delay only on this line. Assuming to use Potato inverters we are speaking about 1.8nS in 15pF. Only on one channel.

Now I see that Potato also produce quite simple things like "delay elements": not inverting inverters LMAO.

http://www.potatosemi.com/potatosemiweb/datasheet/PO74G34A.pdf

Do you think it could be useful to place that delay elements thingy on all the lines to DACs in order to keep all the signals time-aligned? 😕

Many thanks guys and sorry for my bad English!

Try Google search;

"pcm 1704 non-os dac"

and

"nos pcm1704 dac"

Nick

- Status

- Not open for further replies.