Hello

I need convert right justified i2s to left.

Did someone has expierience or find ready solution? The vest will be ready module with in out and pin to setup.

Regards

I need convert right justified i2s to left.

Did someone has expierience or find ready solution? The vest will be ready module with in out and pin to setup.

Regards

Wasn't that your question?

i2s has only right or left justified. Anything else is not i2s.

i2s has only right or left justified. Anything else is not i2s.

Attachments

Last edited:

Ok, my question was wrong.

I have i2s bus with pcm signal with 20bits right justified.

I can not change it in source, but reciver can not decode right, espect left.

How to change justified?

Chip ad1896 will be ok?

https://www.google.pl/url?q=http://...ABNsQFggPMAA&usg=AOvVaw0IqXMgWYWmRW3780kZ3EPZ

I have i2s bus with pcm signal with 20bits right justified.

I can not change it in source, but reciver can not decode right, espect left.

How to change justified?

Chip ad1896 will be ok?

https://www.google.pl/url?q=http://...ABNsQFggPMAA&usg=AOvVaw0IqXMgWYWmRW3780kZ3EPZ

Last edited:

Please check also this Dac page as it contains a lot of info:

http://www.pavouk.org/hw/audiosystem20/en_pcm1702dac.html

http://www.pavouk.org/hw/audiosystem20/en_pcm1702dac.html

Ok,sa what is the name of this bus?

It could be i2s frame or pcm, i wrote i2s bus (i know now that this signal is not i2s)?

About this chip upper, that no help?

It could be i2s frame or pcm, i wrote i2s bus (i know now that this signal is not i2s)?

About this chip upper, that no help?

There are multiple formats possible:

Offset binary, binary two's complement etc.

I guess in your case it is the last.

You will need to change the WS into LE. This is easy but also you need to get the LE in sync with the Data as well.

You can do this either delaying the Data or the LE.

Please see application note AN-207 from AD (is attached).

Offset binary, binary two's complement etc.

I guess in your case it is the last.

You will need to change the WS into LE. This is easy but also you need to get the LE in sync with the Data as well.

You can do this either delaying the Data or the LE.

Please see application note AN-207 from AD (is attached).

Attachments

Hi

What means LE?

And and what give invert WS,when i see on scope empty bits (0) on bouth state of ws (1 and 0) on left side of frame?

For l and r channels looks the same.

For different source (left justified) empty bits are on rigth side..(reference signal).

What means LE?

And and what give invert WS,when i see on scope empty bits (0) on bouth state of ws (1 and 0) on left side of frame?

For l and r channels looks the same.

For different source (left justified) empty bits are on rigth side..(reference signal).

Last edited:

Obviously you did not check any of the files and links i have provided.

I cant’t help you in this case.

Good luck with your project!

I cant’t help you in this case.

Good luck with your project!

Depends on..How many bits the source is? How many bits dac accepts? is this one chip stereo dac or dual mono. From here you can see how many bits to shift

Source has 20 bits out i can also setup 16 bits, destination has bit rate converter on the line, so anything get will be convert to correct frame readable for saa7706 dsp.

I tryed 16, 20, 24 bits and all format works well.

Only justified is required.

I tryed 16, 20, 24 bits and all format works well.

Only justified is required.

http://www.tij.co.jp/ods/images/SLAS965C/right_just_aud_data_for_SLAS965.gif

look here ,you have to be sure about physicaly coming out word clock lenght in bck.You can see this with ordinary osciloscope.There can come 16bits in 32bits word lenght frame left justified as an example.So in that case you have to shift 16bit if receiver can accept 32bit,if it accepts 24bits only so you shift 8bits. Many outcomes can be depending on the gear you have.

look here ,you have to be sure about physicaly coming out word clock lenght in bck.You can see this with ordinary osciloscope.There can come 16bits in 32bits word lenght frame left justified as an example.So in that case you have to shift 16bit if receiver can accept 32bit,if it accepts 24bits only so you shift 8bits. Many outcomes can be depending on the gear you have.

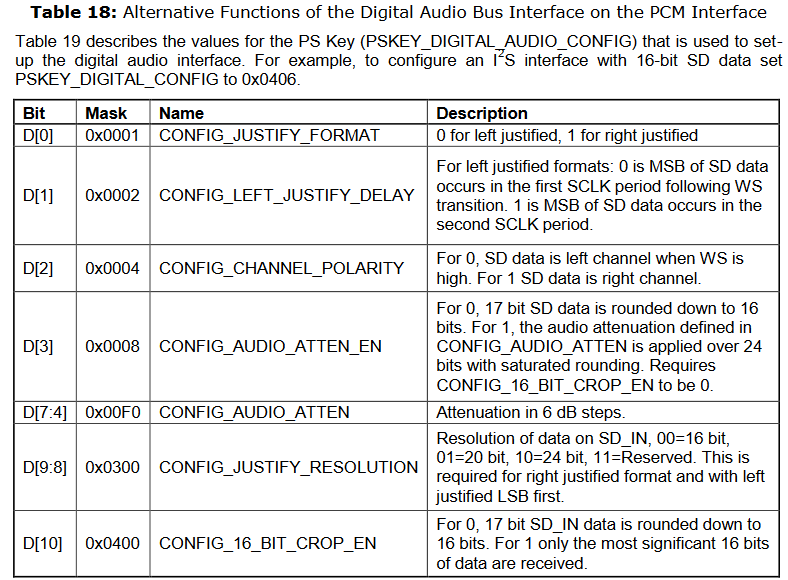

so why you need to convert from left to right justified outside if you can setup this in the D[0] bit??

ok, just explain.

i can setup in source bough of them and this is no problem.

for test my module, i need to test it with dac sebre ES9018K2M.

This dac support only right, on left justified do not work.

i have also PCM5102, not work also on left.

Before install module in target device, i like to test, but i can.

So, if i have some device, which convert to me to format i can setup source on final format and do not change it any more..( i have to desolder SPI socket on module after sending and better will be have ready setup and do not changing this).

For test i have also mp3 player with right justified...for now i can connect this mp3 to target also.

i can setup in source bough of them and this is no problem.

for test my module, i need to test it with dac sebre ES9018K2M.

This dac support only right, on left justified do not work.

i have also PCM5102, not work also on left.

Before install module in target device, i like to test, but i can.

So, if i have some device, which convert to me to format i can setup source on final format and do not change it any more..( i have to desolder SPI socket on module after sending and better will be have ready setup and do not changing this).

For test i have also mp3 player with right justified...for now i can connect this mp3 to target also.

- Status

- Not open for further replies.

- Home

- Source & Line

- Digital Line Level

- I2s format conventer needed.