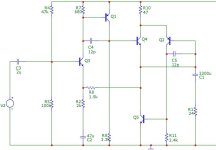

I don`t know who is author of this scheme, probably Sivasankar Chander 2008. Was posted here on diyaudio long time ago and probably was archived. Accidentally came across on this in my archive. What do you think? Constant Vce kills Miller effect and leads to significantly decrease non-linearity and intermodulation distortions.

High side transistor`s TDP just 75 mW => it`s possible to use very fast, low capacitance and high beta TO-92 devices. Low side device - something in TO-126 because of 700 mW TDP.

Looks better than simple 3-transistors design with barely the same BOM, posted here 3 years ago.

High side transistor`s TDP just 75 mW => it`s possible to use very fast, low capacitance and high beta TO-92 devices. Low side device - something in TO-126 because of 700 mW TDP.

Looks better than simple 3-transistors design with barely the same BOM, posted here 3 years ago.

Attachments

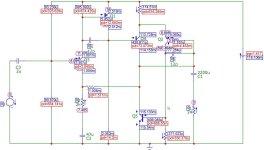

Interesting topology. It accounts for Miller, it simulates with high bandwidth, and should also deal with the Early effect. However my simulation suggested 0.1% or so at 1V amplitude 1kHz input with 12V supply and LTSpice's default NPN/PNP models. Lower amplitudes fare better of course.

If you want flat gain upto about 1MHz its a good performer, but audio doesn't need that. It strikes me its got to be a close relation of the series-shunt pair.

If you want flat gain upto about 1MHz its a good performer, but audio doesn't need that. It strikes me its got to be a close relation of the series-shunt pair.