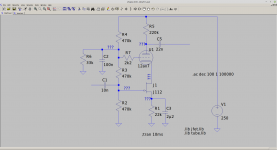

I have been without a proper phono stage for several months now after selling my integrated amplifier, so it is time to build one. Below is my first attempt at a MM phono stage design, after much reading, learning, and reviewing various schematics (inspired by SY's "His Master's Noise" MC phono stage, among others).

My cart is a MM Ortofon 2M Bronze with a 5mV nominal output. It is a two-gain stage "all-in-one" passive EQ with a source follower FET output buffer.

First stage is a triode-strapped D3a, cascode CCS loaded and IR LED biased with 1.2V on the cathode. Next is the RIAA stage optimized for a 1.9Kohm plate resistance of the D3a and the 49pF Miller capacitance of the 2C51.

The second gain stage is 1/2 of a 2C51 triode, also cascode CCS loaded and LED biased with a HLMP6000 with 1.6V on the cathode. Output buffer is an AOT1N60 FET with a IXCP10M45S current sink. Output cap is 1uF.

Power supply is not pictured, but it will be a Maida regulated B+ with a DC heater regulator for the D3a and 2C51.

Net gain at 1kHz is roughly 50dB.

So that is the gist of it, hoping for another set of eyes to see if I overlooked anything. Will I run into issues with the Miller capacitance of the D3a input with a MM cart? The recommended load capacitance of the 2M Bronze is 150-300pF, the Miller of the D3a is roughly 200pF.

Thanks for the feedback.

My cart is a MM Ortofon 2M Bronze with a 5mV nominal output. It is a two-gain stage "all-in-one" passive EQ with a source follower FET output buffer.

First stage is a triode-strapped D3a, cascode CCS loaded and IR LED biased with 1.2V on the cathode. Next is the RIAA stage optimized for a 1.9Kohm plate resistance of the D3a and the 49pF Miller capacitance of the 2C51.

The second gain stage is 1/2 of a 2C51 triode, also cascode CCS loaded and LED biased with a HLMP6000 with 1.6V on the cathode. Output buffer is an AOT1N60 FET with a IXCP10M45S current sink. Output cap is 1uF.

Power supply is not pictured, but it will be a Maida regulated B+ with a DC heater regulator for the D3a and 2C51.

Net gain at 1kHz is roughly 50dB.

So that is the gist of it, hoping for another set of eyes to see if I overlooked anything. Will I run into issues with the Miller capacitance of the D3a input with a MM cart? The recommended load capacitance of the 2M Bronze is 150-300pF, the Miller of the D3a is roughly 200pF.

Thanks for the feedback.

Last edited:

Yes, although not sure I believe the accuracy of the sim. With a 5mV input, 1kHz THD in LTSpice is 0.47% at 2VRMS output. In SY's design, which is a similar but MC stage with a Sowter step-up input transformer and ECC88 cathode follower output, he was seeing THD figures around 0.03% at 3Vrms output.

Yes, although not sure I believe the accuracy of the sim. With a 5mV input, 1kHz THD in LTSpice is 0.47% at 2VRMS output. In SY's design, which is a similar but MC stage with a Sowter step-up input transformer and ECC88 cathode follower output, he was seeing THD figures around 0.03% at 3Vrms output.

Is it possible to give your .asc file? Saves a lot of time for me to just copy and paste it into LTsiceXVII.

Version 4

SHEET 1 880 680

WIRE 176 -272 16 -272

WIRE 592 -272 176 -272

WIRE 176 -240 176 -272

WIRE 16 -192 16 -272

WIRE 176 -112 176 -160

WIRE 224 -112 176 -112

WIRE 432 -112 288 -112

WIRE -80 -80 -192 -80

WIRE 16 -80 16 -112

WIRE 16 -80 -80 -80

WIRE 176 -80 176 -112

WIRE -192 -64 -192 -80

WIRE -80 -48 -80 -80

WIRE 16 -32 16 -80

WIRE 32 -32 16 -32

WIRE 128 -32 112 -32

WIRE 16 16 16 -32

WIRE -192 48 -192 16

WIRE -80 48 -80 16

WIRE 208 96 208 16

WIRE -144 128 -288 128

WIRE -96 128 -144 128

WIRE 16 128 16 96

WIRE 16 128 -32 128

WIRE -288 160 -288 128

WIRE -144 160 -144 128

WIRE 16 160 16 128

WIRE 160 160 16 160

WIRE 16 208 16 160

WIRE 208 208 208 192

WIRE 288 208 208 208

WIRE 208 240 208 208

WIRE 592 240 592 -272

WIRE -288 256 -288 240

WIRE -144 256 -144 240

WIRE 288 256 288 208

WIRE 432 256 432 -112

WIRE -288 352 -288 336

WIRE -144 352 -144 320

WIRE 16 352 16 288

WIRE 208 352 208 320

WIRE 288 352 288 320

WIRE 432 368 432 336

WIRE 592 384 592 320

WIRE -288 464 -288 432

FLAG 16 352 0

FLAG 208 352 0

FLAG -288 464 0

FLAG 592 384 0

FLAG -80 48 0

FLAG -192 48 0

FLAG 288 352 0

FLAG -144 352 0

FLAG 432 368 0

DATAFLAG 208 208 ""

DATAFLAG 208 80 ""

DATAFLAG 176 -112 ""

DATAFLAG 64 160 ""

DATAFLAG -32 -80 ""

SYMBOL njf 160 96 R0

SYMATTR InstName J1

SYMATTR Value J112

SYMBOL res 192 224 R0

SYMATTR InstName R1

SYMATTR Value 22k

SYMBOL res 0 192 R0

SYMATTR InstName R2

SYMATTR Value 470k

SYMBOL voltage 592 224 R0

WINDOW 123 0 0 Left 0

WINDOW 39 0 0 Left 0

SYMATTR InstName V1

SYMATTR Value 250

SYMBOL res 0 0 R0

SYMATTR InstName R3

SYMATTR Value 470k

SYMBOL voltage -288 336 R0

WINDOW 3 -139 102 Left 2

WINDOW 123 24 124 Left 2

WINDOW 39 0 0 Left 0

SYMATTR InstName V2

SYMATTR Value SINE(0 10mV 1000)

SYMATTR Value2 AC 1

SYMBOL cap -32 112 R90

WINDOW 0 0 32 VBottom 2

WINDOW 3 32 32 VTop 2

SYMATTR InstName C1

SYMATTR Value 10n

SYMBOL res 0 -208 R0

SYMATTR InstName R4

SYMATTR Value 470k

SYMBOL cap -96 -48 R0

SYMATTR InstName C2

SYMATTR Value 100n

SYMBOL res 160 -256 R0

SYMATTR InstName R5

SYMATTR Value 220k

SYMBOL triode 176 -32 R0

SYMATTR InstName U1

SYMATTR Value 12ax7

SYMBOL res -208 -80 R0

SYMATTR InstName R6

SYMATTR Value 33k

SYMBOL cap 272 256 R0

SYMATTR InstName C3

SYMATTR Value 2µ2

SYMBOL res 128 -48 R90

WINDOW 0 0 56 VBottom 2

WINDOW 3 32 56 VTop 2

SYMATTR InstName R7

SYMATTR Value 2k2

SYMBOL cap -160 256 R0

SYMATTR InstName C4

SYMATTR Value 2n2

SYMBOL res -160 144 R0

SYMATTR InstName R8

SYMATTR Value 4k7

SYMBOL res -304 240 R0

SYMATTR InstName R9

SYMATTR Value 200

SYMBOL ind -304 144 R0

SYMATTR InstName L1

SYMATTR Value 270mH

SYMBOL cap 288 -128 R90

WINDOW 0 0 32 VBottom 2

WINDOW 3 32 32 VTop 2

SYMATTR InstName C5

SYMATTR Value 22n

SYMBOL res 416 240 R0

SYMATTR InstName R10

SYMATTR Value 470k

TEXT 400 384 Left 2 !.lib jfet.lib

TEXT 150 416 Left 2 !;tran 10ms

TEXT 400 408 Left 2 !.lib tube.lib

TEXT 448 64 Left 2 !.ac dec 100 1 100000

SHEET 1 880 680

WIRE 176 -272 16 -272

WIRE 592 -272 176 -272

WIRE 176 -240 176 -272

WIRE 16 -192 16 -272

WIRE 176 -112 176 -160

WIRE 224 -112 176 -112

WIRE 432 -112 288 -112

WIRE -80 -80 -192 -80

WIRE 16 -80 16 -112

WIRE 16 -80 -80 -80

WIRE 176 -80 176 -112

WIRE -192 -64 -192 -80

WIRE -80 -48 -80 -80

WIRE 16 -32 16 -80

WIRE 32 -32 16 -32

WIRE 128 -32 112 -32

WIRE 16 16 16 -32

WIRE -192 48 -192 16

WIRE -80 48 -80 16

WIRE 208 96 208 16

WIRE -144 128 -288 128

WIRE -96 128 -144 128

WIRE 16 128 16 96

WIRE 16 128 -32 128

WIRE -288 160 -288 128

WIRE -144 160 -144 128

WIRE 16 160 16 128

WIRE 160 160 16 160

WIRE 16 208 16 160

WIRE 208 208 208 192

WIRE 288 208 208 208

WIRE 208 240 208 208

WIRE 592 240 592 -272

WIRE -288 256 -288 240

WIRE -144 256 -144 240

WIRE 288 256 288 208

WIRE 432 256 432 -112

WIRE -288 352 -288 336

WIRE -144 352 -144 320

WIRE 16 352 16 288

WIRE 208 352 208 320

WIRE 288 352 288 320

WIRE 432 368 432 336

WIRE 592 384 592 320

WIRE -288 464 -288 432

FLAG 16 352 0

FLAG 208 352 0

FLAG -288 464 0

FLAG 592 384 0

FLAG -80 48 0

FLAG -192 48 0

FLAG 288 352 0

FLAG -144 352 0

FLAG 432 368 0

DATAFLAG 208 208 ""

DATAFLAG 208 80 ""

DATAFLAG 176 -112 ""

DATAFLAG 64 160 ""

DATAFLAG -32 -80 ""

SYMBOL njf 160 96 R0

SYMATTR InstName J1

SYMATTR Value J112

SYMBOL res 192 224 R0

SYMATTR InstName R1

SYMATTR Value 22k

SYMBOL res 0 192 R0

SYMATTR InstName R2

SYMATTR Value 470k

SYMBOL voltage 592 224 R0

WINDOW 123 0 0 Left 0

WINDOW 39 0 0 Left 0

SYMATTR InstName V1

SYMATTR Value 250

SYMBOL res 0 0 R0

SYMATTR InstName R3

SYMATTR Value 470k

SYMBOL voltage -288 336 R0

WINDOW 3 -139 102 Left 2

WINDOW 123 24 124 Left 2

WINDOW 39 0 0 Left 0

SYMATTR InstName V2

SYMATTR Value SINE(0 10mV 1000)

SYMATTR Value2 AC 1

SYMBOL cap -32 112 R90

WINDOW 0 0 32 VBottom 2

WINDOW 3 32 32 VTop 2

SYMATTR InstName C1

SYMATTR Value 10n

SYMBOL res 0 -208 R0

SYMATTR InstName R4

SYMATTR Value 470k

SYMBOL cap -96 -48 R0

SYMATTR InstName C2

SYMATTR Value 100n

SYMBOL res 160 -256 R0

SYMATTR InstName R5

SYMATTR Value 220k

SYMBOL triode 176 -32 R0

SYMATTR InstName U1

SYMATTR Value 12ax7

SYMBOL res -208 -80 R0

SYMATTR InstName R6

SYMATTR Value 33k

SYMBOL cap 272 256 R0

SYMATTR InstName C3

SYMATTR Value 2µ2

SYMBOL res 128 -48 R90

WINDOW 0 0 56 VBottom 2

WINDOW 3 32 56 VTop 2

SYMATTR InstName R7

SYMATTR Value 2k2

SYMBOL cap -160 256 R0

SYMATTR InstName C4

SYMATTR Value 2n2

SYMBOL res -160 144 R0

SYMATTR InstName R8

SYMATTR Value 4k7

SYMBOL res -304 240 R0

SYMATTR InstName R9

SYMATTR Value 200

SYMBOL ind -304 144 R0

SYMATTR InstName L1

SYMATTR Value 270mH

SYMBOL cap 288 -128 R90

WINDOW 0 0 32 VBottom 2

WINDOW 3 32 32 VTop 2

SYMATTR InstName C5

SYMATTR Value 22n

SYMBOL res 416 240 R0

SYMATTR InstName R10

SYMATTR Value 470k

TEXT 400 384 Left 2 !.lib jfet.lib

TEXT 150 416 Left 2 !;tran 10ms

TEXT 400 408 Left 2 !.lib tube.lib

TEXT 448 64 Left 2 !.ac dec 100 1 100000

I just used a J112 there are much better JFETS. Very noise free when testing. The input circuit is just a model of the reverb pickup coil.

1kHz THD in LTSpice is 0.47% at 2VRMS output.

All 2C51 modell that I have is cr.p, so this THD is inaccurate.

If you use correct models -for example trioded D3a, C3g, E55L, E810F, 6AK5, or 12AX7, E88CC, EC8010- the simmed THD is usually below 0.1% even at large input voltage.

.asc file is attached, models inserted as comments. I have been unable to find equivalent models for the TSML1000 and HLMP6000 LEDs, so cathode resistor with bypass capacitors have been substituted with appropriate bias points.

Agreed, the distortion figures cannot be accurate, should not be so high given the low voltage swing and linearity. It is present after the first gain stage, no change when using two separate triode-strapped D3a models. Substituting ECC88 for the 5670 model still results in 0.47% THD on the output.

I have considered using two triode-strapped EF86 in place of the 5670 in the second gain position. Similar mu, low noise, excellent linearity.

Assuming the high distortion is inaccurate, my two outstanding concerns are input capacitance and noise, although the noise was not an issue in SY's similar MC implementation.

Agreed, the distortion figures cannot be accurate, should not be so high given the low voltage swing and linearity. It is present after the first gain stage, no change when using two separate triode-strapped D3a models. Substituting ECC88 for the 5670 model still results in 0.47% THD on the output.

I have considered using two triode-strapped EF86 in place of the 5670 in the second gain position. Similar mu, low noise, excellent linearity.

Assuming the high distortion is inaccurate, my two outstanding concerns are input capacitance and noise, although the noise was not an issue in SY's similar MC implementation.

Attachments

Thanks L0rdGwyn for the file!

After trying to run it this error popped up"

"could not open include file IXCP10M455.txt"

So.......

I can see the .sbckt of that model. Can I remove that .txt file line?

After trying to run it this error popped up"

"could not open include file IXCP10M455.txt"

So.......

I can see the .sbckt of that model. Can I remove that .txt file line?

Last edited:

Simulation is just an educated guess, i would like to see real measurments of the completed

riaa stage.

riaa stage.

Yes, of course it is. If this stage comes to fruition, I will be happy to provide real world measurements. I have many of the parts on hand already, so it should come together relatively quickly.

Just finished the PCB for the SF output buffer.

Includes TO-220 pads for the AOT1N60 source follower, IXCP10M45S current sink on the source, trimmer / jumper / resistor to set the source follower idle current via the current sink, protection zeners, 100nF PS decoupling cap, gate stoppers...

Includes TO-220 pads for the AOT1N60 source follower, IXCP10M45S current sink on the source, trimmer / jumper / resistor to set the source follower idle current via the current sink, protection zeners, 100nF PS decoupling cap, gate stoppers...

- Home

- Amplifiers

- Tubes / Valves

- First Phono Stage Design: MM D3a > 2C51 Hybrid