Hi

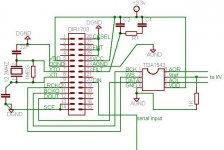

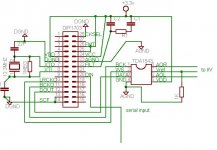

I have a question about a spdif DAC design using dir1703 and tda1543.

Can I build it like this🙁attached)

Is it right to select "16bit msb first right justified" and 128fs?

If it is not, then is it possible to build a dac from these chips only?

kind regards

Adam

I have a question about a spdif DAC design using dir1703 and tda1543.

Can I build it like this🙁attached)

Is it right to select "16bit msb first right justified" and 128fs?

If it is not, then is it possible to build a dac from these chips only?

kind regards

Adam

Attachments

darkfenriz said:Hi

I have a question about a spdif DAC design using dir1703 and tda1543.

Can I build it like this🙁attached)

Is it right to select "16bit msb first right justified" and 128fs?

If it is not, then is it possible to build a dac from these chips only?

kind regards

Adam

This dir1703 chip has a 24bit I2S output mode.

Well I assume it's I2S but it's listed as IIS! (I haven't looked at the timing diagram though)

Not sure about 128fs....

Why should I use 24 bit output mode from spdif receiver if tda1543 is 16 bit DAC?

I think I should choose 128fs, because maximum frequency at clock input of tda1543 is only 9.2MHz, is that right?

I think I should choose 128fs, because maximum frequency at clock input of tda1543 is only 9.2MHz, is that right?

darkfenriz said:Why should I use 24 bit output mode from spdif receiver if tda1543 is 16 bit DAC?

Because you have no choice as far as the '1703 is concerned. In I2S mode it always assumes 24bit data. The TDA1543 will ignore the excess bits.

I understand, yes, that's the only i2s mode and is marked IIS. Thanks to both of you.

Another question: what crystal should I use? can it be 12.3Mhz?

Another question: what crystal should I use? can it be 12.3Mhz?

Why are you using TDA1543? It's not a NOS design, since you have the DF. I just don't get it. AFAIK, the only reason to use TDA1543 is for NOS designs. It's not as if the specs of TDA1543 by themselves are so great.

Whoops, my bad. I thought DIR1703 was a filter. Sorry about that. Didn't mean to scare you. Please, carry on! 😀

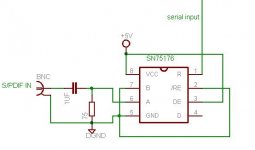

SN75176 will be supplied from +5V, so overdriving DIR1703's input, bacause DIR is supplied from 3.3V.

This is probably not going to fry anything as they state maximum DIR input of 5.5V (LOW: 0 to 30%Vcc ; HIGH : 70%Vcc to 5.5V), but I wonder wheather this is going to increase jitter much.

What do you think?

regards

Adam

This is probably not going to fry anything as they state maximum DIR input of 5.5V (LOW: 0 to 30%Vcc ; HIGH : 70%Vcc to 5.5V), but I wonder wheather this is going to increase jitter much.

What do you think?

regards

Adam

darkfenriz said:SN75176 will be supplied from +5V, so overdriving DIR1703's input, bacause DIR is supplied from 3.3V.

This is probably not going to fry anything as they state maximum DIR input of 5.5V (LOW: 0 to 30%Vcc ; HIGH : 70%Vcc to 5.5V), but I wonder wheather this is going to increase jitter much.

What do you think?

regards

Adam

http://focus.ti.com/lit/ug/sleu008a/sleu008a.pdf

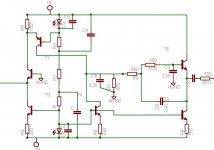

As you are using the tda1543 I'd be tempted to go with the evaluation board setup.

- Status

- Not open for further replies.

- Home

- Source & Line

- Digital Source

- DAC-will this work?