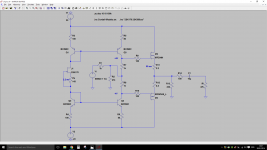

Here is an slightly different buffer. I will be building this on a prototype board shortly just to try it.

Jfet and its Pd pot is used as the biasing device. Nothing requires matching here.

Some of you will recognize elements from existing designs of course, e.g. the improved wilson current mirror, and BA3 style degeneration.

Pd is a 220R pot. Reduce Pd gradually from 220R to approx half way through until you get approx 60ma thru the devices. The values of course will be different depending upon the Jfet Idss, as long as you start from high to lower resistances you are safe. Use BL grade for the 2SK170.

The devices of choice are FQP3N30 & FQP3P20.

The devices will need some heatsinking, attach them to the bottom of the case or something.

Jfet and its Pd pot is used as the biasing device. Nothing requires matching here.

Some of you will recognize elements from existing designs of course, e.g. the improved wilson current mirror, and BA3 style degeneration.

Pd is a 220R pot. Reduce Pd gradually from 220R to approx half way through until you get approx 60ma thru the devices. The values of course will be different depending upon the Jfet Idss, as long as you start from high to lower resistances you are safe. Use BL grade for the 2SK170.

The devices of choice are FQP3N30 & FQP3P20.

The devices will need some heatsinking, attach them to the bottom of the case or something.

Last edited:

- Status

- Not open for further replies.