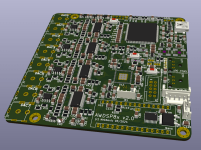

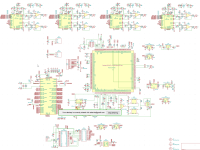

I am revisiting my old project - 4way DSP2DAC crossover with ADAU1452. For the moment I am having trouble starting up ADAU1452 core with MCLK. While working with analog devices engineers to figure out what I messed up, I thought I'd post it here.

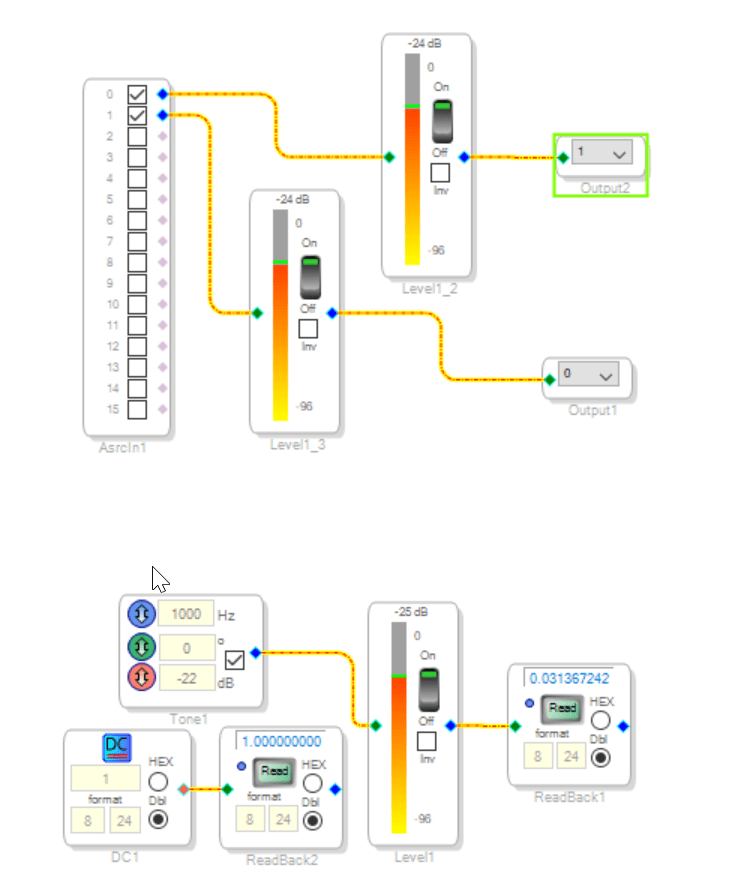

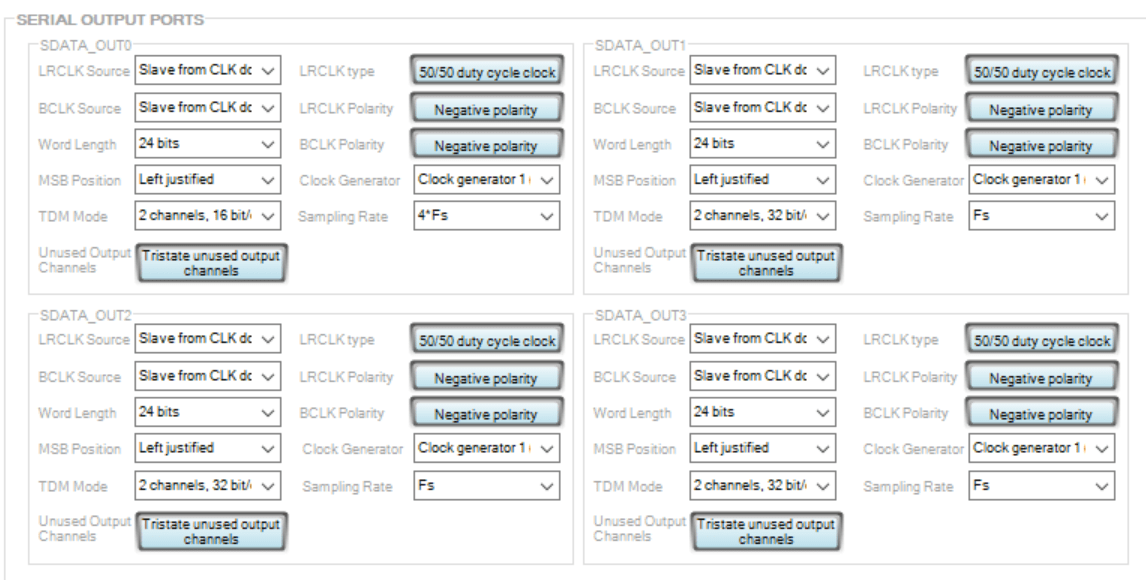

My core is up and running after a struggle with register setup. I just need to figure out a way to send I2S signals from SPDIF to serial outputs over to 4 DACs. SPDIF receiver works correctly and I can see the signal being detected in DSP, but there is nothing on the serial outputs. MCLK is fed to DACs from CLKOUT and that part works fine.

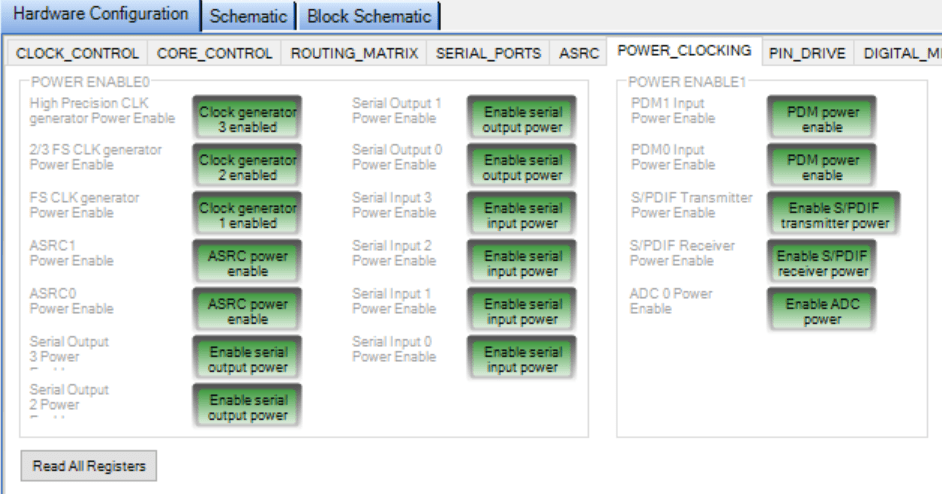

Yes, all the power clocking is on:

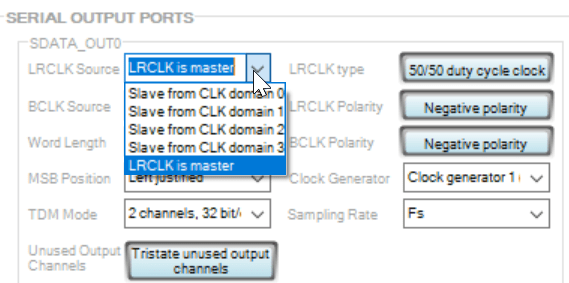

When I put LRCLK and BCLK in master mode, there is an output signal, but sampling frequency does not match the input sampling frequency from SPDIF, and there is nothing on SDATA line (verified with scope). I guess then some processing needs to be done, cannot just pass it through DSP with original sampling rate? I was under impression that slave mode is to DSP internal clock, and not to an external DAC.

I am simply trying to pass SPDIF input signal to SDATAOUT(0-4) pins.

When I put LRCLK and BCLK in master mode, there is an output signal, but sampling frequency does not match the input sampling frequency from SPDIF, and there is nothing on SDATA line (verified with scope). I guess then some processing needs to be done, cannot just pass it through DSP with original sampling rate? I was under impression that slave mode is to DSP internal clock, and not to an external DAC.

I am simply trying to pass SPDIF input signal to SDATAOUT(0-4) pins.

Last edited:

This is how it should be, your DSP operates at its internal frequency, which is why you use ASRC to receive an SPDIF signal. If you receive spdif directly without ASRC, then you will have frequency desynchronization between the chipboard and the spdif source.When I put LRCLK and BCLK in master mode, there is an output signal, but sampling frequency does not match the input sampling frequency from SPDIF, and there is nothing on SDATA line (verified with scope).

When the SPDIF is decoded by the DSP and passed through ASRC, the sampling frequency of the signal in the DSP will be the one that you set in the Sigma Studio project, this is very convenient when you need to receive a signal with different sampling rates, ASRC will make sure that the frequency of the signal inside the DSP is the one that needed. As a result, when you output a signal to the I2S port you need to take this fact into account. The frequency of the project is decisive and you need to start from it when you output sound to the I2S port.I guess then some processing needs to be done, cannot just pass it through DSP with original sampling rate?

Later I will run I2S on my board in master mode and tell you about the result.

I checked the i2S output on my board as a master, everything works according to logic. The frequency on all I2S pins is present according to the settings in Sigma Studio, and there is also a data stream on the SDATA pin. I have attached the project file, but look carefully, the PLL settings in the file are for my board, not yours.

Attachments

It was a bad solder joint. I guess the question remains - how to preserve the original sample rate through DSP to outputs?

Are you interested in one specific frequency, or do you want to be able to change the sample rate of the I2S output in sync with the change in the sample rate of the spdif input?It was a bad solder joint. I guess the question remains - how to preserve the original sample rate through DSP to outputs?

Dont think you can do that easily. Internal sample rate is set in firmware, cant change it on the fly. So in theory you could have external mcu load appropriate firmware (with filter coefficients for this sample rate) to DSP when spdif sample rate change is detected. Not sure if there is other way

Ok, thanks, not a big deal. I am not a believer in high-res formats anyway, so resampling will do just fine. Board is full up and running with 4-way crossover, now I just need more amps.

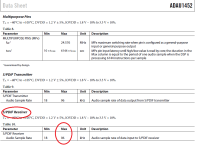

According to the datasheet, SPDIF receiver can receive signals up to 192kHz, but I see that SPDIF locks only up to 96kHz. My core is running at 48kHz, but setting it up to 4*Fs didn't help either. If it's supported at all, I will keep digging.

Analog replied that they messed up clocking in ADAU1452, so it will not work with rates above 96kHz.

I am not a believer in high res audio, so you are probably right. If I could order ADAU1467 as a sample I would simply drop it in, but they seem to have tightened the samples policy.

- Home

- Source & Line

- Digital Line Level

- AWDSP8X - 4way stereo DSP2DAC board with ADAU1452