Hi Everyone,

Any ideas about how to convert optical SPDIF to the AD1866 interface format?

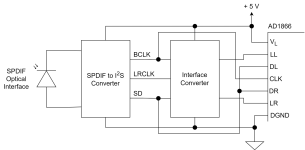

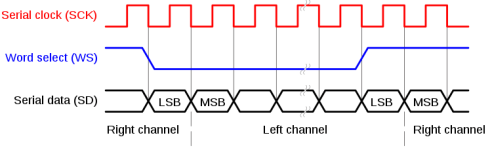

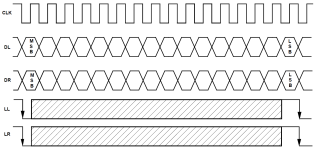

I was thinking about using a SPDIF to I2S converter, similar to this and then converting the signal to the AD1866 format, in this case only the latch signals need to be modified (LL and LR). Do you know if any board with this functionality is currently available for purchase in europe?

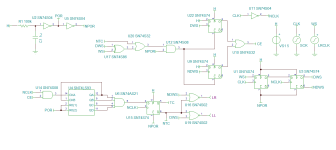

To produce the LL and LR signals I have designed a circuit using the 74 series logic family, it seems to work on simulation, but I don't have a clue if it actually works in practice, also, this circuit is a bit complex and requires a lot of ICs. Only faster digital devices 74FXX or 74SXX seem to be quick enough for sample rates of 88.2 kHz and over, 74HCXX and 74LSXX, only work for 48 kHz or less. I also have an Arduino Due board, do you know if it can be used for the format conversion? Is there any simple way to convert optical SPDIF or I2S to the AD1866 format, using only one or two ICs?

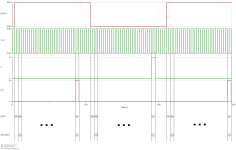

I have attached a few pictures of the block diagram, interface conversion logic circuit, timing diagrams and a TINA SPICE simulation file.

Any ideas about how to convert optical SPDIF to the AD1866 interface format?

I was thinking about using a SPDIF to I2S converter, similar to this and then converting the signal to the AD1866 format, in this case only the latch signals need to be modified (LL and LR). Do you know if any board with this functionality is currently available for purchase in europe?

To produce the LL and LR signals I have designed a circuit using the 74 series logic family, it seems to work on simulation, but I don't have a clue if it actually works in practice, also, this circuit is a bit complex and requires a lot of ICs. Only faster digital devices 74FXX or 74SXX seem to be quick enough for sample rates of 88.2 kHz and over, 74HCXX and 74LSXX, only work for 48 kHz or less. I also have an Arduino Due board, do you know if it can be used for the format conversion? Is there any simple way to convert optical SPDIF or I2S to the AD1866 format, using only one or two ICs?

I have attached a few pictures of the block diagram, interface conversion logic circuit, timing diagrams and a TINA SPICE simulation file.

Attachments

-

Block Diagram.png45.9 KB · Views: 130

Block Diagram.png45.9 KB · Views: 130 -

I2S_Timing.png8.7 KB · Views: 118

I2S_Timing.png8.7 KB · Views: 118 -

AD1866_Timing.png29.2 KB · Views: 131

AD1866_Timing.png29.2 KB · Views: 131 -

I2S CONVERTER (V3 - HIGH SPEED).png20.3 KB · Views: 145

I2S CONVERTER (V3 - HIGH SPEED).png20.3 KB · Views: 145 -

Timing Diagram - I2S to AD1866 Interface (v3 - High Speed).png11.8 KB · Views: 145

Timing Diagram - I2S to AD1866 Interface (v3 - High Speed).png11.8 KB · Views: 145 -

I2S Converter (v3 - High Speed).zip3.8 KB · Views: 106

Given that AD1866, like most R2R style DACs uses a right-justified data format it would probably be a simpler solution not to go via I2S. All modern S/PDIF decoder chips that I've met have the capability to output various formats besides I2S, I would choose an output format closer to what the DAC's expecting. That'd normally be some kind of right-justified format - at least then the WS/LRCK signal would start out in the right place relative to the data, unlike with I2S.

Thank you very much for your reply abraxalito.

Maybe I can use a S/PDIF converter board, based on the DIR9001, for example, and then I can set the format to 16 bit MSB first right-justified. LR can be directly connected to LRCLK, LL requires an inverter gate.

Do you know where I can get a clone of the eval board of the DIR9001 or a chip with similar funcionalities for a lower price, do you know any supplier that delivers such boards in europe?

Maybe I can use a S/PDIF converter board, based on the DIR9001, for example, and then I can set the format to 16 bit MSB first right-justified. LR can be directly connected to LRCLK, LL requires an inverter gate.

Do you know where I can get a clone of the eval board of the DIR9001 or a chip with similar funcionalities for a lower price, do you know any supplier that delivers such boards in europe?

I would hope Aliexpress sellers would send to Europe - here is the kind of board you'll need : https://www.aliexpress.com/item/100...!sea!HK!2609685283&curPageLogUid=skTk7RwwedLC

Thank you very much abraxalito,

I will try to order this board or a similar one.

For the latch signals I still need an inverter gate, for the left channel. Do you think a 74HC04 is quick enough, or I need a 74F04 or something even faster?

I will try to order this board or a similar one.

For the latch signals I still need an inverter gate, for the left channel. Do you think a 74HC04 is quick enough, or I need a 74F04 or something even faster?

I think HC04 (or a single gate version) is going to be plenty fast enough when run on 5V. The quickest inverters are the unbuffered ones so if you worry about speed, go for 74HCU04 but I think the plain one will work fine.

AD1866 is not very good sounding, there are better options like AD1865 configured as current output.

Anyway jlsounds i2soverusb can be configured for direct driving the AD1866 (mode like PCM58, AD1851).

Or alternatively you can use the I2S input logic from my post (16-bit configuration) https://www.diyaudio.com/community/...2s-input-nos-r-2r.354078/page-74#post-6533922

Or if you want skip the I2S logic, you can use my CPLD solution (use the 16-bit configuration) : https://electrodac.blogspot.com/p/i2s-to-pcm-dac-converter-tutorial-cpld.html

Anyway jlsounds i2soverusb can be configured for direct driving the AD1866 (mode like PCM58, AD1851).

Or alternatively you can use the I2S input logic from my post (16-bit configuration) https://www.diyaudio.com/community/...2s-input-nos-r-2r.354078/page-74#post-6533922

Or if you want skip the I2S logic, you can use my CPLD solution (use the 16-bit configuration) : https://electrodac.blogspot.com/p/i2s-to-pcm-dac-converter-tutorial-cpld.html

Hi miro1360, thank you very much for your reply.

I have some AD1866 chips that I want to use, most of the R2R DAC ICs are now out of production. Analog Devices still makes the AD1866 and the AD1851. I know that there are better sounding chips like the AD1862, AD1865, TDA154x, PCM1704K, PCM58 among others. The main reasons I use the AD1866 are:

Maybe in a future project I will try the 1851 in the J version, if I can find one.

Regarding the solutions you have presented, I have already ordered a board similar to the one suggested by abraxalito, so I will stick with this solution.

The solution with the CPLD seems interesting but I don't have any experience with CPLDs I need to learn how to use them.

I have some AD1866 chips that I want to use, most of the R2R DAC ICs are now out of production. Analog Devices still makes the AD1866 and the AD1851. I know that there are better sounding chips like the AD1862, AD1865, TDA154x, PCM1704K, PCM58 among others. The main reasons I use the AD1866 are:

- Circuit simplicity (since it features 2 DACs and requires few external components)

- It's still in production (most of the better sounding DAC ICs are currently clones that might not have the same performance as the original ones, also if I buy them 2nd hand I might end up wasting a lot of money on a chip that is no longer working or which was exposed to conditions above the absolute maximum ratings and no longer has the same performance)

- For me sounds much better than most audio CODECs (like ALC1200 and the like), IMO it also outperforms some advanced segment DACs (multibit DS architectures), like the PCM510x.

Maybe in a future project I will try the 1851 in the J version, if I can find one.

Regarding the solutions you have presented, I have already ordered a board similar to the one suggested by abraxalito, so I will stick with this solution.

The solution with the CPLD seems interesting but I don't have any experience with CPLDs I need to learn how to use them.

LR can be directly connected to LRCLK, LL requires an inverter gate.

Actually it's the opposite, sorry. With DIR9001, LR requires an inverter and LL doesn't. 😛

The DIR9001 board has arrived!

Everything is working as expected, thank you very much abraxalito.

Everything is working as expected, thank you very much abraxalito.

Or if you want skip the I2S logic, you can use my CPLD solution (use the 16-bit configuration) : https://electrodac.blogspot.com/p/i2s-to-pcm-dac-converter-tutorial-cpld.html

How much is the time delay introduced by your solution, Miro, is it enough to cause A/V sync issues? I'm interested in this solution for my project with the AD1862.

- Home

- Source & Line

- Digital Line Level

- AD1866 NOS DAC - Optical SPDIF Interface