to save you from ghost chasing and give you some more time for quality staring at goats, which is much more beneficial for state of mind

at least I'm finding it that way

disclaimer - both DC offset and Iq stability are depending of hefty heatsinking, rail variance ( mains fluctuation) and hope that SIT in case is not having hungry gate

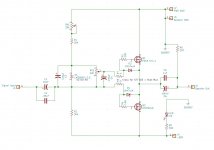

here is case one - SIT Ugs lower in number than P channel Mosfet Ugs, so SIT gate is higher than Mos gate, voltage vise

reckon that 2V5 voltage reference is covering most possible cases; if more is needed, there are ways for that too, easy to increase

it is important to use voltage reference being stable from low Iq; from memory shown one is stable from 10uA upwards

circuit is tested and proven

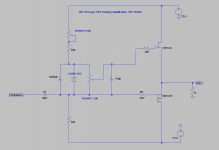

picture self explanatory; THF51 as example, applicable for pretty much any depletion device up, being similar in behavior

at least I'm finding it that way

disclaimer - both DC offset and Iq stability are depending of hefty heatsinking, rail variance ( mains fluctuation) and hope that SIT in case is not having hungry gate

here is case one - SIT Ugs lower in number than P channel Mosfet Ugs, so SIT gate is higher than Mos gate, voltage vise

reckon that 2V5 voltage reference is covering most possible cases; if more is needed, there are ways for that too, easy to increase

it is important to use voltage reference being stable from low Iq; from memory shown one is stable from 10uA upwards

circuit is tested and proven

picture self explanatory; THF51 as example, applicable for pretty much any depletion device up, being similar in behavior

Attachments

Last edited:

case 2 ( even if rare) -

SIT Ugs being greater in number than Mosfet Ugs, so SIT gate sitting bellow Mos gate

everything written up, applicable here

note 470uF cap polarity

SIT Ugs being greater in number than Mosfet Ugs, so SIT gate sitting bellow Mos gate

everything written up, applicable here

note 470uF cap polarity

Attachments

Last edited:

late, so forgot to write - case 2 also tested, but I had on hand SIT-Mos combo with minimal difference in Ugs, thus powering - up current behavior was nice and gentle

what could happen with 1V of Ugs difference, dunno - possible current peak, demands testing

what could happen with 1V of Ugs difference, dunno - possible current peak, demands testing

Thank you MZM!

Thank you MZM!I'll come back to these after I get my desk cleaned up and after I finish

with the UJ3N/FQA combo.

with the UJ3N/FQA combo.Cheers!

Stephen

maybe it could help with that too

start with Case 2, as I'm understanding your UJ3N adventures

though, how current behavior during startup is going to be, - test with fuses in rail

start with Case 2, as I'm understanding your UJ3N adventures

though, how current behavior during startup is going to be, - test with fuses in rail

Last edited:

ZM abides 🙂

case 2 - 3m3 can be decreased to 470uF, for faster biasing, without loss of stability

btw. I made a typo - LM385-2V5 is stable from 20uA up (not 10uA as I wrote in post #1)

case 2 - 3m3 can be decreased to 470uF, for faster biasing, without loss of stability

btw. I made a typo - LM385-2V5 is stable from 20uA up (not 10uA as I wrote in post #1)

ya can call me ZM - Wannabee Conceptualist Wanabee Papa

sometimes I divine my self, how nice I did something ........ just to find it later already done, in most cases better

taking yourself too serious most often simply backfires

sometimes I divine my self, how nice I did something ........ just to find it later already done, in most cases better

taking yourself too serious most often simply backfires

Last edited:

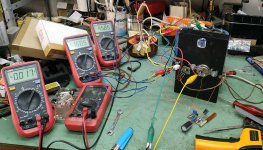

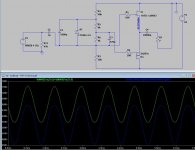

forgot to post Pudding

found notes too

everything about Case 1 testing; didn't made notes and pics when I tested Case 2

Note:

/////////////////////////////////////////////////////////////////////////////////////

Smallish heatsink , so heat up and cool off cycle is shorter

Mos and SIT at same height, close one to another

Mos mica and goop , SIT silicone sheet

Temperature controlled with laser thingie, measured between parts

everything set at 55C, measured both Ugs and DC offset,measured DC bump at output during Power Off

Cooled to 25C , powered on and measured power on DC bump , initial (steady) Iq and DC Offset

Then again heated to 55C to confirm starting values

Starting/wanted/ref. values are :

Rails +/-22V5dc

Iq 1A7

output DC Offset sorta 0-ish mV

output loaded with 8R dummy

Test 1 :

MOSfet IR IRFP9140

SIT THF51S Ser. No 1Z0115

Mos Ugs -4V637

SIT Ugs -2V716

Ugs difference 1V925

55C - 1A7 , Offset +27mV , Turn Off bump: +860mV

cooled to 25C, powered ON, Turn ON bump: -440mV, steady Iq 1A56, DC Offset +40mV

Test 2 :

MOSfet IR IRFP9140

SIT THF51S Ser. No 1X0177

Mos Ugs -4V637

SIT Ugs -3V677

Ugs difference 0V97

55C - 1A7 , Offset +15mV , Turn Off bump: +480mV

cooled to 25C, powered ON, Turn ON bump: +740mV, steady Iq 1A59, DC Offset +40mV

schematic of test setup attached; LM385-2V5 chosen as best solution , being effective from 20uA ; in this case current through 10K trimpot is 250uA , around 250uA through LM385-2V5

//////////////////////////////////////////////////////////////////////////////////

found notes too

everything about Case 1 testing; didn't made notes and pics when I tested Case 2

Note:

/////////////////////////////////////////////////////////////////////////////////////

Smallish heatsink , so heat up and cool off cycle is shorter

Mos and SIT at same height, close one to another

Mos mica and goop , SIT silicone sheet

Temperature controlled with laser thingie, measured between parts

everything set at 55C, measured both Ugs and DC offset,measured DC bump at output during Power Off

Cooled to 25C , powered on and measured power on DC bump , initial (steady) Iq and DC Offset

Then again heated to 55C to confirm starting values

Starting/wanted/ref. values are :

Rails +/-22V5dc

Iq 1A7

output DC Offset sorta 0-ish mV

output loaded with 8R dummy

Test 1 :

MOSfet IR IRFP9140

SIT THF51S Ser. No 1Z0115

Mos Ugs -4V637

SIT Ugs -2V716

Ugs difference 1V925

55C - 1A7 , Offset +27mV , Turn Off bump: +860mV

cooled to 25C, powered ON, Turn ON bump: -440mV, steady Iq 1A56, DC Offset +40mV

Test 2 :

MOSfet IR IRFP9140

SIT THF51S Ser. No 1X0177

Mos Ugs -4V637

SIT Ugs -3V677

Ugs difference 0V97

55C - 1A7 , Offset +15mV , Turn Off bump: +480mV

cooled to 25C, powered ON, Turn ON bump: +740mV, steady Iq 1A59, DC Offset +40mV

schematic of test setup attached; LM385-2V5 chosen as best solution , being effective from 20uA ; in this case current through 10K trimpot is 250uA , around 250uA through LM385-2V5

//////////////////////////////////////////////////////////////////////////////////

Attachments

Once again, thank you MZM for this.

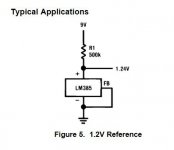

If I understand correctly, the 36K/39K/20K trimpot is setting the (approximate) bias voltage seen by the gates and the LM385 is setting a 2.4V envelope within that. The 10K trimmer is acting as voltage divider to trim the difference in Ugs (ZMengrish for Vgs) between the 2 devices. I don't have 2.4V but I do have 1.2V ones so I can try this.

Questions

- would LED work here or is the problem with low current capability?

- tie 3rd leg to negative side is that correct?

What I like about this:

- no degeneration, get to visit square law happyland ("minimize degeneration where you can" - smart guy who is celebrating birthday today)

- simple

I went back and looked at SissySIT R.3 again and understand a bit more. Is this baby SissySIT junior version for dummies? I understand the implementation in SR3 is much more sophisticated and well behaved but maybe this is enough for those who enjoy their food raw.

If I understand correctly, the 36K/39K/20K trimpot is setting the (approximate) bias voltage seen by the gates and the LM385 is setting a 2.4V envelope within that. The 10K trimmer is acting as voltage divider to trim the difference in Ugs (ZMengrish for Vgs) between the 2 devices. I don't have 2.4V but I do have 1.2V ones so I can try this.

Questions

- would LED work here or is the problem with low current capability?

- tie 3rd leg to negative side is that correct?

What I like about this:

- no degeneration, get to visit square law happyland ("minimize degeneration where you can" - smart guy who is celebrating birthday today)

- simple

I went back and looked at SissySIT R.3 again and understand a bit more. Is this baby SissySIT junior version for dummies? I understand the implementation in SR3 is much more sophisticated and well behaved but maybe this is enough for those who enjoy their food raw.

Attachments

well, it seems that you already replied on all your questions

if you didn't ( reference question) , re-read few times more what I wrote ..... and you'll get it - exactly what I wrote as important characteristic of LM385-2V5

last line of text in my previous post - #9- is telling ya all

- it isn't stable as none of SissySIT iterations, but it will work ..... and it will especially work flawlessly if you make it with one rail and caps in/out - as Pa made DEFiSIT

-if you have hungry SIT gate, only SissySIT R.3 can cope with that

conclusion - you got last trick to make XeroX copy of Pa's DEFiSIT, with Tokin SIT

last thing - LM 385-2V5 is 2pin device, even if in TO92 case with all 3pins

see here

what you show is from datasheet of LMx85 adj.

if you didn't ( reference question) , re-read few times more what I wrote ..... and you'll get it - exactly what I wrote as important characteristic of LM385-2V5

last line of text in my previous post - #9- is telling ya all

- it isn't stable as none of SissySIT iterations, but it will work ..... and it will especially work flawlessly if you make it with one rail and caps in/out - as Pa made DEFiSIT

-if you have hungry SIT gate, only SissySIT R.3 can cope with that

conclusion - you got last trick to make XeroX copy of Pa's DEFiSIT, with Tokin SIT

last thing - LM 385-2V5 is 2pin device, even if in TO92 case with all 3pins

see here

what you show is from datasheet of LMx85 adj.

Yes, I will do it soon 🙂)

I have a little worried about this circuit that not opto bias as SissySIT. maybe I will make something damage?

I have a little worried about this circuit that not opto bias as SissySIT. maybe I will make something damage?

it is tried and proven

as I already said - not stable as optobiasing, but with some luck (with SITs on disposal) it can be decent simple amp

edit:

it can be awesome simple amp

as I already said - not stable as optobiasing, but with some luck (with SITs on disposal) it can be decent simple amp

edit:

it can be awesome simple amp

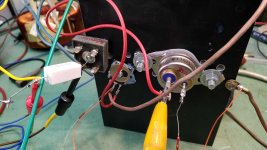

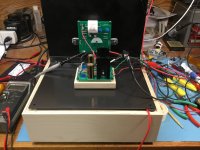

I built this with a Pass-SIT 1 from Papa and it sounds Great! I did use a coupling cap and take the SIT drain to ground.

Picture for ZM

Attachments

-

A1D7D4CA-8F9D-468F-83D9-C236861F470C.jpeg594.7 KB · Views: 290

A1D7D4CA-8F9D-468F-83D9-C236861F470C.jpeg594.7 KB · Views: 290 -

3CB523ED-2DB5-413E-9FB0-6BF6F820B330.jpeg477.1 KB · Views: 254

3CB523ED-2DB5-413E-9FB0-6BF6F820B330.jpeg477.1 KB · Views: 254 -

EE7AE240-40F6-4125-97D5-E57E867009FD.jpeg447.4 KB · Views: 230

EE7AE240-40F6-4125-97D5-E57E867009FD.jpeg447.4 KB · Views: 230 -

53AA8130-06C2-4029-9C2B-8A79F5C518F8.jpeg687.4 KB · Views: 239

53AA8130-06C2-4029-9C2B-8A79F5C518F8.jpeg687.4 KB · Views: 239 -

4BDAA5FB-B572-4F56-B281-D2D8FA36C3DE.jpeg687.3 KB · Views: 253

4BDAA5FB-B572-4F56-B281-D2D8FA36C3DE.jpeg687.3 KB · Views: 253

- Home

- Amplifiers

- Pass Labs

- Redneck ZM DEFiSIT/DEF biasing