Dear all,

I implemented a new Class-D amp which is modulating the PWM signal fully digital with the help of a 4th order noise-shaper.

So actually a similar concept like a lot of silicon vendors out there are using for their digital I2S input Class-D amps.

The full source code is available on my GitHub:

GitHub - YetAnotherElectronicsChannel/FPGA-Class-D-Amplifier

And I also explained everything once again in a YouTube video (including listening tests)

YouTube

Have fun by checking out,

Markus

I implemented a new Class-D amp which is modulating the PWM signal fully digital with the help of a 4th order noise-shaper.

So actually a similar concept like a lot of silicon vendors out there are using for their digital I2S input Class-D amps.

The full source code is available on my GitHub:

GitHub - YetAnotherElectronicsChannel/FPGA-Class-D-Amplifier

And I also explained everything once again in a YouTube video (including listening tests)

YouTube

Have fun by checking out,

Markus

Well above my head.

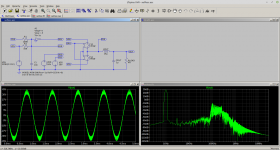

At the risk of using the wrong words the attached is a model of a first order self oscillating Class D with pre-filter feedback.

The zero output switching frequency is set by the time delay in the gate. In simple terms it notices an error then takes Td to respond accumulating the opposite error then flips back recovers the error then takes another Td to respond.

That works out to be 4 x Td. In this case 250KHz. When driven with a signal the self oscillating frequency varies according to the output level.

Picture plus LTspice asc.

What happens if you replace A1 with your FPGA and program the delay to adapt it in order to maintain a fixed switching frequency?

...

At the risk of using the wrong words the attached is a model of a first order self oscillating Class D with pre-filter feedback.

The zero output switching frequency is set by the time delay in the gate. In simple terms it notices an error then takes Td to respond accumulating the opposite error then flips back recovers the error then takes another Td to respond.

That works out to be 4 x Td. In this case 250KHz. When driven with a signal the self oscillating frequency varies according to the output level.

Picture plus LTspice asc.

What happens if you replace A1 with your FPGA and program the delay to adapt it in order to maintain a fixed switching frequency?

...

Attachments

@MorbidFractal:

Well I know what you mean, I know the self-resonating concept. But I have never seen it somewhere implemented in some pure digital logic. I know it only mainly from the IRF designs.

Actually the self-resonating concept is also only some kind of a 1-Bit sigma-delta converter, but without any external clocking.

But interesting hint, would be definitely worth it trying out what happens actually.

Well I know what you mean, I know the self-resonating concept. But I have never seen it somewhere implemented in some pure digital logic. I know it only mainly from the IRF designs.

Actually the self-resonating concept is also only some kind of a 1-Bit sigma-delta converter, but without any external clocking.

But interesting hint, would be definitely worth it trying out what happens actually.

Cool. How do you implement feed back?

The feedback is implemented behind the 5 bit quantizer of the noise-shaper.

The power-stage actually is open-loop then (see in the block-diagram in my slides I provided in my GitHub)

I got into FPGA's in the 1990's.

We got a project in a for Ford ECU interface to modify the engine fuel and ignition maps.

In those days before VHDL we had to use schematic entry to define the functions of the FPGA.

I really should have kept going with FPGA's and moved onto VHDL but never had the time which is shame.

I do work with USB scopes which would benefit from a fast FPGA interface.

We got a project in a for Ford ECU interface to modify the engine fuel and ignition maps.

In those days before VHDL we had to use schematic entry to define the functions of the FPGA.

I really should have kept going with FPGA's and moved onto VHDL but never had the time which is shame.

I do work with USB scopes which would benefit from a fast FPGA interface.

cool project. I have made low fidelity delta sigma ADCs from discrete components before with good results. I see the immediate low hanging fruit would be switch to a different FPGA as you should be able to achieve significantly higher clocks. As an example using something like a Xilinx 7 series Zynq in the lowest speed grade (not that expensive) I have implemented 200 MHz + logic of hard to optimize things like increment by 5 counters, nicer things could go 300 MHz+.

- Home

- Amplifiers

- Class D

- Full digital Class-D amplifier on FPGA (with a multibit sigma-delta noiseshaper)