Their ESR tends to be too low for adequate bypass damping so they tend to ring on transients. If you really want to use them I guess you could put a small resistor in series to control damping. You will have more series inductance that way though....should i use C0G preferably for bypassing?

@Markw4 Not true, not for this regulator. Eval board parallels 5 pieces x5r, to further reduce esr. At input too low esr MAY introduce oscillations, but with tant and 0.1uf cog it shpuldn't be an issue. And as i mentioned, it's always smart for a first design to leave aditional pads, in this case not for resistor at input, but for another tantalum cap with few hundred mohm esr.

This one is quite hard to push to maximum load for extended periods of time by itself (package is the limit), with a pass transistor yeah. And yes, i borrow from time to time programable dc load, but most of the time i use dummy resistive load for testing. Fortunately, as mentioned before, people have tested this regulator far more than i have. Low output esr is mandatory, too low input esr piezo cap can be problematic, hence aditional pad to dampen with ~300-400mohm cap if required. Usually not a problem, depending on the layout, cap distance etc.

Ah, well i went with X7R for the input, since im not sure when i come around to test/measure things

im not as concerned about the tant output caps, they have together only 30mohms ESR + the 100nF C0G

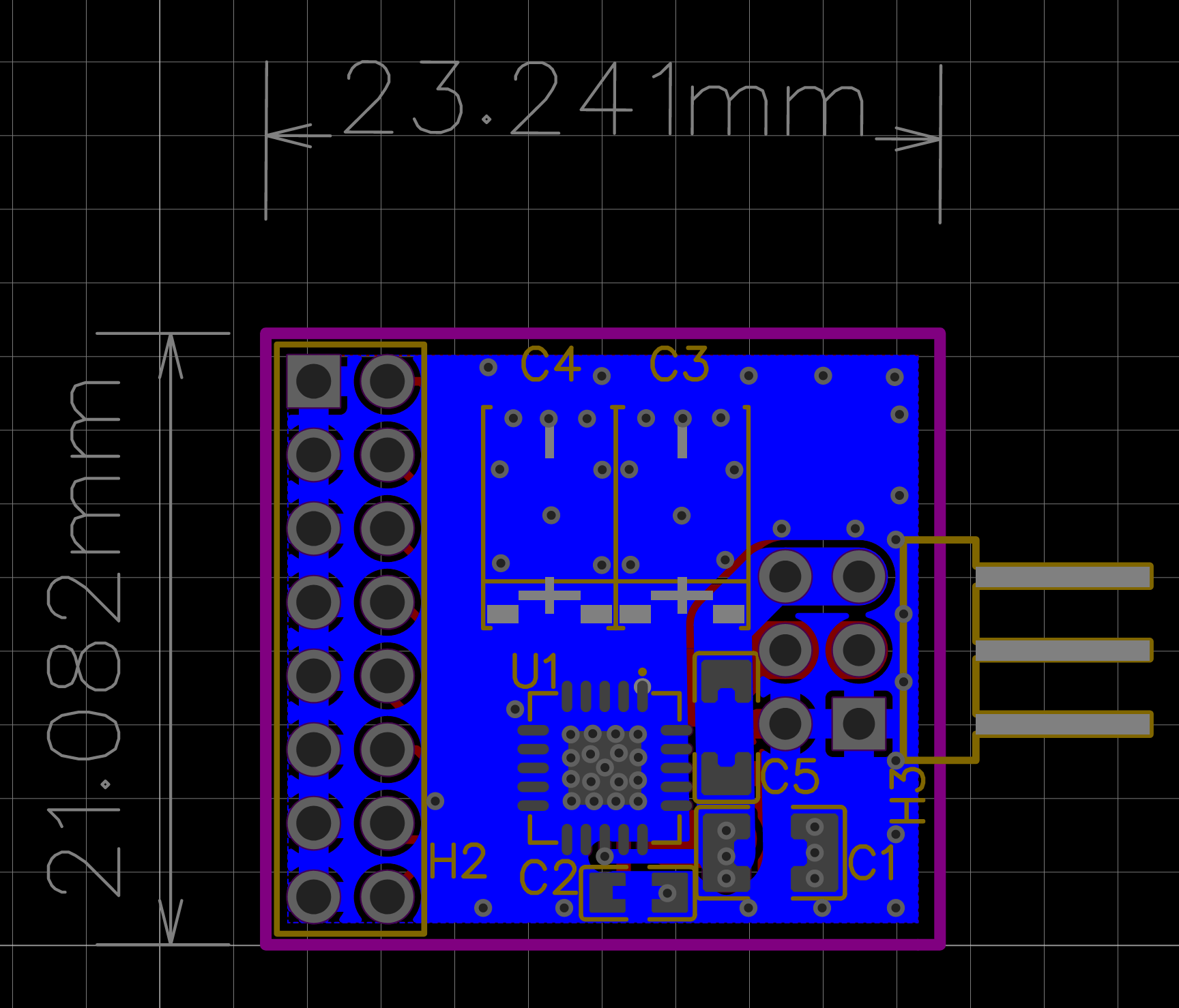

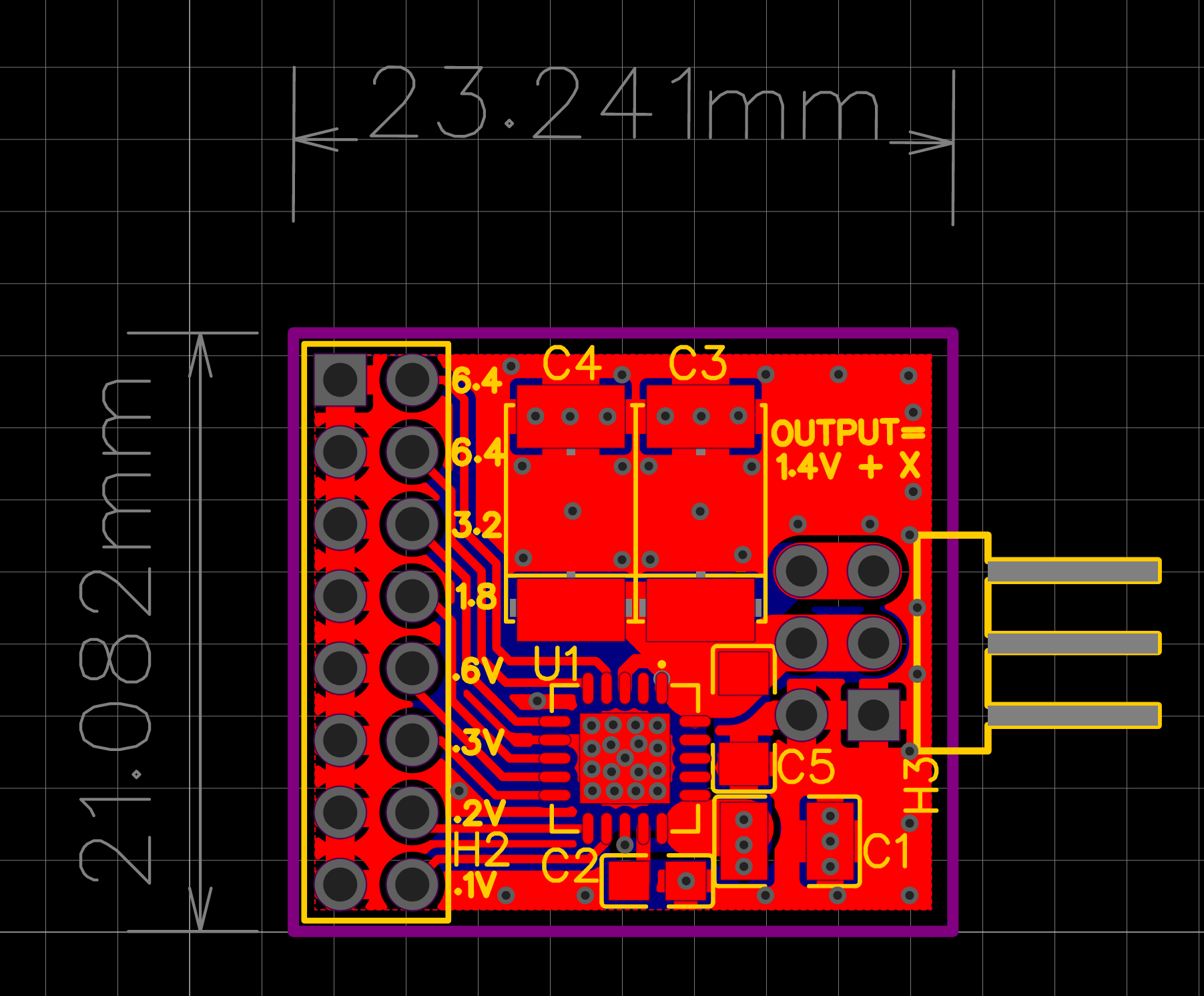

this is how it looks now:

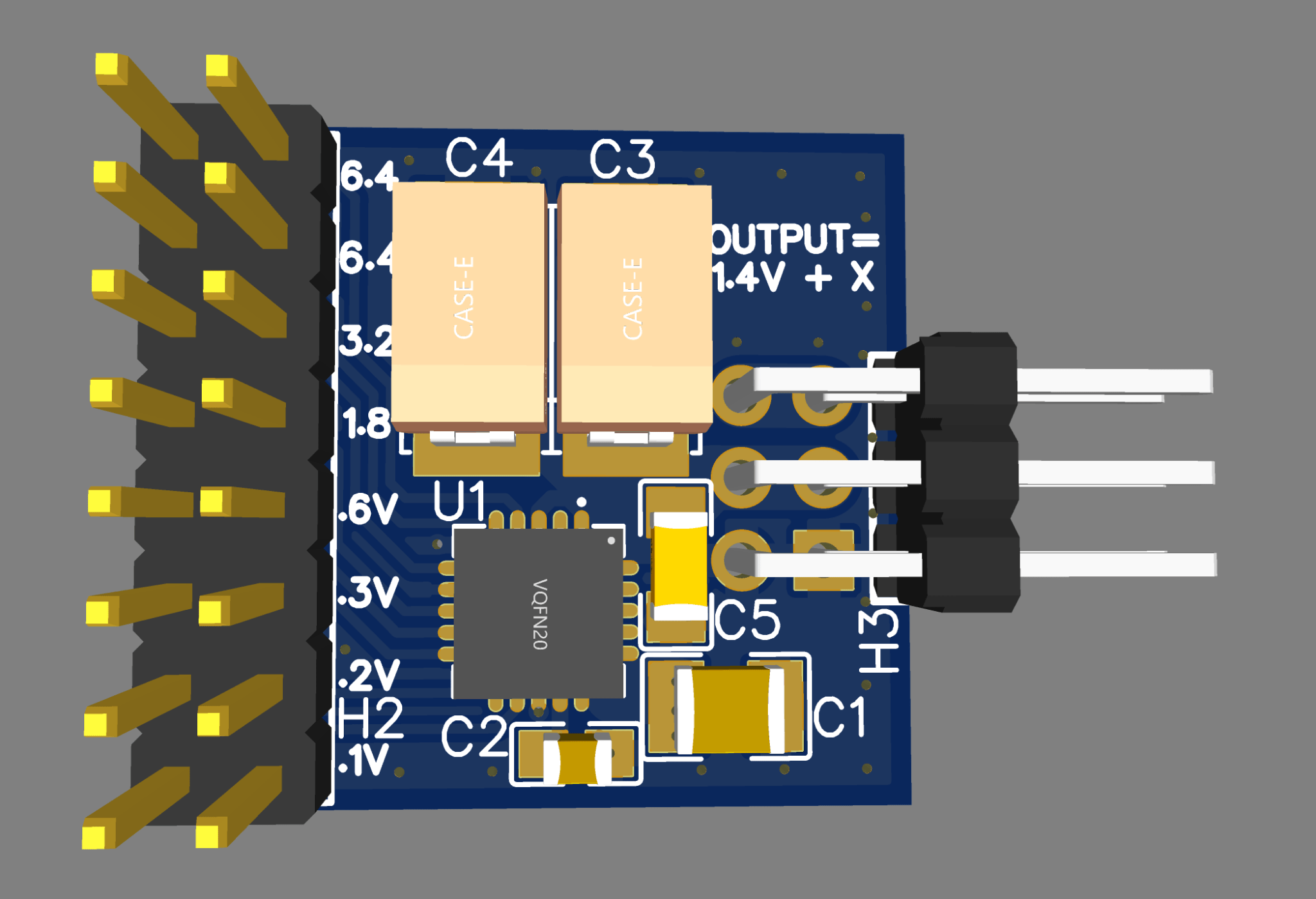

Looks also more tidy with the tant caps

i watched a video about 2layer vs 4layer, so the important part is to keep the overall "loop area" in mind right? i think i done a fairly good job now to keep it small... the tant output caps have the largest loop area, just because of the size

Also i saw the ldvor board uses many vias under the TPS chip, i guess for heat desipation, i also added those

im not as concerned about the tant output caps, they have together only 30mohms ESR + the 100nF C0G

this is how it looks now:

Looks also more tidy with the tant caps

i watched a video about 2layer vs 4layer, so the important part is to keep the overall "loop area" in mind right? i think i done a fairly good job now to keep it small... the tant output caps have the largest loop area, just because of the size

Also i saw the ldvor board uses many vias under the TPS chip, i guess for heat desipation, i also added those

- Home

- Design & Build

- Electronic Design

- TPS74A700 Regulator Board