I think what you are showing from previous posts supports why I claim that a -ve Salas regulator using N channel devices may perform better than +ve regulators.

The irf510 & irf520 have far higher gm as well as lower capacitance, lower Rdson, higher current capability. Even the irf530 & irf540 could be used but there are probably some other devices that achieve better performance at similar cost.

I have stated this many times and actually built a -ve reg from a +ve PCB to prove that it is practical to adopt all +ve regulators.

The irf510 & irf520 have far higher gm as well as lower capacitance, lower Rdson, higher current capability. Even the irf530 & irf540 could be used but there are probably some other devices that achieve better performance at similar cost.

I have stated this many times and actually built a -ve reg from a +ve PCB to prove that it is practical to adopt all +ve regulators.

What matters when used for current gain is Crss for frequency and gfs @ Ibias for Zo. PMOS is quieter than NMOS BTW. All types and schemes have been used in the various ones. NMOS in SSHV and Reflektor, PMOS with and without CFP in SSLV. Even TTL level NMOS. Its a matter of best fitting one VS priorities. SSLV1.1 and 1.2R are very nice subjectively with FSNJFR phono. 35V active Vref and TTL NMOS Reflektor subjective tests will be done also.

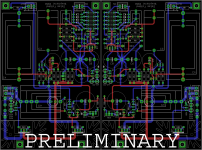

Meanwhile I guide lead spacing dimensional mistakes and errors after what crt sent back under my last guidance. We are slow this time, but nearing to proto worthy. Made space for MCAP EVO in the regs besides various industrial standard pitch, resistors are 1/2W, Z-Foil options, provision for Caddock Rset even. Can anybody pick out the glowing mistake in this one? Hint is I am not joking, there is a party killer repeated mistake there.

Attachments

Have you posted reports on these measurements?................... PMOS is quieter than NMOS................

But you and others report that the Salas regs are very quiet.

Does the alleged Pmos Nmos noise parameter difference make any difference to the noise output and to the audibility of that noise output?

If there is no evidence, then there is no point in highlighting an alleged improvement.

I cannot measure noise that is so low. I cannot help with evidence.

I rely on others telling the parts of the story that I can't fill in.

I rely on the integrity of those others.

If one invents fictitious attributes then I lose respect for that author.

You said that Pmos is quieter than Nmos in respect to building +ve or -ve Salas regulators.

Show the proof, or withdraw the statement

Does the alleged Pmos Nmos noise parameter difference make any difference to the noise output and to the audibility of that noise output?

If there is no evidence, then there is no point in highlighting an alleged improvement.

I cannot measure noise that is so low. I cannot help with evidence.

I rely on others telling the parts of the story that I can't fill in.

I rely on the integrity of those others.

If one invents fictitious attributes then I lose respect for that author.

You said that Pmos is quieter than Nmos in respect to building +ve or -ve Salas regulators.

Show the proof, or withdraw the statement

Last edited:

It would take wide band high dynamic range professional spectrum analyzer with very careful tests to see that, a machine that I don't own. I referred to intrinsic PMOS-NMOS character with a BTW. Not meant that the regs I made with one or another had an overall important impact difference to phono stages noise floor. Given that the voltage reference contributes the same between them.

If one invents fictitious attributes then I lose respect for that author.

You said that Pmos is quieter than Nmos in respect to building +ve or -ve Salas regulators.

Show the proof, or withdraw the statement

Don't make dcb1s and SSLVs for you and your friends then and don't respect the author. I will resign from IEEE after that humiliation.

Can I suggest that your comment made to look like "fact" is irrelevant to the discussion on -ve vs +ve Salas regulators?

Alright, posting shortly can do that, no worries.

Salas,

you choose whether to leave your original comment in the Forum.

I never remove content. A scientist might see it and tell us if it can make a real difference for regs use even.

But did you find the error yet? Hint 2 to help: "CAD mirroring".

Q2 and Q1?

Thought so too from the .png. But now I got a .brd file also that I can zoom dynamically to see that a blue line is connecting right hiding exactly under a red. So its a pass!

Nice

- Home

- Source & Line

- Analogue Source

- Simplistic NJFET RIAA