Just for clarity, I meant: don't they distort substantially when used as inductors rather than as transformers? I know good signal transformers can have low distortion levels when they are used for the purpose they are meant for and driven from a low impedance.

Well, good ones probably distort a lot less than cheap ones. Substantial high-nickel cores driven in their more linear region are probably better, but also cost more.

Also, they can filter when simply used as transformers. Laminated cores are lossy at RF, and if there is high quality electrostatic shielding between primary and secondary then that would help a lot too. Thus there may be a lot less RF left to filter after passing the dac output through a transformer.

Also, they can filter when simply used as transformers. Laminated cores are lossy at RF, and if there is high quality electrostatic shielding between primary and secondary then that would help a lot too. Thus there may be a lot less RF left to filter after passing the dac output through a transformer.

Last edited:

These are the transformers I am using:

https://www.lundahltransformers.com/wp-content/uploads/datasheets/1588.pdf

When I bought them they were significantly cheaper than the £110 each I see them listed for now. However I did buy them direct from Lundahl through their UK sales person which saved a bit.

I bought them for another project a couple of years before the RTZ came to my attention. They just happen to sound really good when used with the opa1632 based filter - perhaps it is just the synergy with my amplifier - I am not sure.

https://www.lundahltransformers.com/wp-content/uploads/datasheets/1588.pdf

When I bought them they were significantly cheaper than the £110 each I see them listed for now. However I did buy them direct from Lundahl through their UK sales person which saved a bit.

I bought them for another project a couple of years before the RTZ came to my attention. They just happen to sound really good when used with the opa1632 based filter - perhaps it is just the synergy with my amplifier - I am not sure.

After a product inquiery, I was invited and visited Mr Lundahl at his office/production facility. A very nice experience which gave high confidence in the products. I bought since then I think 3 pairs of different transformers - the first I used to build a passive I/V stage for an ESS based DAC (Acko AKD12P) by using MC trafos and high quality 15 ohm R on the secondary.

//

//

Here you go:I don't know what the "original filter design" was, though (can seem to find it right now).

View attachment 1300188

It is easily observed that the input impedance depends on the open loop gain and is effectively as a result inductive.

The 8.2nF Capacitors forms a parallel resonant circuit with this "virtual inductance".

If we remove them....

So for HF out input impedance is around 300 Ohm differential, I expect these are the 760 Ohm DAC source impedance and the 510 resistance inside the feedbackloop (760R//510R = 305 Ohm).

Also, gentlemen, I feel you are not just overegging the pudding but you are going full on Billy Joel by trying to move all passive filtering to the front.

I'm fine with extremes, but do we have a middle ground?

Let's take Zsrc = 380R and Z load = 260R and a total capaictance of 8.2n and see what filter we can get?

A 320k cutoff with a 5th order response should allow significant rejection of HF stuff, with inductor and capacitor values that are rather managable.

Looks to me a material improvement in filtering high frequency stuff, while noise gains and audio band behaviour are largely unchanged.

Blue original, red the filter I showed. If we go simple CLC (3rd order) like I have used in commercial products the difference is further reduced:

Much simpler, is the filter response sufficiently similar? Answers on a postcard.

Thor

Attachments

Last edited:

An article on making audio frequency filters using transformers: https://ka7oei.blogspot.com/2013/01/an-lc-audio-bandpass-filter-using.html

Something like this occurred to me previously, which is to say, thinking about using transformers in filters even if only as simple inductors. Regarding self resonance and effectiveness at RF frequencies, seems to me the transformer/inductors may become usefully lossy at higher RF frequencies.

When you operate a transformer as inductor, you are effectively using @unwanted parasitic. It may work, but a much less expensive OTS inductor may do better. Up to 1mH are fairly easily found in SMD.

If you use a transformer intentionally, a correctly designed terminated Transformer is a 2nd order bandpass.

While experimenting with ESS DAC Chip's which run at very high speeds and dump considerable RF energy downstream, the best solution I found was a high grade microphone transformer, which also presented a relative load impedance to the DAC, less than purely voltage out but more than active I/U conversion.

This was followed by a buffer. It ended up with a very low distortion cathode follower (similar to Allen Wright SLCF) with two tubes per channel.

It is certainly a valid solution to making a DAC. It would likely also work on the FIR DAC.

Thor

Last edited:

That also contributes, but I meant through the source follower action of the PMOS.

View attachment 1299510

The simplest way to make a TTL compatible input on a 5 V CMOS chip is just to scale the width-length ratios of the input inverter a bit, but with a PMOS threshold voltage of about -0.7 V, you then essentially have a PMOS source follower from the input to the 5 V reference supply for any input voltage from the switching point to 4.3 V.

I think we can agree, that the 74AHCT16374 does not suffer this problem.

It does seem to offer a number of advantages over dual 74LV574. Looking at the switching characteristics I do not see really any disadvantage uisng 74AHCT16374 over 74LV574 in this case.

Having a symmetrical flow through layout, 8 GND and 4 VCC pin's vs only 2 each all do better.

I cannot find the Supply Current Versus Input Voltage graph for LV, so it is debatable which device creates less disturbance on the reference (DAC Supply) voltage when level shifting from 3.3V to 5V.

Hence I would suggest that IF a new layout is made, the 74AHCT16374DGVR (TVSOP-48) is considered as DAC.

Additionally, adding either a trim Capacitor (appx. 3.3pF) or one input from an AHCT (or whatever logic is used) Gate at the final output pair (that is unloaded except for the DAC resistor) should be considered to ensure all outputs behave as identical as possible.

Additionally, I think options for the clock system might also be good, with stuffing option based selection. A 50 Ohm SMA connector makes an excellent choice, We could incorporate a clock tree with suitable fanout using either dedicated clock buffer IC's or Picogate logic, which might also help the current design.

Personally I'd likely use NC7WZU04PX or equivalent (e.g. SN74LVC2GU04), essentially improved LVC unbuffered inverters with appx. 15 Ohm Zout. Likely 3pcs, one buffers the MCK and then drives 5 more inverters in the 3 packages. Due to skew each DAC should be driven from one output, and the same chip. Use a 36R series resistor and a 50Ohm strip line splitting into two exactly equal length and mechanical arrangement 100 Ohm strip lines to each clock pin. Generally, a series pair of unbuffered inverters add very little phase noise and / or jitter to the clock. Three more controlled impedance clock lines would be available for remainder of the circuit.

Just my suggestions (take them as worth what you paid for them) should a new layout be made.

Thor

I cannot find the Supply Current Versus Input Voltage graph for LV, so it is debatable which device creates less disturbance on the reference (DAC Supply) voltage when level shifting from 3.3V to 5V.

To the best of my knowledge 74LV logic cannot level shift from 3.3 V to 5 V, not reliably anyway. (Nor does it need to in my circuit, all signals going to the SN74LV574As are already at 5 V.) The specified minimum high input voltage is 70 % of the supply voltage, so that's 3.5 V at 5 V and 3.675 V at 5 V + 5 %.

To the best of my knowledge 74LV logic cannot level shift from 3.3 V to 5 V, not reliably anyway. (Nor does it need to in my circuit, all signals going to the SN74LV574As are already at 5 V.)

Ahhh, yes I missed that. All your logic is 5V using popcorn logic that is true 5V rated LVC. Interfacing is done using AHCT at the input.

It's a great Idea, I'll have to steal it.

Thor

Due to skew each DAC should be driven from one output, and the same chip. Use a 36R series resistor and a 50Ohm strip line splitting into two exactly equal length and mechanical arrangement 100 Ohm strip lines to each clock pin. Generally, a series pair of unbuffered inverters add very little phase noise and / or jitter to the clock.

Agree. Was thinking about broaching the subject at some point as my clock board will use buffers.

Just my suggestions (take them as worth what you paid for them) should a new layout be made.

Incidentally, I should perhaps just mention my own project will use 74ALVC164245 (currently in mass production from TI, NXP and Renesas) as actual bit switches. These should run at around 1...1.5nS actual in circuit delay.

Their logic is thus that the 5.5V "B" side only has the output pair on the Vcc pin's, all other logic reverences to the "A" side.

I think that this makes sure to minimise any impact on the analogue reference / supply by the switching and equally minimises any switching noise, issues from loading by inputs of the next stage etc. The idea is to completely separate switching timing and all logic from the actual DAC.

While perhaps stretching level translation abilities a bit, if I run the input on 3V and 74AUC/AVC/LXC/VCX16374 at 2.7V the system should operate reliably with the 74XXX16374 providing the delay chains.

I intend to use a much larger number of Bit's than Marcel, probably 4 X 8 balanced drive by a balanced chain of 16374 with staggered bit assignment, meaning bit 0/2/4/6/8/10/12/14 goes to the first DAC, 1/3/5/7/9/11/13/15 goes to the second DAC, 2/4/6/8/10/12/14/16 goes to the third DAC, 3/5/7/9/11/13/15/17 goes to the fourth DAC.

Despite having 32 Bit Switches - the delay is only 17 BCK and a lot of time interleaving goes on, to hopefully scramble a lot of the errors.

Overall Kaiser Window function, though I'll also test unitary weighting.

Operation will be DSD256 fixed with 75% RTZ and an MCK at 4 X build up from 74AUC/AUP/AVC etc. popcorn logic.

This is just a "denkanstoss" for those working more in depth with this kind of DAC. Don't expect or ask for a fully ready design from me.

Thor

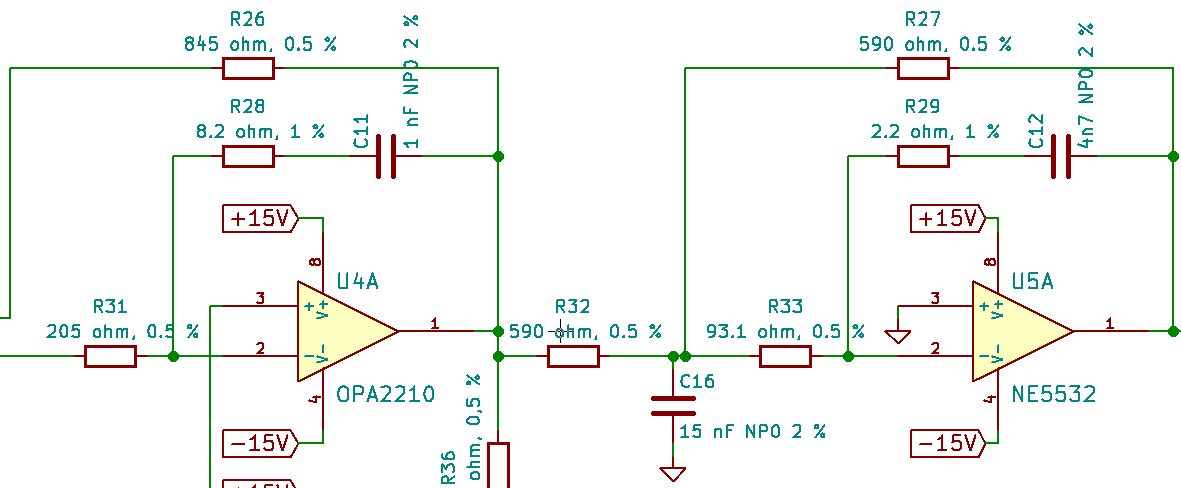

Actually, the least invasive filter change I can come up with is just to put the section with the highest quality factor first: op-amps stay the same, PCB stays the same, resistor and capacitor values change. It comes with a small noise penalty because the noise gain at 20 kHz for the first stage increases slightly. The input impedance actually goes down. Changes:

Change the capacitors on the DAC board from 8.2 nF NP0/C0G 2 % to 22 nF NP0/C0G 2 %.

Change most resistors and capacitors on the filter board, like this:

See also the attachment. The third stage is still as optional as it always was.

It should reduce the spurs around fs/2 that reach the first op-amp by about 7 dB. As the audio products are second-order intermodulation products, those should theoretically drop by about 14 dB if this is the only cause of the intermodulation.

Change the capacitors on the DAC board from 8.2 nF NP0/C0G 2 % to 22 nF NP0/C0G 2 %.

Change most resistors and capacitors on the filter board, like this:

See also the attachment. The third stage is still as optional as it always was.

It should reduce the spurs around fs/2 that reach the first op-amp by about 7 dB. As the audio products are second-order intermodulation products, those should theoretically drop by about 14 dB if this is the only cause of the intermodulation.

Attachments

Since we are sharing some information today and in particular on the topic of inverters as buffers, a professional dac designer acquaintance told me the best inverter/buffer he had found for low phase noise is Microchip PL133-27

Not so easy to hand solder though.

Not so easy to hand solder though.

Actually, the least invasive filter change I can come up with is just to put the section with the highest quality factor first:

It should reduce the spurs around fs/2 that reach the first op-amp by about 7 dB. As the audio products are second-order intermodulation products, those should theoretically drop by about 14 dB if this is the only cause of the intermodulation.

The weird low-level distortion should get better, but the plain harmonic distortion at 10 kHz, 0 dB DSD may get worse.

Just a thought - WRT transformers, a zero field transformer may be a worthwhile option to try right in front of the 1632. These are essentially a current in / current out device with very low distortion.Not the ones Cinemag made for Quadratic Audio, nor some prototype line level transformers here (still under NDA unfortunately). IIUC Cestrian is using some Lundhal transformers that may be pretty good. Of course, they may not be low-cost.

Also, if transformers filter out RF in a way that sounds better than, say, opamps, then they may be more fit for purpose than, again, say, opamps. Just saying if the goal is to satisfy human perception of a very close to real listening experience, PSS distortion is not the only factor that affects the end goal (as Paul Frindle found out).

In some ways it will function somewhat opposite an RF (pre OPA) inductor in that the core running out of BW > audio frequencies is your friend.

Since we are sharing some information today and in particular on the topic of inverters as buffers, a professional dac designer acquaintance told me the best inverter/buffer he had found for low phase noise is Microchip PL133-27

A few observations.

Inverters are used in clock trees as with correct (or decent "by the seats of pants" engineering) we can be reasonably sure that unequal rise and fall times do not accumulate, unlike it would be the case with non-inverting buffers:

In principle, LVC Buffers should be good. Most other logic has issues.

What I am proposing with unbuffered inverters (strictly unbuffered) is to make a discrete fanout that is non-inverting.

I remember from a Wenzel publication that a single 74AC inverter (buffered) as squarer ends up not compromising -130dBc @ 10Hz phase noise from a 10MHz reference oscillator (meaning it's own noise is much lower) and even at 1Hz was only 1dB worse (which may be other parts of the circuit).

The NC7WZU04 dual inverter is functionally similar to the PL133, minus the OE option. It has the advantage of having multiple parallel parts from a range of sources, I learned the hard way to avoid single vendor parts as possible.

My personal "seat of pants" clock tree engineering assumes a 50R stripline is around 1.5pF/cm.

Typically we drive at least two inputs per inverter, which we call 10pF plus 10cm stripline is 25pF. Less we can always maeander the line or add a trim cap at the beginning.

So each inverter is loaded by appx. 25pF, if we now load the first inverter with 5 inputs of 5pF each, all inverters have approximately identical rise and fall times and the net result should preserve out 50% duty cycle clock.

As noted, one or two inverters are unlikely to materially impact the phase noise from most readily available clocks. An Accusilicon AS318 with -90dBc @ 10Hz is unlikely to challenge one or two inverters with < -130dBc @ 10Hz, even if our gates have 20dB more noise and only give us -110dBc - I think no point to loose sleep. The PL133 seems to have worse phase noise performance, but in the graph in the datasheet the source has likely more phase noise than PL133 below ~500Hz.

So, my logic for recommending a 1:5 fanout using 3pcs NC7WZU04 is:

Adequate phase noise performance

Preserves Duty Cycle in our application

Inexpensive and readily available parallel parts from multiple suppliers

It is not specified for the job, but it should do fine.

Thor

Just a thought - WRT transformers, a zero field transformer may be a worthwhile option to try right in front of the 1632. These are essentially a current in / current out device with very low distortion.

Nope, they are not. They are just very conventional transformers, which are operated with a mix of positive and negative feedback. It is the positive feedback (or negative resistance) that actually makes it zero field (from Lundahl):

As the "Zero Field" feedback extends bandwidth it will "broadband" the transformer and in effect counteract it's filtering effect.

Transformers that will only be used in Zero Field can be smaller and less expensive than those for normal use, however traditional Transformers work fine in zero field as well.

Ideally with Zero Field we would trim out all the DCR of the transformer windings, but copper is not constantan and thus we need account for a variations in temperature and actual winding resistance tolerance. So we never get the equivalent of "0 Ohm" input impedance at the transformer and the field is never zero.

With the OPA1632 (or a Birt based design) it is not really easy to apply the required positive feedback. So at best we run the transformer into a virtual ground.

If we take an OEP 1:10 step-up A187A15C we have 20 Ohm primary DCR and 1.59k secondary DCR. This means without compensating the DCR by positive feedback, we add 36 Ohm to the circuits input impedance. If we take a 600R:600R 1:1 transformer (A187A12C) we add almost 100 Ohm DCR so this is worse.

I'm not really sure this is a good place for a transformer. I think the Analogue stage would need to be completely redesigned with the correct zero field circuit and ideally R3 would be thermally coupled with the transformer case and be made from pure copper, so the circuit is inherently temperature compensated.

Thor

Based on datasheets LMK1C110x is much better in every respect.the best inverter/buffer he had found for low phase noise is Microchip PL133-27

Close-in phase noise of LMK1C110x is also very good:

https://e2e.ti.com/support/clock-ti...2-residual-phase-noise-plot-for-the-lmk1c1102

So even at -87dBc@1Hz the source seems to be the limitation. And that is for 100MHz clock.

Yes, negative resistance topology well documented by Lundahl. They can also be implemented successfully without NR using a low DCWR traffo (Studer / Neve did). I have used them in front of DAC I-V's sans NR but the I-V's were open loop so no real gains to be had given the I-V was fairly immune to any DAC RF. Main gains were just making the 0FB I-V more linear. Given low(ish) OP Z DACs (Sabre / this one), difficult to acheive good linearity with ZFB I-V without crazy high currents so back to opamps. PS I was thinking more low DCR, 1:1 ratio and an appropriately large core to achieve desired LF linearity.Nope, they are not. They are just very conventional transformers, which are operated with a mix of positive and negative feedback. It is the positive feedback (or negative resistance) that actually makes it zero field (from Lundahl):

View attachment 1301509

As the "Zero Field" feedback extends bandwidth it will "broadband" the transformer and in effect counteract it's filtering effect.

Transformers that will only be used in Zero Field can be smaller and less expensive than those for normal use, however traditional Transformers work fine in zero field as well.

Ideally with Zero Field we would trim out all the DCR of the transformer windings, but copper is not constantan and thus we need account for a variations in temperature and actual winding resistance tolerance. So we never get the equivalent of "0 Ohm" input impedance at the transformer and the field is never zero.

With the OPA1632 (or a Birt based design) it is not really easy to apply the required positive feedback. So at best we run the transformer into a virtual ground.

If we take an OEP 1:10 step-up A187A15C we have 20 Ohm primary DCR and 1.59k secondary DCR. This means without compensating the DCR by positive feedback, we add 36 Ohm to the circuits input impedance. If we take a 600R:600R 1:1 transformer (A187A12C) we add almost 100 Ohm DCR so this is worse.

I'm not really sure this is a good place for a transformer. I think the Analogue stage would need to be completely redesigned with the correct zero field circuit and ideally R3 would be thermally coupled with the transformer case and be made from pure copper, so the circuit is inherently temperature compensated.

Thor

Last edited:

They can also be implemented successfully without NR using a low DCWR traffo (Studer / Neve did).

That depends on a lot of factors. Studer did it as microphone input. And technically, the still fairly high DCR doesn't make that one "zero field", just low field.

PS I was thinking more low DCR, 1:1 ratio and an appropriately large core to achieve desired LF linearity.

The point of ZF is to use a small core. LF linearity is achieved by cancelling the LF magnetic field.

Here an example of the same 1:1 600R transformer (50 Ohm resistors model the DCR) in Zero Field, inverting "low field" and normal operation.

Curves are at the Voltage meters. Low field at 10Hz is down by 46dB on standard connection, but true zero field is -123dB.

Based on datasheets LMK1C110x is much better in every respect.

Not really my readng

Close-in phase noise of LMK1C110x is also very good:

So even at -87dBc@1Hz the source seems to be the limitation. And that is for 100MHz clock.

Yes, but it's likely no better than a pair of suitable CMOS inverters. So I have doubts that there is any reason to chose a single source, 8 times more expensive device.

Thor

- Home

- Source & Line

- Digital Line Level

- Return-to-zero shift register FIRDAC