Did YOU photoshop the alternative circuit? I can't see it in the original paper.

I think they are equivalent and that the common mode of 0 is nice to have.

Fooled you

These guys from ETH Zürich have invested a lot more in constant temperature:

< https://aip.scitation.org/doi/10.1063/1.4997963 >

Not so much for noise but for 100 fA DC input current with those fat IF3602 FETs.

Any more info, did they do that with matched singles in separate TO-5 cans? They must have been chilly.

Syn

How does your MM 4.2 compare to what Gerhard is doing?

Sorry, no idea.

Any more info, did they do that with matched singles in separate TO-5 cans? They must have been chilly.

The link points to the .pdf that discloses everything. They enforced 20°C with Peltiers,

selected parts and even compensated the bias current.

They use the dual version IF3602, which is a good idea because you don't get

opposite outliers combined. But that is still a far cry from "matched" for > €50 a pop.

Id over Vgs for 8 pairs of IF3602. That was not a cheap measurement.

I have some more of them, but they were soldered in somewhere.

< 8pcs_IF3602 | 8 pairs of Interfet IF3602 JFETs Id vs Vgs | Gerhard Hoffmann | Flickr >

There are combinations that definitely make no sense to use in parallel, like Q2

and Q7. At Vgs = -0.45V, the Q7(red/black) pair would be wide open while

Q2 (light blue/ greenish-brown) is still completely cut-off.

cheers,

Gerhard

Last edited:

Gerhard,

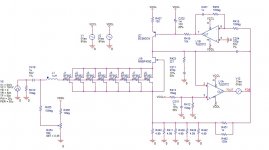

I see Waly already posted (with due credit) my latest idea for a LNA servo. Here's the latest incarnation of my 60dB gain LNA.

The driver behind this was twofold; first I was really curious if biasing the low noise jfets well beyond the Idss (which I was using in previous LNAs) will tame those pesky very low frequency flickers, that will saturate the LNA output at gains of 80dB or so, and secondly to determine the input equivalent voltage noise on Id (both at flat and at 10Hz). Previous 8xBF862 running at a total of about 100mA reached 0.33nV/rtHz flat, but a dissapointing 4-5nV/rtHz at 10Hz.

Since I'm rather shy in connecting a servo at the amp input, I chose to keep the active load servo and bias the gates at a fixed voltage, as you also did. The servo has an extra pole determined by the 10k/1000uF opamp output cell, which requires an equivalent zero in the servo loop to avoid a big low frequency gain bump. The extra pole was added to filter with 40dB/dec the servo opamp noise, but it turned out I overreacted; there's almost no difference in noise with and without this extra cell; one can pull C202 and set R416 and R453 to zero ohm, further simplifying the schematic. As shown in the schematic, the 3dB bandwidth is about 100Khz, starting from .7Hz, with a healthy stability margin. One can try to further optimize the bandwidth, I would suspect it can be easily pushed up to 200KHz, if required, which would render an equivalent 200MHz GBW, not too shabby for a discrete implementation.

Now, regarding the noise performances:

I tried 3 types of low noise JFETs, the now extinct BF862 (I have a lifetime stock ) the OnSemi 2SK3557 (also found in the CPH5905 BJT cascode) and the OnSemi CPH3910. All were set to run at 1mA/jfet (8mA total) by adjusting the on board multiturn pot.

) the OnSemi 2SK3557 (also found in the CPH5905 BJT cascode) and the OnSemi CPH3910. All were set to run at 1mA/jfet (8mA total) by adjusting the on board multiturn pot.

- The winner was still the BF862, with 0.44nV/rtHz equivalent input noise.

- There was virtually no difference between the 2SK3557 and the CPH3910, other than some random statistic fluctuation (certainly due the process) at about 0.5nV/rtHz, so a smidge worse than the BF862. This is telling me that the OnSemi devices are sharing the same silicon. The noise performance shows that not everything is lost with the demise of the popular NXP BF862 JFET. For further massive scaling for even lower noise, the OnSemi devices have a major advantage, though: they have Ciss=6pF compared to the 10pF for the BF862.

- All devices delivered a 10Hz equivalent input noise of anywhere between 1.4 and 2.5nV/rtHz, randomly, no correlation with the device type was identified. I suspect one could go lower with sorting the devices for low GR noise, I didn't bother.

Some conclusions:

- Low noise fluctuations of allegedly thermal origin decreased significantly when lowering the Id (and hence the power dissipation). Scott could be right, these fluctuations could be due the convection at board level, although a previous model running at Idss and enclosed in 1/2" of metal has the same fluctuations amplitude and frequency (on average, once every 3-4 seconds) as in free air. Interesting enough, the fluctuation frequency for the low power case remained the same, only the amplitude decreased significantly. I am still puzzled by these fluctuations, which, BTW, are specific to the sigle ended topology. Never seen such in any op amp or discrete differential implementation.

- Flat noise. Already mentioned, BF862 is (without any sorting) still the winner, by a smidge. Regarding the noise increase, the 1/4 power law for noise decrease with Id is optimistic; experimentally, the exponent value was found anywhere between 1/6 and 1/8. So running the JFETs at low current is not degrading the noise performance as badly as expected by the 1/4 power law.

- Finally, indeed running the JFETs at low current significantly lowered the 10Hz noise, by a factor of about 2. These results are still far from those reported elsewhere (1nV/rtHz @ 10 Hz) - I have no idea why. The LF excess noise slope was confirmed to be quite close to the theoretical 1dB/decade.

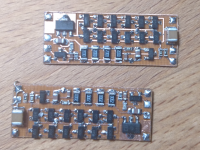

I'm attaching a photo of the LNA board; it includes two ultra low noise requlators (+/- 9V) built with the TI latest ICs (TPS7A4700 and TPS7A33). These are also some sort of "luxury" since the PSRR of the LNA is excellent, anyway. One can simply feed the LNA from a couple of 9V batteries, since it takes about 10mA from the positive supply and about 2mA from the negative supply (plus whatever the LEDs are chosen to). Without the LDO regulators, the thing takes about 4cm^2 of PCB asset.

P.S. The input cap is a rather new 1uF 1206 film device http://www.cde.com/resources/catalogs/FCA.pdf To my surprise, it is of excellent quality, zero microphonics and very low leakage. DigiKey has them in stock.

I see Waly already posted (with due credit) my latest idea for a LNA servo. Here's the latest incarnation of my 60dB gain LNA.

The driver behind this was twofold; first I was really curious if biasing the low noise jfets well beyond the Idss (which I was using in previous LNAs) will tame those pesky very low frequency flickers, that will saturate the LNA output at gains of 80dB or so, and secondly to determine the input equivalent voltage noise on Id (both at flat and at 10Hz). Previous 8xBF862 running at a total of about 100mA reached 0.33nV/rtHz flat, but a dissapointing 4-5nV/rtHz at 10Hz.

Since I'm rather shy in connecting a servo at the amp input, I chose to keep the active load servo and bias the gates at a fixed voltage, as you also did. The servo has an extra pole determined by the 10k/1000uF opamp output cell, which requires an equivalent zero in the servo loop to avoid a big low frequency gain bump. The extra pole was added to filter with 40dB/dec the servo opamp noise, but it turned out I overreacted; there's almost no difference in noise with and without this extra cell; one can pull C202 and set R416 and R453 to zero ohm, further simplifying the schematic. As shown in the schematic, the 3dB bandwidth is about 100Khz, starting from .7Hz, with a healthy stability margin. One can try to further optimize the bandwidth, I would suspect it can be easily pushed up to 200KHz, if required, which would render an equivalent 200MHz GBW, not too shabby for a discrete implementation.

Now, regarding the noise performances:

I tried 3 types of low noise JFETs, the now extinct BF862 (I have a lifetime stock

- The winner was still the BF862, with 0.44nV/rtHz equivalent input noise.

- There was virtually no difference between the 2SK3557 and the CPH3910, other than some random statistic fluctuation (certainly due the process) at about 0.5nV/rtHz, so a smidge worse than the BF862. This is telling me that the OnSemi devices are sharing the same silicon. The noise performance shows that not everything is lost with the demise of the popular NXP BF862 JFET. For further massive scaling for even lower noise, the OnSemi devices have a major advantage, though: they have Ciss=6pF compared to the 10pF for the BF862.

- All devices delivered a 10Hz equivalent input noise of anywhere between 1.4 and 2.5nV/rtHz, randomly, no correlation with the device type was identified. I suspect one could go lower with sorting the devices for low GR noise, I didn't bother.

Some conclusions:

- Low noise fluctuations of allegedly thermal origin decreased significantly when lowering the Id (and hence the power dissipation). Scott could be right, these fluctuations could be due the convection at board level, although a previous model running at Idss and enclosed in 1/2" of metal has the same fluctuations amplitude and frequency (on average, once every 3-4 seconds) as in free air. Interesting enough, the fluctuation frequency for the low power case remained the same, only the amplitude decreased significantly. I am still puzzled by these fluctuations, which, BTW, are specific to the sigle ended topology. Never seen such in any op amp or discrete differential implementation.

- Flat noise. Already mentioned, BF862 is (without any sorting) still the winner, by a smidge. Regarding the noise increase, the 1/4 power law for noise decrease with Id is optimistic; experimentally, the exponent value was found anywhere between 1/6 and 1/8. So running the JFETs at low current is not degrading the noise performance as badly as expected by the 1/4 power law.

- Finally, indeed running the JFETs at low current significantly lowered the 10Hz noise, by a factor of about 2. These results are still far from those reported elsewhere (1nV/rtHz @ 10 Hz) - I have no idea why. The LF excess noise slope was confirmed to be quite close to the theoretical 1dB/decade.

I'm attaching a photo of the LNA board; it includes two ultra low noise requlators (+/- 9V) built with the TI latest ICs (TPS7A4700 and TPS7A33). These are also some sort of "luxury" since the PSRR of the LNA is excellent, anyway. One can simply feed the LNA from a couple of 9V batteries, since it takes about 10mA from the positive supply and about 2mA from the negative supply (plus whatever the LEDs are chosen to). Without the LDO regulators, the thing takes about 4cm^2 of PCB asset.

P.S. The input cap is a rather new 1uF 1206 film device http://www.cde.com/resources/catalogs/FCA.pdf To my surprise, it is of excellent quality, zero microphonics and very low leakage. DigiKey has them in stock.

Attachments

Last edited:

How is the drain voltage on JFet 1 .. 8 ? Thanks.

For an average MMBF4392, about 2.5...3V.

Last edited:

For an average MMBF4392, about 2.5...3V.

OK, I see type BF862 is well behaved at drain voltages like this.

Last edited:

OK, I see type BF862 is well behaved at drain voltages like this.

So are the OnSemi devices; at the same Idss they have just a little lower Vp (but still > -1V). Even the CPH3910, or the high Idss grade of the 2SK3557, are still happy with the MMBF4392 resulting Vds @ 1mA Id. The saturation condition is here |Vds|>|Vp|, since Vgs is virtually zero, so any JFET with Vgs<-2V @ 8mA is good as cascode. One can try to increase the drain currents to, say, 3mA (a total of 24mA) then a) the top current source resistor has to be decreased proportionally and b) use MMBF4391, the higher Idss grade device, as cascode.

I see people using Fets at drain voltage as low as 0.6 volts ..

Yes it can work better than one might think. I had to make a medical part that used a 1V Vp process that had to work at the end of life voltage of a single cell.

Yes it can work better than one might think. I had to make a medical part that used a 1V Vp process that had to work at the end of life voltage of a single cell.

My only concern going so low, in particular for high gain feedback amplifiers, is what happens when the amp saturates the output by bumping into the rails. Once the feedback loop loses control, if Vds decreases further, then you lose control of the JFET and this may trigger a latch-up condition (if the phase inverts). That’s why i think it is always good to have a little margin in the Vds.

Some conclusions:

- Low noise fluctuations of allegedly thermal origin decreased significantly when lowering the Id (and hence the power dissipation). Scott could be right, these fluctuations could be due the convection at board level

- Flat noise. Already mentioned, BF862 is (without any sorting) still the winner, by a smidge. Regarding the noise increase, the 1/4 power law for noise decrease with Id is optimistic; experimentally, the exponent value was found anywhere between 1/6 and 1/8. So running the JFETs at low current is not degrading the noise performance as badly as expected by the 1/4 power law.

The first point is interesting (seeing it only single ended) maybe worth a look. I was also thinking along the lines of do acoustic phonons have an equivalent to shot noise and hence a temperature uncertainty? I don't know if that question even makes sense.

The 1/4 law eventually fails due to subthreshold behavior at the low end, BTW I made a mic running a 2SK222 at 10uA and it sounded fine.

Iirc there's a decent body of research into describing phonon dispersion with a Boltzmann distribution (there's your shot noise), but it's for extremely small dimension materials (nanowires, primarily).

Or are you talking about this, Scott: Phonon noise - Wikipedia ?

Or are you talking about this, Scott: Phonon noise - Wikipedia ?

Or are you talking about this, Scott: Phonon noise - Wikipedia ?

Thanks never came across that before, now the problem is the theory around 1/f of this.

The first point is interesting (seeing it only single ended) maybe worth a look. I was also thinking along the lines of do acoustic phonons have an equivalent to shot noise and hence a temperature uncertainty?

For what is worth, I've seen the same fluctuations in single ended bipolar low noise stages, 4 x low noise BJTs running @ Ic=10mA each (for minimum voltage noise), voltage noise was in total 0.28nV/rtHz, current noise was 5pA/rtHz (yes, those extinct ultra low noise Hitachi 2SC2547 BJTs not only have 0.5nV/rtHz a pop, but also beta > 500, amazing for the early 80's when they were developed, all I know they were in a process with polysilicon emitter).

So the issue is not JFET specific, another reason why I suspect the issue is of thermal origin.

So the issue is not JFET specific, another reason why I suspect the issue is of thermal origin.

Although these issues are probably too obscure for general interest here I confirmed the results of this paper with the BF862 in extremely high impedance applications (1/f Electrical Noise in Planar Resistors: The Joint Effect of a Backgating Noise and an Instrumental Disturbance, José-Ignacio Izpura). The result being an inherently 1/f spectrum from a distributed R/C process. Heat flow obeys diffusion equations which are similar to distributed R/C networks so there could be an argument that the thermal uncertainty is 1/f in nature by first principles. I don't have the knowledge to pursue this.

BTW I also found microphone capsules that had excess 1/f noise due to high sheet rho in the diaphragm coating (another case of distributed R/C). This stuff does not appear anywhere in the literature that I can find, I took about 12 Primo capsules and separated out the ones with excess noise and the noisy ones had a different diaphragm (100% correlation).

I scratched my head for years trying to explain my measurements till I came across Mr. Izpura's paper.

For the record years ago the CEO/CTO of one of the most prestigious hydrophone manufacturers and a universally recognized guru told me I was totally wrong (in a very rude way) and excess gate current noise of FET's does not exist (probably because he didn't discover it).

Last edited:

I did read repeatedly that 1/f and current density / size of the active zones are linked inversely,

can't find the references right now but it convinced me to try a 100 MHz

crystal oscillator with Infineon sot-89 RF transistors running at low current density.

I have much too many projects in parallel, I must seriously flush that pipeline.

And there are some 1/f corner claims for the BF862 that I really do not believe.

Just drown everything in white noise and you can push down the 1/f corner as much

as you like.

Prof. Enrico Rubiola has promoted a different metric, see < Enrico Rubiola home page >

That homepage is a wonderful resource.

Scott, did you get that ETH paper?

I have not yet caught up on the messages above.

Cheers, Gerhard

can't find the references right now but it convinced me to try a 100 MHz

crystal oscillator with Infineon sot-89 RF transistors running at low current density.

I have much too many projects in parallel, I must seriously flush that pipeline.

And there are some 1/f corner claims for the BF862 that I really do not believe.

Just drown everything in white noise and you can push down the 1/f corner as much

as you like.

Prof. Enrico Rubiola has promoted a different metric, see < Enrico Rubiola home page >

That homepage is a wonderful resource.

Scott, did you get that ETH paper?

I have not yet caught up on the messages above.

Cheers, Gerhard

Last edited:

- Home

- Design & Build

- Equipment & Tools

- My version of the G = 1000 low noise measurement amp (for Ikoflexer)