it'll need sort of speaker delay , just because there is nasty voltage peak in startup sim

or a small knife switch on outputs ala Frankenstein?

tnx

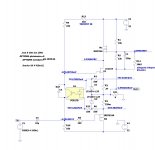

this is proof of a pudding ....... not exactly proof in a pudding

si , it is doable , Iq around 1A6 as predicted per spice

it'll need sort of speaker delay , just because there is nasty voltage peak in startup sim

this is far from optimised** , THD is 0.1% at 1W , though THD spectra is schweeeeeeeeeet

**demanding both more time with LTSpice and then real deal - playing with it in vivo

Hi ZM. Interesting circuit. Pls check FET Vgs values; -5.3V for P-MOS and -3.8V for SIT?; reversed?

tnx

this is proof of a pudding ....... not exactly proof in a pudding......

**demanding both more time with LTSpice and then real deal - playing with it in vivo

Mr. MR , have you SJDP model , too ?

and , just now , I'm having an idea of trying it with cascoded LU ...... it would allow full blast (meaning regular FW range of PSU voltage ) version of amp

will sim tonight ....... and just dream when I'll have time to try it in vivo

another proof that pudding exists

real pudding is on da Bench

startup behavior pretty benign , no need for speaker delay

cascode voltage fine-level trimpot advisable , you can put pot there and call it Zen Amount Pot ........ something as in PapaSit-1

real pudding is on da Bench

startup behavior pretty benign , no need for speaker delay

cascode voltage fine-level trimpot advisable , you can put pot there and call it Zen Amount Pot ........ something as in PapaSit-1

Attachments

Last edited:

- Home

- Amplifiers

- Pass Labs

- Most Greedy Boy, of them all... or (there is no) DEFiSIT of Papa's Koans