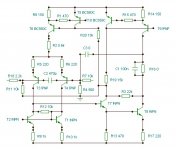

ian_elvar said:Main filtering is done as close the the power rail connections as I could get it, and sits between them and the small signal parts, opposite the power components. Both positive and negative rail decoupling have their own connections back to the star point.

The vertical track on the left of the board only carries some extra rail decoupling, and the grounds for the current sources.

The Zobel also has its own connection back to the star point.

The power decoupling grounds should be joined in the own PCB through a short low inductance path, wiring in series with decoupling (or after it) makes it useless. Multiple returns to a central ground are only useful below 20Khz to avoid humm and buzzz, at RF they only make harm. The positive rail, the negative rail and power (decoupling) ground should be laid out close together. This single power ground should be the one returned to the star ground (and also one main signal ground).

The zobel should be connected to the power (decoupling) ground in the own PCB through a short low inductance PCB track. The zobel resistor should be low inductance (not wirewound), it should be resistive at least up to the unity gain frequency of the CFP, which may be 10Mhz or more once the layout is optimized.

The purpose of all this is to have low RF impedance from +V to -V and a resistive RF load from output to PGND (actually to +V and -V, the output stage does not care about PGND, one zobel from output to V+ and other from output to V- would work equally fine).

Remember that two parallel wires carrying opposite currents are at least 5nH per cm. This is 100nH for 20cm. On the other hand, Z=2*pi*F*L, so Z for 20cm of these wires at 5Mhz is over 3 ohms. Wires are very inductive.

If you can, try enlarging the PCB a bit to the right and placing the power, zobel and decoupling stuff on the right side of the output transistors.

Otherwise, try growing the PCB vertically, spacing more the output transistors and placing that stuff on the middle.

Remember to add some layout inductance to the power paths when doing simulations. You can assume 5 to 10nH per cm.

Otherwise, try growing the PCB vertically, spacing more the output transistors and placing that stuff on the middle.

Remember to add some layout inductance to the power paths when doing simulations. You can assume 5 to 10nH per cm.

ian_elvar said:And I forgot to mention that I'm going to try something that may or may not be slightly unconventional this evening. Simulation suggests that keeping the inductance on the source connection low is the best way to keep gain peaks and phase changes out of the way, so I'm going to try making the power connections straight to the bolts that run through the ali mounting plate to hold the FETs down and make the source connection with the PCB.

I've got a car ignition system and ECU that I'm tweaking on the bench at the moment, but I'll update when I get the amp set up again this evening.

I've simulated your circuit with all the same models as you and it looks pretty well behaved. I've used 150nH inductors in the power lines and zobel to represent the 30cm of wiring you are using (I assume?). Bandwidth is about 4MHz.

With the cosher models the DG caps actually work slightly better the other way around - 47pF on the p-channel M1 and 22pF on the N-channel.

So if it doesn't work, I'll be looking for some other culprit. I assume you haven't got ANY decoupling caps on the pcb. There is nothing but the bench supply, 30cm of wire away, and this is where the star ground is located. This is extremely important.

Given the inductance of the psu wires, I think you are wasting your time with the direct-bolt connection, if I understand it right.

What Eva is recommending regarding localized decoupling may help, but I'm wondering why it should be necessary. But lots of things can cause problems and I cannot see you actual circuit.

The other thing, Ian, is what level of output voltage into what size load causes the oscillation to start? Or is it there all the time? It is useful to know what current level causes the problem. The FETs gm increases with current, you see, so the loop gain of the CFP circuit increases and this decreases its phase margin.

Stopping a circuit oscillating is not a problem. All it takes is reducing the gain and adding damping (resistors). In your circuit you can just make the emitter resistors bigger and bigger until it stops (someone suggested 100 ohms, earlier). But we need to try to identify the cause and how close to the edge the thing is. And also if there are any mitigating factors to do with the psu and ground arrangements.

Stopping a circuit oscillating is not a problem. All it takes is reducing the gain and adding damping (resistors). In your circuit you can just make the emitter resistors bigger and bigger until it stops (someone suggested 100 ohms, earlier). But we need to try to identify the cause and how close to the edge the thing is. And also if there are any mitigating factors to do with the psu and ground arrangements.

I couldn't sleep. This happens to me a lot when I've got an unresolved problems with something I'm working on. At 4am I was suddenly WIDE awake, so I cleared my bench and set the amp up again.

I added the small D-G caps, changed to 1K and 1K5 stoppers, and began testing. So far I've completely failed to upset it.

Sine and square testing give a clean output right accross the frequency and power range.

Swing before to get oscillation was around 5V pk2pk, at about .5A

The only thing I can't do is test at any great swing with an unattenuated connection to the speaker, as I run the risk of incurring the wrath of my girlfriend who is currently still sound asleep, so that will have to wait until later.

I have an attenuator box which allows me to switch high power resistors in with the speaker in different configurations, or run just with a resistive load, so I'm running through that at the moment. This equates to about 22ohm load impedance, which I know isn't much of a test, but the current state is still an improvement on before. Maximum current draw has been 1A off each rail. When I get a chance to assault my ears with unattenuated testing I'll do another update. Might even play some music, but I'm not holding my breath.

I added the small D-G caps, changed to 1K and 1K5 stoppers, and began testing. So far I've completely failed to upset it.

Sine and square testing give a clean output right accross the frequency and power range.

Swing before to get oscillation was around 5V pk2pk, at about .5A

The only thing I can't do is test at any great swing with an unattenuated connection to the speaker, as I run the risk of incurring the wrath of my girlfriend who is currently still sound asleep, so that will have to wait until later.

I have an attenuator box which allows me to switch high power resistors in with the speaker in different configurations, or run just with a resistive load, so I'm running through that at the moment. This equates to about 22ohm load impedance, which I know isn't much of a test, but the current state is still an improvement on before. Maximum current draw has been 1A off each rail. When I get a chance to assault my ears with unattenuated testing I'll do another update. Might even play some music, but I'm not holding my breath.

Lumba Ogir said:Variation on a Theme (in the head)...

That's an interesting idea. Any simulations planned?

Sine and square testing reveals no problems into an 8ohm single drive speaker, or two of said speakers in parallel. Clipping is graceful, with perfect recovery. I can't find any oscillation no matter how hard I look. Time for some music!

Lumba Ogir said:ian_elvar

simulation`s done - in the head.

Lol. I've started putting it into LTSpice out of interest, but not finished yet. What's the background?

Eva said:Have you tried how far can you go reducing gate resistors? Output stage distortion is going to depend mostly on their value.

That was going to be my next move actually. I want to test it thoroughly before I make any more changes, then try tweaking it back towards where I know it's unstable to find out what margin I've got to play with. It'll also give me something to compare to when I re-do the PCB layout.

First impressions....

Difficult to tell. I'm using a cheap pair of Hitachi speakers, mounted on my PC desk which has a load of stuff that rattles. Listening to one channel of material that you know well is also a bit weird. Anyway, I started off with BT's Road to Lostwithiel from ESCM, because he's my favorite recording artist, and I know every track on that album intimately. I'm the last person to get anthripomorphic about a piece of solid state circuitry, but there's something about Road to Lostwithiel that manages to bring audio systems to their knees.

What I can discern is that it's extremely punchy and ruthless about bringing out detail, even with these truly abysmal speakers. Depth of sound isn't ever going to be their strong point, so it's unfair to be too judgemental, but it certainly beats the hell out of the little Hitachi amp that normally drives them. When it gains my confidence a bit more I'll plug it into some KEF Cresta's that I use for latter phases of testing and give it a half decent listen.

Difficult to tell. I'm using a cheap pair of Hitachi speakers, mounted on my PC desk which has a load of stuff that rattles. Listening to one channel of material that you know well is also a bit weird. Anyway, I started off with BT's Road to Lostwithiel from ESCM, because he's my favorite recording artist, and I know every track on that album intimately. I'm the last person to get anthripomorphic about a piece of solid state circuitry, but there's something about Road to Lostwithiel that manages to bring audio systems to their knees.

What I can discern is that it's extremely punchy and ruthless about bringing out detail, even with these truly abysmal speakers. Depth of sound isn't ever going to be their strong point, so it's unfair to be too judgemental, but it certainly beats the hell out of the little Hitachi amp that normally drives them. When it gains my confidence a bit more I'll plug it into some KEF Cresta's that I use for latter phases of testing and give it a half decent listen.

ian_elvar,

in my humble opinion: the oscillation undoubtedly occurs in the CFP, its frequency being about ten times higher than that caused by GNF. It tells me that the drivers are not fast enough, (around 100MHz@5mA, which is probably the level of the FETs), 300-500MHz would be desirable.

in my humble opinion: the oscillation undoubtedly occurs in the CFP, its frequency being about ten times higher than that caused by GNF. It tells me that the drivers are not fast enough, (around 100MHz@5mA, which is probably the level of the FETs), 300-500MHz would be desirable.

After the earlier comment, I have been looking for a suitable driver.ian_elvar said:Ok, I can see where you're coming from. Dalbani have 2SC3600/2SA1406 in stock, so I've ordered up a couple of pairs.

1407/3601 seems suitable but it's 150mA capability restricts it to driving probably only one output FET. I don't know how well the 1406 @ 100mA will cope with the dual die output FET.

The concepts here might help, not CFP and examples are BJTs but the analysis might offer some insight:

http://www.analogzone.com/col_1017.pdf

http://www.analogzone.com/col_1121.pdf

Pete B.

http://www.analogzone.com/col_1017.pdf

http://www.analogzone.com/col_1121.pdf

Pete B.

Nice  My brain is a bit frazzled from not getting much sleep last night though, so I'll have a better look tomorrow and see what I can pull out that'll be useful here.

My brain is a bit frazzled from not getting much sleep last night though, so I'll have a better look tomorrow and see what I can pull out that'll be useful here.

I think I found the solution to the driver problem. Sanyo 2sc3954/2sa1539. 400MHz, 300mA, 120V. I can't find any better at the moment, so I amended my order.

I think I found the solution to the driver problem. Sanyo 2sc3954/2sa1539. 400MHz, 300mA, 120V. I can't find any better at the moment, so I amended my order.

Glad you seem to have it behaving, and especially glad you are listening to it. That's the best bit of the design process, in my opinion.

There are some more things to look at after you've had a listen on proper speakers and noted its pros and cons.

Pete B.'s articles are quite good.

As a general point, speed is not always your friend, don't just go for speed without knowing what you are trading off for it. There is always a trade off. You need to choose the right speed for the job.

Brian

BTW: those Sanyo drivers only have 5MHz ft. I think the drivers you have are ok, provided the oscillation has been quenched.

There are some more things to look at after you've had a listen on proper speakers and noted its pros and cons.

Pete B.'s articles are quite good.

As a general point, speed is not always your friend, don't just go for speed without knowing what you are trading off for it. There is always a trade off. You need to choose the right speed for the job.

Brian

BTW: those Sanyo drivers only have 5MHz ft. I think the drivers you have are ok, provided the oscillation has been quenched.

- Status

- This old topic is closed. If you want to reopen this topic, contact a moderator using the "Report Post" button.

- Home

- Amplifiers

- Solid State

- CFP oscillation woes