Read the manuał : "6VAC or 7-9V DC" ...Hi guys, Ian,

Do you think a 10V AC transformer would be ok for the LinearPi?

Hi Eduard.I have solved my problem.The problem was in the cables 6 inches long(www.audiophonics.fr/en/cables-audio-cables-numeriques/ian-canada-ufl-coaxial-cable-double-ended-silver-plated-6-p-14449.html).Components from IAN do not play with these cables.You only need to use 2.5-inch cables(www.audiophonics.fr/en/cables-audio-cables-numeriques/ian-canada-ufl-coaxial-cable-double-ended-silver-plated-25-p-14448.html).Hello,

Me too i am having problem getting sound from Fifopi/ raspberry/ stationpi/ reclockpi/stationpi / Andrea's clock circuits connected to DDDAC motherboard.

All leds that need to be lit are lit.

The only thing that i can do is reconnecting the 3 u.FL cables to the DDDAC mainboard. I think about removing the original connector from the DDDAC motherboard so i can insert the u.FL cables into the board and get a better soldering contact.

I also thought about just using 6 solid cores wires from 40 pin GPIO connector and guide them '' into '' the motherboard but they say u.FL is better. But to me only if you can make a proper connecting.

I also think that the cable '' proposed '' for connecting the external clock to the Sinepi is much to rigid.

Greetings, Eduard

P.s i guess there no way to check with a simple multimeter if the output from the reclockpi is liker it should be when it enters the DDDAC board??

Thanks for the feedback retty. I too have struggled with 6" cables.Hi Eduard.I have solved my problem.The problem was in the cables 6 inches long(www.audiophonics.fr/en/cables-audio-cables-numeriques/ian-canada-ufl-coaxial-cable-double-ended-silver-plated-6-p-14449.html).Components from IAN do not play with these cables.You only need to use 2.5-inch cables(www.audiophonics.fr/en/cables-audio-cables-numeriques/ian-canada-ufl-coaxial-cable-double-ended-silver-plated-25-p-14448.html).

Is anybody using SinePi successfully with a FifoPiQ2 and two external Andrea clocks? I'm having problems.

The FifoPiQ2 is working perfectly with two Crystek XOs, but when replacing these with the SinePi and two external Andrea clocks (45/49 MHz) the SinePi relay keeps switching between the two clocks no matter what the FifoPi input sample rate is. The clock outputs seems fine.

The FifoPiQ2 is working perfectly with two Crystek XOs, but when replacing these with the SinePi and two external Andrea clocks (45/49 MHz) the SinePi relay keeps switching between the two clocks no matter what the FifoPi input sample rate is. The clock outputs seems fine.

Hey - You need Q3 to manage two XO's without OE Pin. Worth the upgrade with the reclockpi though. Pretty significant for clarity, I was surprised.Is anybody using SinePi successfully with a FifoPiQ2 and two external Andrea clocks? I'm having problems.

The FifoPiQ2 is working perfectly with two Crystek XOs, but when replacing these with the SinePi and two external Andrea clocks (45/49 MHz) the SinePi relay keeps switching between the two clocks no matter what the FifoPi input sample rate is. The clock outputs seems fine.

Edit: I use Andrea Clocks..

Hmm... that is not what is written in the manual...

In the introductions it says: "works flawlessly with FifoPi Q1, Q2 and Q3".

The only place Q3 specific functionality is mentioned is for the "half sine mode" with one local square wave crystal. Here it reads: "the local XO doesn’t need an OE control pin if you use FifoPi Q3 or higher".

If what you say is correct SinePi does not work flawlessly with FifoPi Q2. It is in reality only compatible with FifoPi Q3.

Anyway, I hope you are wrong and that Ian will take a minute to clarify things.

In the introductions it says: "works flawlessly with FifoPi Q1, Q2 and Q3".

The only place Q3 specific functionality is mentioned is for the "half sine mode" with one local square wave crystal. Here it reads: "the local XO doesn’t need an OE control pin if you use FifoPi Q3 or higher".

If what you say is correct SinePi does not work flawlessly with FifoPi Q2. It is in reality only compatible with FifoPi Q3.

Anyway, I hope you are wrong and that Ian will take a minute to clarify things.

Hmm... that is not what is written in the manual...

In the introductions it says: "works flawlessly with FifoPi Q1, Q2 and Q3".

The only place Q3 specific functionality is mentioned is for the "half sine mode" with one local square wave crystal. Here it reads: "the local XO doesn’t need an OE control pin if you use FifoPi Q3 or higher".

If what you say is correct SinePi does not work flawlessly with FifoPi Q2. It is in reality only compatible with FifoPi Q3.

Anyway, I hope you are wrong and that Ian will take a minute to clarify things.

Fair enough........

This Q3 version of FiFoPi, a direct improvement of FiFoPi Q2, benefits from several enhancements that increase the performance of the module in order to offer you a sound reproduction of ever higher quality.

- Supports oscillators (XO) with and without OE pin.

- Uses 3.3V for a clean DC power supply. All LDOs have been removed to allow direct operation with a better 3.3V power solution via LifePO4 or ultra-capacitor.

- Optional U.FL input for connection to an external oscillator via coaxial cable.

- Supports XO (oscillator) Single Mode.

- XO oscillator support in SMT format for easy replacement.

- Isolated MUTE and DSD EN outputs for better operation with pure DSD DACs or external PCM/DSD DACs (via TransportPi or HdmiPi).

- New high-speed 300MHz flip-flops to reduce the additional jitter of the final I2S/DSD reclocking.

- Optimized decoupling networks to improve power supply performance.

Hello,

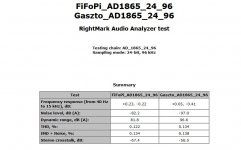

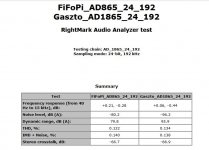

I 'm using FiFoPi Q2- I2StoPCM - AD1865 DAC, but is it a step back in sound quality comapared to my previous setup (RPi USB port - JLSounds - AD1865)

With USB - JLSounds the sound stage was more defined, there was a big air around the instruments. Now it is dull.

I did some measurement (before and after) with my ESI Juli@ sound card, and the Noise and Dynamic was better.

I connected FiFoPi and I2Sto PCM card with U.FL cables, as short as possible. The power supply is for the clean side of the FIFoPi, and I2StoPCM card are two parallel LT3045 (I used same power supply earlier for the JLSounds card)

Anybody have an idea what is wrong? I think FiFoPi should be as good as the JLSounds or better.

I 'm using FiFoPi Q2- I2StoPCM - AD1865 DAC, but is it a step back in sound quality comapared to my previous setup (RPi USB port - JLSounds - AD1865)

With USB - JLSounds the sound stage was more defined, there was a big air around the instruments. Now it is dull.

I did some measurement (before and after) with my ESI Juli@ sound card, and the Noise and Dynamic was better.

I connected FiFoPi and I2Sto PCM card with U.FL cables, as short as possible. The power supply is for the clean side of the FIFoPi, and I2StoPCM card are two parallel LT3045 (I used same power supply earlier for the JLSounds card)

Anybody have an idea what is wrong? I think FiFoPi should be as good as the JLSounds or better.

Attachments

This is from the description of Q3 that came out a long time before SinePi and the information refers to square wave clocks plugged directly into Q3.Fair enough........

This Q3 version of FiFoPi, a direct improvement of FiFoPi Q2, benefits from several enhancements that increase the performance of the module in order to offer you a sound reproduction of ever higher quality.

- Supports oscillators (XO) with and without OE pin.

- Uses 3.3V for a clean DC power supply. All LDOs have been removed to allow direct operation with a better 3.3V power solution via LifePO4 or ultra-capacitor.

- Optional U.FL input for connection to an external oscillator via coaxial cable.

- Supports XO (oscillator) Single Mode.

- XO oscillator support in SMT format for easy replacement.

- Isolated MUTE and DSD EN outputs for better operation with pure DSD DACs or external PCM/DSD DACs (via TransportPi or HdmiPi).

- New high-speed 300MHz flip-flops to reduce the additional jitter of the final I2S/DSD reclocking.

- Optimized decoupling networks to improve power supply performance.

External clocks are connected via coax (gnd/signal) to SinePi and there is no connection for an "enable pin".

I may have a defective SinePi and for the moment I'm just trying to find out if it should work.

The continuous switching of the SinePi relay occur only when FifoPi Q2 is receiving a signal. It happens independently of the number of clocks connected (2, 1 or none), making me think that the problem may be related to the square wave conversion.

If you say so - have a good eve.This is from the description of Q3 that came out a long time before SinePi and the information refers to square wave clocks plugged directly into Q3.

External clocks are connected via coax (gnd/signal) to SinePi and there is no connection for an "enable pin".

I may have a defective SinePi and for the moment I'm just trying to find out if it should work.

The continuous switching of the SinePi relay occur only when FifoPi Q2 is receiving a signal. It happens independently of the number of clocks connected (2, 1 or none), making me think that the problem may be related to the square wave conversion.

The JLsounds is great, but I prefer using I2s over HDMI - less conversions. Try the reclocker, that really made a significant difference for me.Hello,

I 'm using FiFoPi Q2- I2StoPCM - AD1865 DAC, but is it a step back in sound quality comapared to my previous setup (RPi USB port - JLSounds - AD1865)

With USB - JLSounds the sound stage was more defined, there was a big air around the instruments. Now it is dull.

I did some measurement (before and after) with my ESI Juli@ sound card, and the Noise and Dynamic was better.

I connected FiFoPi and I2Sto PCM card with U.FL cables, as short as possible. The power supply is for the clean side of the FIFoPi, and I2StoPCM card are two parallel LT3045 (I used same power supply earlier for the JLSounds card)

Anybody have an idea what is wrong? I think FiFoPi should be as good as the JLSounds or better.

I2StoPCM is also an old design.

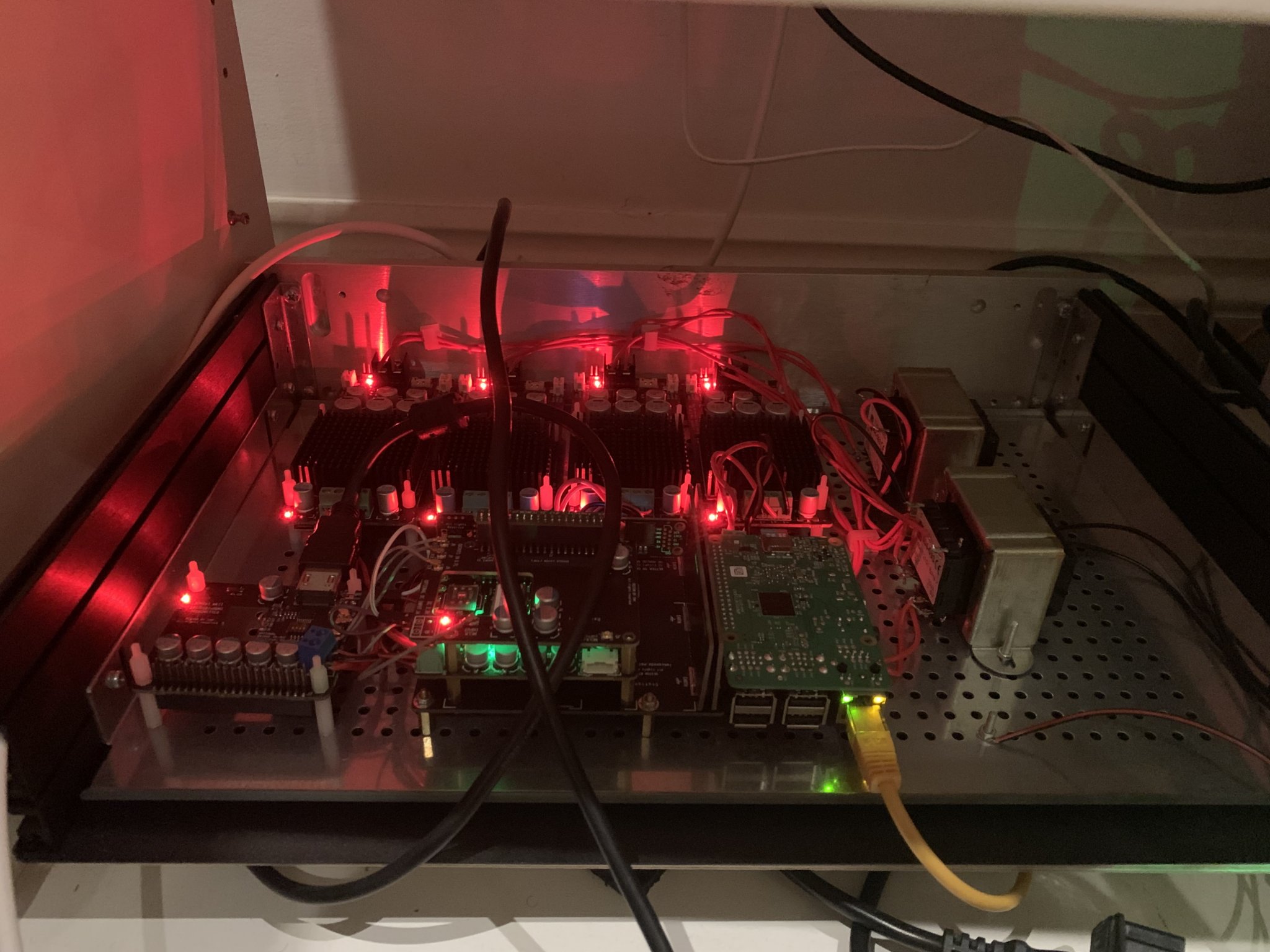

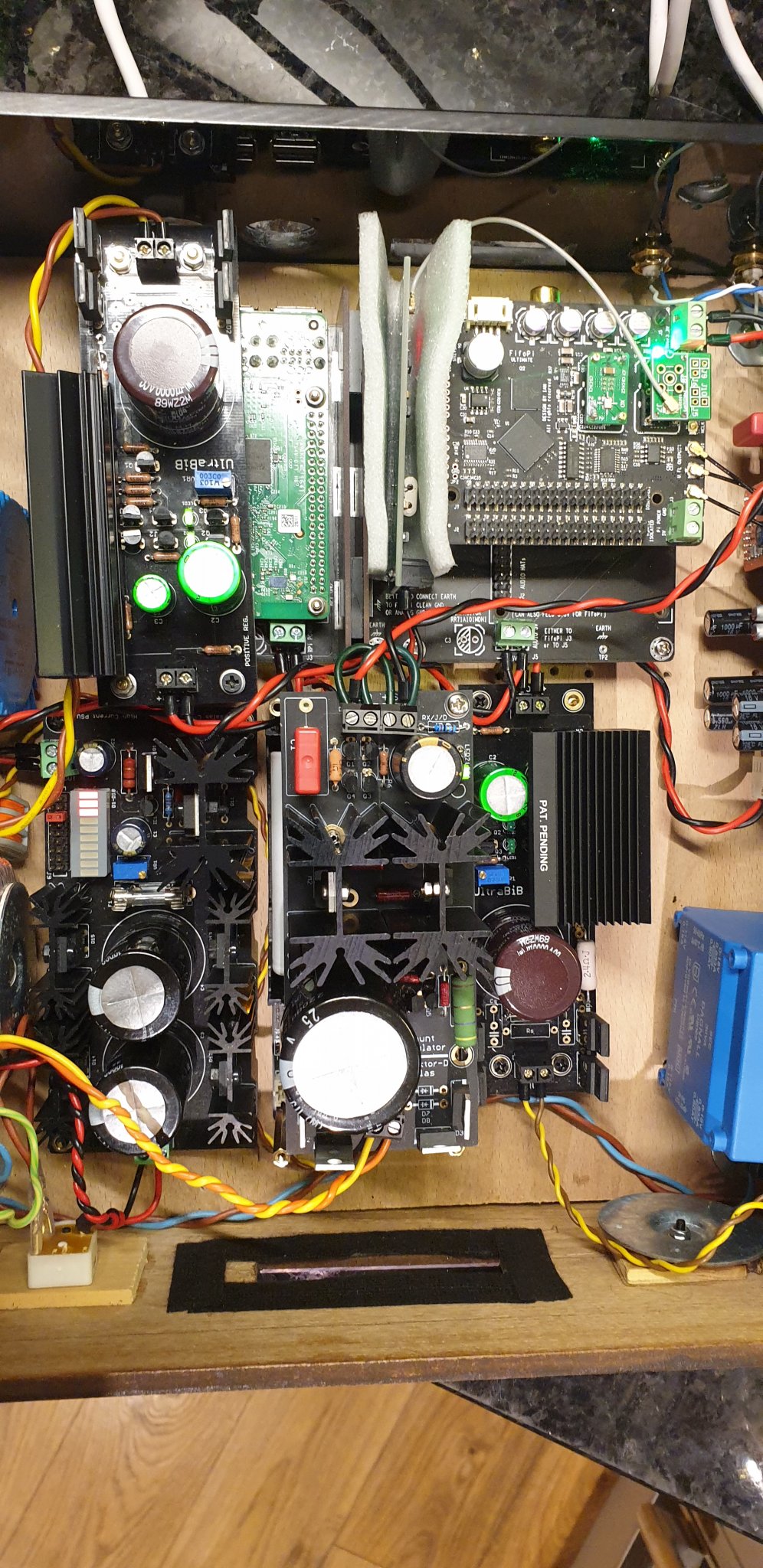

Whilst I am here and Ian is on a R+D sabbatical. I have been fiddling around with my dac/streamer for quite a bit now - I think I'm on year 2 now (maybe year 3). These are old photos, I'm super happy about the clarity/tone and since broken it into pieces for a proper case (waiting on stationpi pro). It has sent some expensive off the shelf stuff back to the shops or friends houses!

I am getting ready to take what I've learnt (had a couple of Dac projects on the go for a while now) and build an end game streamer/dac. Key differences for my personal end game is R2R for conversion (so much easier to get good sound out of a R2R chip - ESS is hard hard work but worth it imo for the benefits of SDM but also the benefits of R2R (If that makes sense)... - but waiting for Andrea's discrete option), ATX for streamer.

DAC: Please ignore build quality like that 5v dirty side , I on average rebuild once or twice a week to test something new - not much has changed here though apart from ultra caps on the dirty side of the FIFO. There is also an external 19v LPS for the battery board you cannot see in the photo.

, I on average rebuild once or twice a week to test something new - not much has changed here though apart from ultra caps on the dirty side of the FIFO. There is also an external 19v LPS for the battery board you cannot see in the photo.

The streamer has changed substantially - there are 7 rails now, plan to add ultra caps on rebuild but still need to be purchased. There are two toroidy transformers now, much larger VA. 1x for pi side/FIFO dirty Side and 1x Clean side. I also have two Andrea clocks for streamer, but want to see if I can hear the benefit of double Andrea clocks..

I have to say congrats Ian, the sound I have achieved from this gear has really really surprised me and anyone that has visited.

It's certainly dealt with my OCD nature for a while I think I have tried most power supply/clock options out there on this project.

I think I have tried most power supply/clock options out there on this project.

I am getting ready to take what I've learnt (had a couple of Dac projects on the go for a while now) and build an end game streamer/dac. Key differences for my personal end game is R2R for conversion (so much easier to get good sound out of a R2R chip - ESS is hard hard work but worth it imo for the benefits of SDM but also the benefits of R2R (If that makes sense)... - but waiting for Andrea's discrete option), ATX for streamer.

DAC: Please ignore build quality like that 5v dirty side

The streamer has changed substantially - there are 7 rails now, plan to add ultra caps on rebuild but still need to be purchased. There are two toroidy transformers now, much larger VA. 1x for pi side/FIFO dirty Side and 1x Clean side. I also have two Andrea clocks for streamer, but want to see if I can hear the benefit of double Andrea clocks..

I have to say congrats Ian, the sound I have achieved from this gear has really really surprised me and anyone that has visited.

It's certainly dealt with my OCD nature for a while

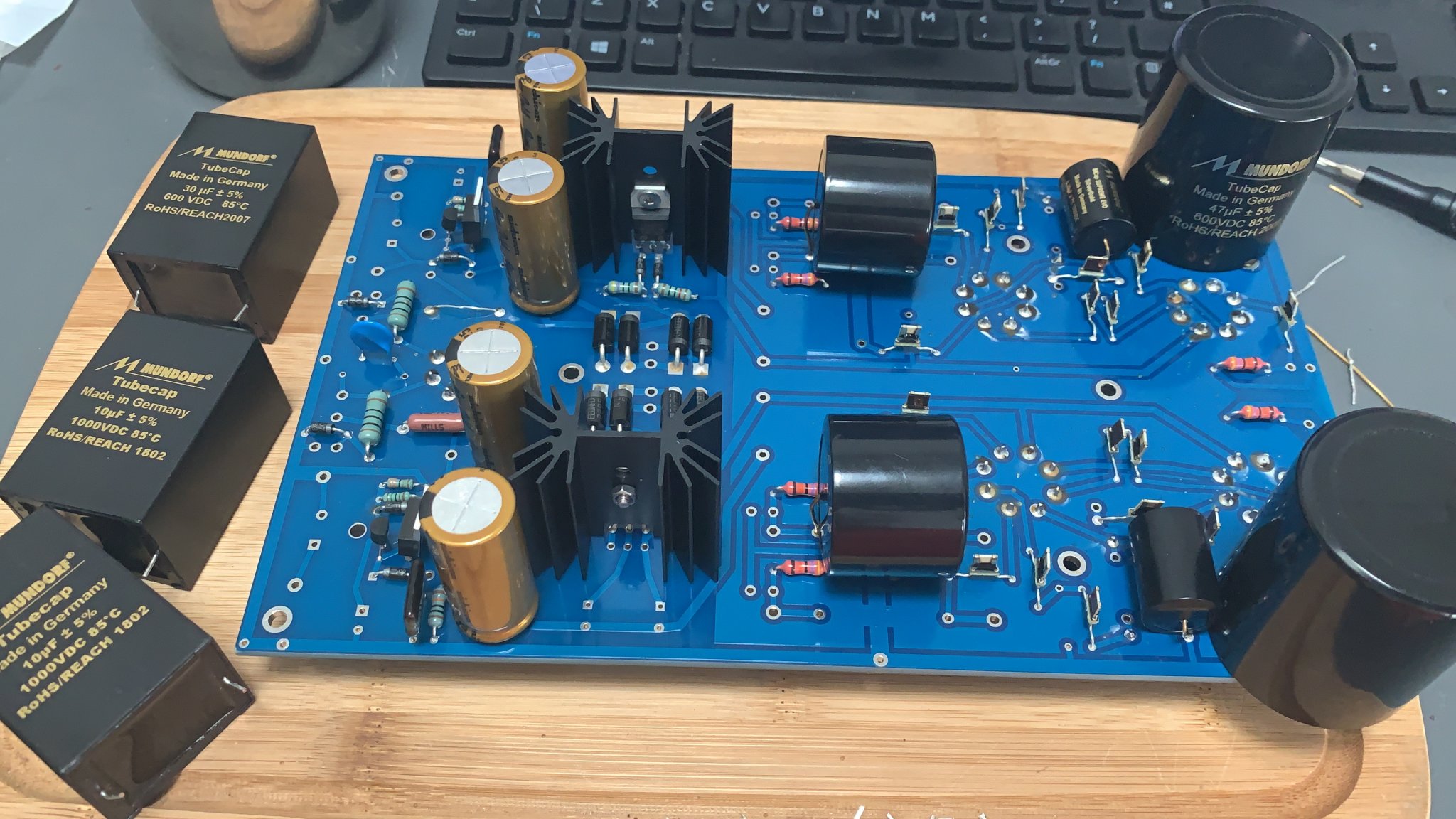

Forgot the output stage! That's taken the longest to get right. I have gone for a hybrid output stage. I use transformers (Ivan's Copper primary and silver secondary - amazing and worth every extra) for IV conversion with Z-foils. I have it set-up so the ESS chip only sees 2.5ohm load (Game changer) and it pops out 0.2v output to the real gain stage - that brings it up to around 1.8v something (Testing tubes)

:

:

I had this and mentioned to Ian. I think after a few resit's - they do get loose. I've redone a few Fifo Q2's and Q3's clock connectors to get that tight fit again. Sinepi is a nice design with the ReclockPI because it applies pressure from the top and prevent's the sinepi moving about. A nice functional improvement, not sure if it was intended, but there wasn't a lot of vertical space for the sinepi - so must have taken Ian a little while to get it right.Dont know if its the integrity of the pins seating in the socket...

I'm a big fan of the Reclockpi

Serious setup Sebby. Nice work.

Here is mine of late.

StationPi, 5v Pi power from Salas L adaptor. 3v3 clean to fifo from Salas Reflektor D. Ian Receiver in there too. 3v3 dirty by Salas Ubib.

Another Ubib powering Abraxalito Phideca dac. Ian 6v6 Lipomini powering Andrea Mori clock TWTMC PPG. Currently trying this dac over the Ian dual ESS . I'll try the Miro AD1862 in here too sometime

Here is mine of late.

StationPi, 5v Pi power from Salas L adaptor. 3v3 clean to fifo from Salas Reflektor D. Ian Receiver in there too. 3v3 dirty by Salas Ubib.

Another Ubib powering Abraxalito Phideca dac. Ian 6v6 Lipomini powering Andrea Mori clock TWTMC PPG. Currently trying this dac over the Ian dual ESS . I'll try the Miro AD1862 in here too sometime

- Home

- Source & Line

- Digital Line Level

- Asynchronous I2S FIFO project, an ultimate weapon to fight the jitter