BTW to increase the confidence of your measurements at this level you could verify the distortion at all three outputs of the state variable ring as well as at the multiplier output. For my oscillator design I get -135 dB for the 2nd and 3rd harmonic (no higher harmonics measurable) at all three oscillator outputs which gives some confidence that this is actually an analyzer contribution.

Hi Samuel, after a few changes I just did a couple of tests with both analysers - using the Bainter/Twin-T double notch I get a fixed ~-140 dB 3rd harmonic residual, while the 2nd harmonic level varies between ~-127 dB (HP out) and ~-140 dB (LP out); the 2nd harmonic from the BP out is ~3 dB higher (~-137 dB), which sounds a little bit strange. The SVF auto notch is considerably noisier: the 3rd harmonic is consistently beyond noise floor, while 2nd harmonic level lowers almost exactly by 6dB/oct switching from HP (~-126dB) to BP (~-132dB); the 2nd harmonic from the LP output is buried in the noise. The generator's output level is +10dBV, and its output is lowered to 0dBV before entering the analysers.

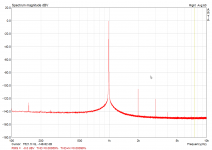

Just to answer your question about noise performance, here is a sample spectrum acquired with the EMU:

The amplitude stability and the settling time are both satisfactory, the main issue remaining the startup time, which is unbearably long; once started, a stable output level is reached in about 4-5 seconds. I still have to address this.

My goal is to achieve a very low THD for, say, 4-5 spot frequencies; I've also tried a variable-frequency voltage-controlled setup by inserting a couple of AD633 in the SVF ring, and it worked very well, by its THD performances are limited by the multipliers' THD, as you pointed out.For a fixed frequency oscillator it is in fact much simpler to just add e.g. a Chebyshev low pass filter at the oscillator output rather than spending too much efforts in reducing level detector ripple and multiplier distortion.

L.

Sorry for the repeated posts - I just did something wrong with the editor...

Last edited:

The 2nd harmonic from the BP out is ~3 dB higher (~-137 dB), which sounds a little bit strange.

So it seems like there is some cancellation going on. What capacitors/resistors have you used in the notch filter? What's its operating level?

Just to answer your question about noise performance, here is a sample spectrum acquired with the EMU:

If you want to determine the actual sideband performance of the oscillator you must make sure that the FFT window has very good sidelobe performance; it looks as if on your plot window sidelobes would actually mask oscillator sidebands. What window did you use?

The amplitude stability and the settling time are both satisfactory, the main issue remaining the startup time, which is unbearably long.

Its not entirely clear to me what you mean by "settling time" and "startup time"; as we usually power up our oscillators just few times a day 4-5 s seems fast enough for me. What's important is settling after a frequency change.

My goal is to achieve a very low THD for, say, 4-5 spot frequencies.

So what's the range of these?

Samuel

So it seems like there is some cancellation going on. What capacitors/resistors have you used in the notch filter? What's its operating level?

Selected polypropylene capacitors/1% metal film resistors. Both notches were designed trying to keep as low as possible CM distortion, so SVF has an 'all inverting' topology, and Bainter was chosen because only one out of three opamp is in non-inverting configuration. The operating level is 0 dBV for both, but this is a real issue only for the auto-tuning one.

The spectrum was taken with Hanning window, which is far from optimum from the point of view of sidelobe suppression - Blackman-Harris or Kaiser would behave better, but I don't remember such a great difference in spectral line shape using these ones; nevertheless I'll try them.If you want to determine the actual sideband performance of the oscillator you must make sure that the FFT window has very good sidelobe performance; it looks as if on your plot window sidelobes would actually mask oscillator sidebands. What window did you use?

It takes about 30 seconds for oscillation to build up; once oscillation has started amplitude stabilize in 5 seconds or so. It seems a genuine microsoft product: it's a feature, not a bug...Its not entirely clear to me what you mean by "settling time" and "startup time"; as we usually power up our oscillators just few times a day 4-5 s seems fast enough for me. What's important is settling after a frequency change.

Something like 200 - 400 - 1k - 4k - 6/8k.So what's the range of these?

Ciao,

L.

Selected polypropylene capacitors/1% metal film resistors. Both notches were designed trying to keep as low as possible CM distortion, so SVF has an 'all inverting' topology, and Bainter was chosen because only one out of three opamp is in non-inverting configuration. The operating level is 0 dBV for both.

I'd say at this AC level and choice of passives their voltage coefficient should be negligible, but you never know if you got one with bad end contacts. Unlikely though. What's perhaps more likely are distorted ground currents or induction from the supply rails (they carry class B currents from the opamps). But at these levels its hard to tell.

I don't remember such a great difference in spectral line shape using these ones.

If its really the oscillator performance this would indicate very high amplitude noise (if this matters is another question). What's the FFT resolution?

It takes about 30 seconds for oscillation to build up.

And that's not because you have a low pass filter on the voltage reference (or somewhere in the power supply)?

Once oscillation has started amplitude stabilizes in 5 seconds or so.

Does the level bounce (i.e. go above and below nominal level in a ringing fashion)? What does the multiplier control voltage look like?

Samuel

If its really the oscillator performance this would indicate very high amplitude noise (if this matters is another question). What's the FFT resolution?

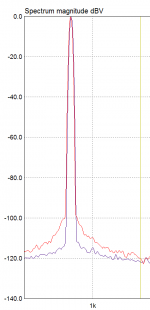

Ok - just to understand what level of amplitude/phase noise is going to be considered acceptable: the graph below is a comparison between a low cost synthetized function generator (blue line) and another SVF generator of my own design (red line):

FFT length is 131072 points with Kaiser window (the highest resolution window I can apply in rt using ARTA). What about the generator performance in your opinion?

Ciao,

L.

It would be easier to judge the plots with a linear frequency scale (and a range of about 500-1500 Hz), but I'd say these two oscillators have low noise.

Looking at the plot of your new design again I think the noise which is visible is not actually from the AGC noise (i.e. true sidebands) but rather just the noise floor from the multiplier, resistors and opamps. 0 dBV is a rather low operating level. But if you just want to do FFT analysis this is less of a problem--for THD+N measurements you'd probably need to increase the operating level.

What is the decoupling factor (i.e. the gain from its output to the low pass output of the SVF) of the multiplier?

Samuel

Looking at the plot of your new design again I think the noise which is visible is not actually from the AGC noise (i.e. true sidebands) but rather just the noise floor from the multiplier, resistors and opamps. 0 dBV is a rather low operating level. But if you just want to do FFT analysis this is less of a problem--for THD+N measurements you'd probably need to increase the operating level.

What is the decoupling factor (i.e. the gain from its output to the low pass output of the SVF) of the multiplier?

Samuel

It would be easier to judge the plots with a linear frequency scale (and a range of about 500-1500 Hz), but I'd say these two oscillators have low noise.

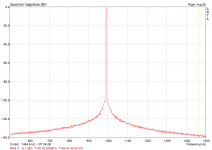

Something like this?

This is the 'all-multiplier' design @ +10dBV out with a better decoupling of the Q-controlling AD633; now it works at a slightly higher operating level than before, and its output is low-pass filtered too - it seems the filtering is really effective in lowering phase noise, but probably you are right: analog multiplier are a little bit too noisy for this kind of application. I mean continuous coverage, as you pointed out - my earlier design, employing a single multiplier in the rectifying stage and an home-made analog optocoupler as Q controlling element, was by far more simpler and effective, altough its THD was certainly higher. Anyway, the ALC loop was improved too: upon startup it takes less then 5 seconds to get the output signal amplitude to within a fraction of dB of its final value; amplitude stability seems very good.

I've not yet managed to measure the distortion products, but they seem to be in the -130 dBc range or less @ +10dBV out - I'll let you know.

About 50dB, which is almost exactly the expected value, actuallyWhat is the decoupling factor (i.e. the gain from its output to the low pass output of the SVF) of the multiplier?

Ciao,

L.

How linear are LDRs that are illuminated with an LED?

For use instead of the FET

I'd say pretty poor, just like FETs and OTAs (and analog multipliers and VCAs, too), but a properly setup SVF topology employing an LDR as level controlling element can attain THD level in the -110/-120 dBc range.

L.

Something like this?

Yes. To make the plot independent of FFT resolution and window we'd actually need to plot in dBc/Hz (or dBc/sqrt(Hz)), but most standard FFT packages don't support this.

For comparison here the performance of my oscillator: sideband_noise.pdf

This was done using a special Equiripple window and a 32k FFT. Performance is actually dominated by mains interference in the level detector (hence 50 Hz sidebands). Once proper screening/casing is applied noise should drop considerably.

How linear are LDRs that are illuminated with an LED?

I've yet do do a good analysis but preliminary measurements indicated that a decent LDR might be slightly better than a JFET with respect to distortion. However it introduces a significant time constant (in the ms region) and the control law is nothing like the linear law we want.

Samuel

2N4091 replacement

Hi Bob,

The Vishay (formerly Siliconix) VCR2N is a suitable direct replacement for the 2N4091. The specs are right on.

The device is specifically intended for this type of application and is supposed to be more linear. While I have not done a direct comparison between the two, I have retrofitted these in several of your oscillators with excellent results.

Better yet, they are available surplus for $1.80 from Electronic Goldmine. VCR2N JFET Voltage-Controlled Resistor (Siliconix)-The Electronic Goldmine

Hope this helps.

Regards,

Keith

Hi Alex,

This is good information. It does sound like the AGC FET may be to blame. It is odd, however, that adjusting the oscillator agc to obtain a higher operating signal level in the oscillator does not increase distortion, including any that would be introduced by the agc FET. I know the 2N4091 is no longer available, and that is problematic. Its high Vgs off is important to minimize its distortion contribution, as the operating signal is then small compared to Vgs. I'm surprized that there are not any good substitutes out there.

Of course, we cannot fully rule out that there is some other source of distortion, such as bad op amps or op amps that are oscillating. What op amps are you using? Maybe try another, like the LM4562, that is internally compensated for unity gain.

It is entirely possible to replace the JFET agc with a good low-noise analog multiplier with some good engineering.

Best,

Bob

Hi Bob,

The Vishay (formerly Siliconix) VCR2N is a suitable direct replacement for the 2N4091. The specs are right on.

The device is specifically intended for this type of application and is supposed to be more linear. While I have not done a direct comparison between the two, I have retrofitted these in several of your oscillators with excellent results.

Better yet, they are available surplus for $1.80 from Electronic Goldmine. VCR2N JFET Voltage-Controlled Resistor (Siliconix)-The Electronic Goldmine

Hope this helps.

Regards,

Keith

Attachments

The Vishay (formerly Siliconix) VCR2N is a suitable direct replacement for the 2N4091. The specs are right on.

No, Ron is about twice as high as for the 2N4091 (or PN4091 and J111). Probably low enough to not give a drastic increase in distortion, but as the part is more difficult to source than the other two replacements I'd avoid it.

The device is specifically intended for this type of application and is supposed to be more linear.

I would not believe that too much.

Samuel

No, Ron is about twice as high as for the 2N4091 (or PN4091 and J111). Probably low enough to not give a drastic increase in distortion, but as the part is more difficult to source than the other two replacements I'd avoid it.

I would not believe that too much.

Samuel

Greetings Herr Groner,

Possibly, I could have been a bit more specific. Of the ten devices I purchased, most fell within the range of 35-40 ohms Ron Max, thus making (IMHO) the VCR2N a reasonable replacement for the 2N4391 in this application.

As to difficulty in sourcing, I was not implying worldwide availability, simply ready availability from the source stated. However, if availability were to be an issue, and one were to ask nicely, perhaps a fellow DIYer might find himself inclined to assist with the sourcing.

Also, I was merely pointing out that the VCR2N is specified for use as a voltage controlled resistor in AGC or VCO (linear) applications, whereas, the 2N4391 is specified solely for switching. In any event, the device does indeed work well in this particular case, as, I believe, my results demonstrate.

It would seem that if low Ron is the metric of choice, the 2N5432 (Ron 5 ohms) could potentially be more suitable.

On a different, but related topic, it is relatively easy to improve linearity of FETs in VCR applications via feedback (Siliconix Application Note AN105). I have not tried this, it looks like it might have merit for applications such as this.

MfG,

Keith

Attachments

Of the ten devices I purchased, most fell within the range of 35-40 ohms Ron Max, thus making (IMHO) the VCR2N a reasonable replacement for the 2N4391 in this application.

Sure--however the typical figure for the 2N4091 (I presume you wanted to refer to that part no.) will also be lower than the max. value given in the datasheet so this only a partially valid argument. But as I said I believe that Ron of the VCR2N is sufficiently low for that application or we could just parallel a pair so we don't need to argue about that any further.

Also, I was merely pointing out that the VCR2N is specified for use as a voltage controlled resistor in AGC or VCO (linear) applications, whereas, the 2N4391 is specified solely for switching.

Unfortunately that does neither mean that the VCR2N offers particularly better performance in this specific application nor that the 2N4091 would not be suitable for linear applications. There is no magic thing manufacturers can do about these distortion mechanisms. We want high Vp and sufficiently low Ron, that's about all. Don't fall in the trap of believing too much in what the datasheet says.

In any event, the device does indeed work well in this particular case, as, I believe, my results demonstrate.

Maybe you could elaborate a bit more how you measured the distortion performance. It looks to me as if you were feeding the oscillator output to some AD converter for a FFT analysis. At these distortion levels you show I very much doubt that such a measurement result has any relevance as the distortion contribution of the AD converter must be in the same order of magnitude as the oscillator distortion. "Improvements" you're observing are just as likely actually higher oscillator distortion which results in better cancellation with the AD converter contribution. If you want to measure to -120 dBc you'll need an analyzer which is guaranteed to have at most -130 dBc distortion contribution; you're showing a graph with the 2nd harmonic near -130 dBc so you'd need an analyzer with -140 dBc performance--that's not easy to do.

For that specific case of comparing JFETs in the multiplier I suggest that you just measure the (absolute!) 2nd harmonic at the multiplier output. At this node distortion is sufficiently high to make the analyzer contribution neglible.

On a different, but related topic, it is relatively easy to improve linearity of FETs in VCR applications via feedback (Siliconix Application Note AN105). I have not tried this, it looks like it might have merit for applications such as this.

That's already implemented (R13 provides drain feedback). Otherwise multiplier distortion would be gross.

If there's sufficient interest I might be willing to look into the multiplier implementation of this particular oscillator in more detail. Intuition suggests that some optimisation of the operating levels might reduce distortion but I'd need to verify this.

Samuel

Well, I have studied this subject here and read the article series a few times, to really understand the design.

I simulated the oscillator in LT-spice. Well, I found the 5534 models, but the simulator ran smoother with LT1037.

Anyway, I confiugered the oscillator to run in 1kHz mode.

Bob recommended a four phase rectifier, I set out to test this.

I measured the ripple voltage at the output of IC7 and found it to be 1.7mVpp after 2s with a full wave rectifier.

I reran the test with a four phase rectifier and found the ripple to be 0.8mVpp. Changing C10 to 1uF reduces the ripple to 200uVpp.

Anybody that has identified the regulation parameters of the system, to get an optimized amplitude regulation in the oscillator?

I simulated the oscillator in LT-spice. Well, I found the 5534 models, but the simulator ran smoother with LT1037.

Anyway, I confiugered the oscillator to run in 1kHz mode.

Bob recommended a four phase rectifier, I set out to test this.

I measured the ripple voltage at the output of IC7 and found it to be 1.7mVpp after 2s with a full wave rectifier.

I reran the test with a four phase rectifier and found the ripple to be 0.8mVpp. Changing C10 to 1uF reduces the ripple to 200uVpp.

Anybody that has identified the regulation parameters of the system, to get an optimized amplitude regulation in the oscillator?

The simulator ran smoother with LT1037.

The LT1037 is not unity-gain stable so at least the integrators should show oscillation (at the wrong frequency)... So much to the accuracy of the opamp models.

Bob recommended a four phase rectifier, I set out to test this. I measured the ripple voltage at the output of IC7 and found it to be 1.7 mVpp after 2 s with a full wave rectifier. I reran the test with a four phase rectifier and found the ripple to be 0.8 mVpp.

The advantage of the four-phase rectifier is not just the lower ripple but mainly the higher order (i.e. fundamental frequency) of the ripple; this results in better low-pass filtering of the resulting harmonic distortion. In practice time constant mismatch in the integrator stages will limit the effectiveness of the four-phase rectifier. Also the amplitude flatness will be compromised.

Anybody that has identified the regulation parameters of the system, to get an optimized amplitude regulation in the oscillator?

This is a very complicated problem, particularly above some kHz where the opamps can't be assumed to have infinite loop gain. As a starter you need to do the following things for optimum settling behaviour:

* The gain of the AGC loop above the integrator zero must be set to some optimum value which depends on multiplier gain constant (and decoupling), steady-state oscillator level and the used level detector architecture.

* The time constant of the integrator must be made proportional to the oscillator frequency and as high as phase margin constraints allow.

You'll quickly find out that the first statement results in much higher distortion because level detector ripple is pronounced. If you want an oscillator with fast settling (a couple of cycles) and very low distortion (< -100 dBc) you need a *much* better level detector. IME the most suitable topology is a track-and-hold/sample-and-hold level detector. This approach is well described here:

* 1985-12.pdf, pp. 31-35

* 1980-08.pdf, pp. 3-17

Samuel

Thanks!,

I have read the articles and I will return to them for further reference. I found the 8903 manual with schematics on the net, I will study the schematics and come back with some more conclusions and/or questions.

Thanks for informing me of the LT amplifier, I didn't intend to really use it, but I needed something to simulate the system with, to learn the circuit.

I have read the articles and I will return to them for further reference. I found the 8903 manual with schematics on the net, I will study the schematics and come back with some more conclusions and/or questions.

Thanks for informing me of the LT amplifier, I didn't intend to really use it, but I needed something to simulate the system with, to learn the circuit.

Thanks for the litterature reference. I will keep on studying.

The 8642 reference was really good reading, it gave me a somewhat theoretical explanation to my "experimental" findings in LT-spice, where the amplitude got an exponential growth or decay ( exp(kt)) as a step response.

I still haven't got to the control equation. But I have some ideas, it's usually only once a year that I do control theory calculations.

I promise to get back with the calculations, as soon as I have something to present.

The 8642 reference was really good reading, it gave me a somewhat theoretical explanation to my "experimental" findings in LT-spice, where the amplitude got an exponential growth or decay ( exp(kt)) as a step response.

I still haven't got to the control equation. But I have some ideas, it's usually only once a year that I do control theory calculations.

I promise to get back with the calculations, as soon as I have something to present.

Hi again,

Some more questions.

The oscillator, is it still the state variable oscillator that still is the best audio oscillator. Analog devices have some DDS circuits that might be usable, since they run at around 100MHz.

I saw that both the HP8903 and APS-1 one had State variable oscillators, as well as Bobs. But both AP and HP do the resistor switching with FETs. AP has a mystic hybrid called MDAC.

It seems that AP did a better job since they specify 92dB THD+N where HP only gets 80dB, the same as Bob!

The AP schematic has more "magic" in it in the form of feedback/forward resistors, whereas HP is more straight on.

I beleive they chose to do the control with FETs for cost and/or reliability.

I was planning to use DPDT relays for swithing the RC-nets. DPDT are the cheepest relays, and they can control both integrators.

But there is the reliability issue.

I will try to look for a good library to read about the oscillators

Some more questions.

The oscillator, is it still the state variable oscillator that still is the best audio oscillator. Analog devices have some DDS circuits that might be usable, since they run at around 100MHz.

I saw that both the HP8903 and APS-1 one had State variable oscillators, as well as Bobs. But both AP and HP do the resistor switching with FETs. AP has a mystic hybrid called MDAC.

It seems that AP did a better job since they specify 92dB THD+N where HP only gets 80dB, the same as Bob!

The AP schematic has more "magic" in it in the form of feedback/forward resistors, whereas HP is more straight on.

I beleive they chose to do the control with FETs for cost and/or reliability.

I was planning to use DPDT relays for swithing the RC-nets. DPDT are the cheepest relays, and they can control both integrators.

But there is the reliability issue.

I will try to look for a good library to read about the oscillators

- Status

- This old topic is closed. If you want to reopen this topic, contact a moderator using the "Report Post" button.

- Home

- Amplifiers

- Solid State

- My implementation of the Cordell Distortion Analyser