Hi,

This might be a very stupid question, if so please forgive me!

I am using my CD-PRO2 drive with a 0-oversampling DAC based on 2 x TDA 1543. The DAC's input is I2S from the CD-PRO2.

I wonder if it makes sense to re-clock the I2S data at the input of the DAC. If so how do I do this?

Please your comments.

Thanks for reading.

Peter K.

This might be a very stupid question, if so please forgive me!

I am using my CD-PRO2 drive with a 0-oversampling DAC based on 2 x TDA 1543. The DAC's input is I2S from the CD-PRO2.

I wonder if it makes sense to re-clock the I2S data at the input of the DAC. If so how do I do this?

Please your comments.

Thanks for reading.

Peter K.

rfbrw said:Here is an example. RECLK is 512 Fs

Thanks for your reply. Can you please explain what you mean with 512 Fs in relation to the RCLK.

Best regards,

Peter K.

512 Fs means the samplerate (Fs) multiplied by 512. In the case the 74HC74 flip-flops would have a 22.5792MHz clock with a CD source (512 x 44100Hz). It does not have to 512Fs. It could also be 256Fs but it must be synchronous with respect to the data lines being clocked i.e. the clock is an integer multiple of Fs otherwise one creeps into the world of samplerate conversion through the backdoor.

ray

ray

rfbrw said:In the case the 74HC74 flip-flops would have a 22.5792MHz clock with a CD source (512 x 44100Hz).

What are the requirements on the clock, must this be HQ? Do you have an idea where to find a complete diagram?

Thanks,

Peter K.

Low noise and low jitter. Jocko Homo has posted a schematic for a clock on this forum and Elso Kwak has one he sends out on request. I have been content to use encapsulated oscillators that come in 8 and 14 pin dip sizes.

In the example I posted the clock came from a VCXO-based PLL locked to the FSYNC signal from the input receiver. For another example of a PLL based design see,

http://httpd.chello.nl/~m.heijligers/DAChtml/dactop.htm

There is an unconventional form of reclocking where the oscillator is freestanding and asynchronous with respect to the data and clock lines being reclocked. If this is what you are after then Elso Kwak is the man with the plan.

While it is useful to have a schematic there really isn't much more to reclocking that is applicable to a non o/s dac. All you have to do is decide on the nature of the clock you drive the flip-flops with.

In the example I posted the clock came from a VCXO-based PLL locked to the FSYNC signal from the input receiver. For another example of a PLL based design see,

http://httpd.chello.nl/~m.heijligers/DAChtml/dactop.htm

There is an unconventional form of reclocking where the oscillator is freestanding and asynchronous with respect to the data and clock lines being reclocked. If this is what you are after then Elso Kwak is the man with the plan.

While it is useful to have a schematic there really isn't much more to reclocking that is applicable to a non o/s dac. All you have to do is decide on the nature of the clock you drive the flip-flops with.

Asynchronous Reclocking

Hi Peter,

If you are using Asynchronous Reclocking the clock frequency can be as high as 125 MHz. When using a asynchronous clock you need two filip-flops in series to avoid the metastabillity problem.. See Feddes site. For Asynchronous reclocking the frequency does not need to be a multiple of the CD-sampling frequency.

http://home.student.utwente.nl/f.s.bouwman/audio/nonoz.html

Click on the schematic of the DAC.

The quality of the clock used is reflected in the sound quality of the result. Tones 80 MHz oscillator also works as well as Vite on Lines VCC1 125 MHz oscillator.

www.viteonline.com

😉

Hi Peter,

If you are using Asynchronous Reclocking the clock frequency can be as high as 125 MHz. When using a asynchronous clock you need two filip-flops in series to avoid the metastabillity problem.. See Feddes site. For Asynchronous reclocking the frequency does not need to be a multiple of the CD-sampling frequency.

http://home.student.utwente.nl/f.s.bouwman/audio/nonoz.html

Click on the schematic of the DAC.

The quality of the clock used is reflected in the sound quality of the result. Tones 80 MHz oscillator also works as well as Vite on Lines VCC1 125 MHz oscillator.

www.viteonline.com

😉

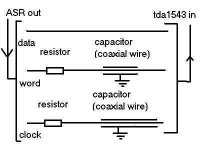

I'm sorry my first post was very short and I was on the moon.

The image post is not very good too.

Well,my trick seems strange and my explanation are far from perfect.

Let's go:

-when i lesson it,it's improve the sound.

-it cost nothing (2 resistors and a few coaxial wire).

-it's easy.

Well,why i have doing this:

-the three signals from the ASR are locked with the same very high frequency (100Mhz).

-a phase shift between this three signals can maybe (with bad luck) produce some audio noise into the tda1543.Why not,we use a phase shift(from the same signal) in radio to brodcast music(FM).

-if we can't suppress this phase shift we can increase it.

-bigger it is,higher is the frequency of the noise (whith luck over the audio frequency).

-the tda1543 tolerate some phase shift between the three signals.

How to do this:

-for increase the phase shift,we can use a Resistor Capacitor filter.

-100 ohm for the resistor.

-capacitor:capacitive effect of a coaxial wire.

-data signal is the reference:do nothing.

-word select signal:increase the phase shift between the word select signal and the data signal (use a 100 ohm resistor and 1cm of coaxial wire).

-bit clock signal:increase the phase shift between the bit clock signal,the word select signal and the data signal too (use a 100 ohm resistor and 2cm of coaxial wire).

Like this:the phase between the three signals are not equal or too close.

The image post is not very good too.

Well,my trick seems strange and my explanation are far from perfect.

Let's go:

-when i lesson it,it's improve the sound.

-it cost nothing (2 resistors and a few coaxial wire).

-it's easy.

Well,why i have doing this:

-the three signals from the ASR are locked with the same very high frequency (100Mhz).

-a phase shift between this three signals can maybe (with bad luck) produce some audio noise into the tda1543.Why not,we use a phase shift(from the same signal) in radio to brodcast music(FM).

-if we can't suppress this phase shift we can increase it.

-bigger it is,higher is the frequency of the noise (whith luck over the audio frequency).

-the tda1543 tolerate some phase shift between the three signals.

How to do this:

-for increase the phase shift,we can use a Resistor Capacitor filter.

-100 ohm for the resistor.

-capacitor:capacitive effect of a coaxial wire.

-data signal is the reference:do nothing.

-word select signal:increase the phase shift between the word select signal and the data signal (use a 100 ohm resistor and 1cm of coaxial wire).

-bit clock signal:increase the phase shift between the bit clock signal,the word select signal and the data signal too (use a 100 ohm resistor and 2cm of coaxial wire).

Like this:the phase between the three signals are not equal or too close.

Attachments

Trick

Hi Herve,

I am sorry but for me it is totally unclear why you want to introduce phaseshift into the digital signals. What do you want to accomplish?

With my Asynchronous Reclocker my idea was just to preserve the timing relations of the digital signals and not to upset them. 😕 😕 😕

Hi Herve,

I am sorry but for me it is totally unclear why you want to introduce phaseshift into the digital signals. What do you want to accomplish?

With my Asynchronous Reclocker my idea was just to preserve the timing relations of the digital signals and not to upset them. 😕 😕 😕

Re: Trick

Perhaps he just likes what it does to the sound.

Elso Kwak said:Hi Herve,

I am sorry but for me it is totally unclear why you want to introduce phaseshift into the digital signals. What do you want to accomplish?

With my Asynchronous Reclocker my idea was just to preserve the timing relations of the digital signals and not to upset them. 😕 😕 😕

Perhaps he just likes what it does to the sound.

timing or waveform ?

Is this a matter of getting better timing acuracy ( clocking )... or just to have steeper waveforms ... I don't get it .

Wouldn't it be a better idea to use HQ low jitter XO in first place ? than listen to the results first ....

Is this a matter of getting better timing acuracy ( clocking )... or just to have steeper waveforms ... I don't get it .

Wouldn't it be a better idea to use HQ low jitter XO in first place ? than listen to the results first ....

Re: Re: Trick

Hi Rfbrw,

Sure,

Quote:

"It's improve the sound"

rfbrw said:

Perhaps he just likes what it does to the sound.

Hi Rfbrw,

Sure,

Quote:

"It's improve the sound"

- Status

- Not open for further replies.

- Home

- Source & Line

- Digital Source

- Re-clocking the data with I2S