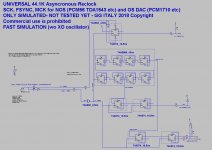

Hello, after many internet and DIYAUDIO navigation, I mixed some of the best idea I found (Doede, Elso, etc), and I’m going to build the following ASYNC re-clock circuit.

(I know that the very best would be PLL &VXCO or send back the MCK to the player, but this is too much complicated for my purpose. I know that result will be missed or duplicated samples (hope not too many!), but many people here say that async sounds good and better)

1) Instead of 74HC4040 async counter, I will use 74AS869 TTL Sync 8-bit counter. This is very fast and, important, still in a unique and DIP package.

2) Output is TTL and I will rise to CMOS level with a 500ohm or 1K resistor. In fact while the majority of DAC can receive TTL at their inputs, CS4303 receive only CMOS (VD-1=4V min)

3) I never heard that 74AS suffers from “ground bounce”, like 74AC which I have discharged for this reason

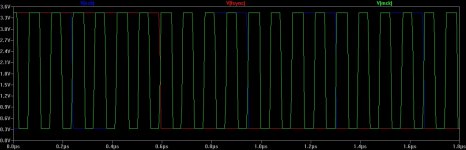

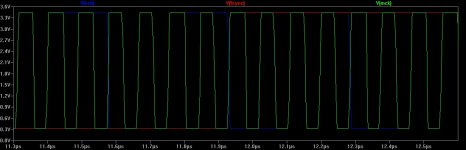

4) I’m going to re-clock with a low jitter COLPITTS crystal clocks with two parallel J310 FET and AD8611 comparator in single supply. Simulated curves are very nice using the attached polarization. I will put a trimmer for the negative input.

5) I’m going to re-clock FSYNC, SCK to CS8412/14 (in slave mode) and to NOS DAC (TDA1543 and PCM56), but also MCK to OS Delta-Sigma DAC like (PCM1710 and CS4303).

6) By using 11.289 MHz MCK, the Delta Sigma DACs will work only at at 256x and not 384x. May be that these OS DAC will “sound” better using the lower rate…

7) Even if 74AS869 is synchronous, I’ll further synchronise all signals by using a cascade set of fast latches 74AS74.

8) I have put few “ns” of delay (74AS02) to better synchronise MCK’ edges to SCK and FSYNC.

9) I will use complementary output capability of 74AS74 to select right and left channels of the PCM56 couple of chips, without having delays between the two channels when using a simple 7404 inverter.

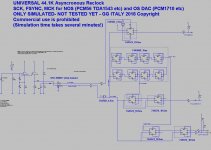

10) Everything works perfectly synchronously on LTspice even by exceeding maximum datasheets’ delays; I don’t know in reality, thus I’m posting this hoping in any your suggestion before building this.

PS: This is my first DAC construction. I decided to build and test 4 DIY different DAC: two OS with delta-sigma (PCM1710 and CS4303), and two NOS (TDA1543 and PCM56). I have all chips, now obsolete, bought from China. Not tested yet, hope they are not fake! So I don’t know if working. After listening I will choose the best configuration, and upgrade just this one by ears.

(I know that the very best would be PLL &VXCO or send back the MCK to the player, but this is too much complicated for my purpose. I know that result will be missed or duplicated samples (hope not too many!), but many people here say that async sounds good and better)

1) Instead of 74HC4040 async counter, I will use 74AS869 TTL Sync 8-bit counter. This is very fast and, important, still in a unique and DIP package.

2) Output is TTL and I will rise to CMOS level with a 500ohm or 1K resistor. In fact while the majority of DAC can receive TTL at their inputs, CS4303 receive only CMOS (VD-1=4V min)

3) I never heard that 74AS suffers from “ground bounce”, like 74AC which I have discharged for this reason

4) I’m going to re-clock with a low jitter COLPITTS crystal clocks with two parallel J310 FET and AD8611 comparator in single supply. Simulated curves are very nice using the attached polarization. I will put a trimmer for the negative input.

5) I’m going to re-clock FSYNC, SCK to CS8412/14 (in slave mode) and to NOS DAC (TDA1543 and PCM56), but also MCK to OS Delta-Sigma DAC like (PCM1710 and CS4303).

6) By using 11.289 MHz MCK, the Delta Sigma DACs will work only at at 256x and not 384x. May be that these OS DAC will “sound” better using the lower rate…

7) Even if 74AS869 is synchronous, I’ll further synchronise all signals by using a cascade set of fast latches 74AS74.

8) I have put few “ns” of delay (74AS02) to better synchronise MCK’ edges to SCK and FSYNC.

9) I will use complementary output capability of 74AS74 to select right and left channels of the PCM56 couple of chips, without having delays between the two channels when using a simple 7404 inverter.

10) Everything works perfectly synchronously on LTspice even by exceeding maximum datasheets’ delays; I don’t know in reality, thus I’m posting this hoping in any your suggestion before building this.

PS: This is my first DAC construction. I decided to build and test 4 DIY different DAC: two OS with delta-sigma (PCM1710 and CS4303), and two NOS (TDA1543 and PCM56). I have all chips, now obsolete, bought from China. Not tested yet, hope they are not fake! So I don’t know if working. After listening I will choose the best configuration, and upgrade just this one by ears.

Attachments

-

UNIVERSAL ASYNC CLOCK (LT1711).asc14.5 KB · Views: 56

-

ASync reclock.jpg206.6 KB · Views: 201

ASync reclock.jpg206.6 KB · Views: 201 -

ASync reclock complete.jpg205.5 KB · Views: 185

ASync reclock complete.jpg205.5 KB · Views: 185 -

UNIVERSAL ASYNC CLOCK (fast simulation).asc11.5 KB · Views: 47

-

Falling FSYNC signals.jpg78.7 KB · Views: 162

Falling FSYNC signals.jpg78.7 KB · Views: 162 -

Rising FSYNC signals.jpg70.8 KB · Views: 158

Rising FSYNC signals.jpg70.8 KB · Views: 158