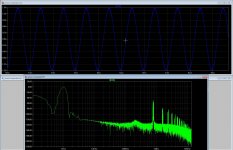

I do see oscillations in the risetimes, or heavenly ringing or maybe shoot through?

Perhaps it helps to realize that these are perforated board prototypes built to demonstrate the validity of the idea, not the actual performance.

You did notice when the initial posts were made yes?

yes ssassen but i think maybe you perfected your ucd hysteirs or hysteris version because it showed very low distortion . maybe made a compact dualsided board with a small daughter driver board near the output fets for optimum layout and perfomance

Perhaps it helps to realize that these are perforated board prototypes built to demonstrate the validity of the idea, not the actual performance.

Oke thanks, yes then it will go wrong, Have you never think of a bessel 24dB low pass filter?, I do not mention previous post..

Buy the way, is there somewhere a good model for the IR2110 chip? mine do not work, get 3 amps on SD pin and K-amp 0n VCC thanks in advance.

regards

Attachments

This was a quick breadboard design I whipped up 15 years ago (!) so no, as that IC wasn’t available back then.

This was a quick breadboard design I whipped up 15 years ago (!) so no, as that IC wasn’t available back then.

thanks for the reply , please post here your latest projects .