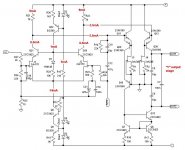

R21, Q11, Q29 and R22, Q13, Q30 are components of a well known ccs, aka "two BJT CCS".

J3, R1 and J4, R2 are another two current sources used for first two ccs biasing (2sk246 has zero tempco at 0.34mA)

That first two BJT ccs form a folded cascode VAS because R11 and R22 currents are modulated by LTP currents.

J3, R1 and J4, R2 are another two current sources used for first two ccs biasing (2sk246 has zero tempco at 0.34mA)

That first two BJT ccs form a folded cascode VAS because R11 and R22 currents are modulated by LTP currents.

roender said:R21, Q11, Q29 and R22, Q13, Q30 are components of a well known ccs, aka "two BJT CCS".

You've drawn Q11 and Q13 upside down.

Cheers

Alex

roender said:What do you think about this amp?

Looks OK. It is not in my taste thought. Too many transistiors for too little OL gain 🙂 . Also I would not use 2SK170 for the input as these have too much capacitance (IMHO) . My preferred VAS is here:

http://www.diyaudio.com/forums/showthread.php?s=&threadid=104205

In one of the versions I've used a cascoded JFET pair (selected BF244B) on the input (in a similar arrangement to your schematics) with very good results (in Creek A52/A52SE power amplifier).

Cheers

Alex

95dB OLG it is ok for a moderate NFB design.

As per k170, I like the sound of Toshiba jfets.

It is important to have a low capacitance j-fet in a cascoded stage?

Thank you,

Mihai

As per k170, I like the sound of Toshiba jfets.

It is important to have a low capacitance j-fet in a cascoded stage?

Thank you,

Mihai

Alex,

if input diff pair is FET and it drives a cascode, surely the input capacitance is less of a problem? What's your view on this?

I've simulated this type of input circuit on a pre-amp design and get great results.

if input diff pair is FET and it drives a cascode, surely the input capacitance is less of a problem? What's your view on this?

I've simulated this type of input circuit on a pre-amp design and get great results.

roender said:95dB OLG it is ok for a moderate NFB design.

As per k170, I like the sound of Toshiba jfets.

It is important to have a low capacitance j-fet in a cascoded stage?

95dB sounds fine. Is this figure from a simulation?

Re. JFET - I found in the past that higher capacitance in the input stage is not very good for the sound. However in your circuit you need as high transconductance as possible in a first stage otherwise you will lose the OL gain.

Cheers

Alex

x-pro said:

95dB sounds fine. Is this figure from a simulation?

Re. JFET - I found in the past that higher capacitance in the input stage is not very good for the sound. However in your circuit you need as high transconductance as possible in a first stage otherwise you will lose the OL gain.

Cheers

Alex

Yes, 95dB come from simulation.

It is a one stage amp and as you already had mention, it is nice to have a high transconductance LTP (see how big is the cureent in the front stage ...) Also, a good current mirror in the "VAS" is another trick used to enable high OLG

roender said:

Also, a good current mirror in the "VAS" is another trick used to enable high OLG

According to J. Carr, for proper FC operation (soundwise and measurements) we need an active CS for FC transistors. Another good trick is to use a voltage regulator with low impedance output to bias the bases of FC transistors (place a base stoppers form 47~100R if you experience some oscillation).

aparatusonitus said:

According to J. Carr, for proper FC operation (soundwise and measurements) we need an active CS for FC transistors. Another good trick is to use a voltage regulator with low impedance output to bias the bases of FC transistors (place a base stoppers form 47~100R if you experience some oscillation).

I known all that recommendations. Jonathan Carr is a big fan of FC topology

Firstly, I have an active CCS for folded cascode transistor.

The front stage will be supplied separately, from a good PSU.

Thank you for remind me that

Because I have a triple darlington output stage, there is no need for more current.darkfenriz said:You/ve chosen aa rather small idle current of the second stage compared to first stage. Why?

You see, when we use active CCS cascode, there is no limitation in "VAS" current. With standard folded cascode, when you increase current in "VAS" you also decrease OLG.

With only 2.5mA "VAS" current I have 75V/us SR which is more than enough

aparatusonitus said:Look for pat.#4959622 and Fig.1b explenation, may be of interest.

The patent, which try to make LTP current equal to 2x differential folded cascode current by using a current mirror between LTP and differential folded cascode stage, it's very hard to be implemented. The circuit will easily oscillate like hell...

Also, will be impossible to apply that patent in a LTP cascoded stage with floating bias reference.

- Status

- Not open for further replies.

- Home

- Amplifiers

- Solid State

- Smart Folded Cascode power amp, SFCamp