I came across a stash of PCM56 chips years ago and am looking to build a modern DAC around them. The analog side is straightforward enough, but after reading many threads about how manage the digital connections, I'm hoping to get a quick sanity check from the community before getting too deep into to board layout.

The goal is to connect an Amanero Combo384 to four PCM56s for hardware balanced analog outputs, similar to the Parasound DAC1600, Adcom GDA-700, Pass D1, etc. I'll be using the Amanero clock with settings recommended by Domenico at Amanero, but I'm open to doing things differently if anyone has suggestions to improve the jitter performance. I'm concerned the isolator and gates will introduce jitter but am not sure if it's possible to slave the Amanero to a clock on the DAC.

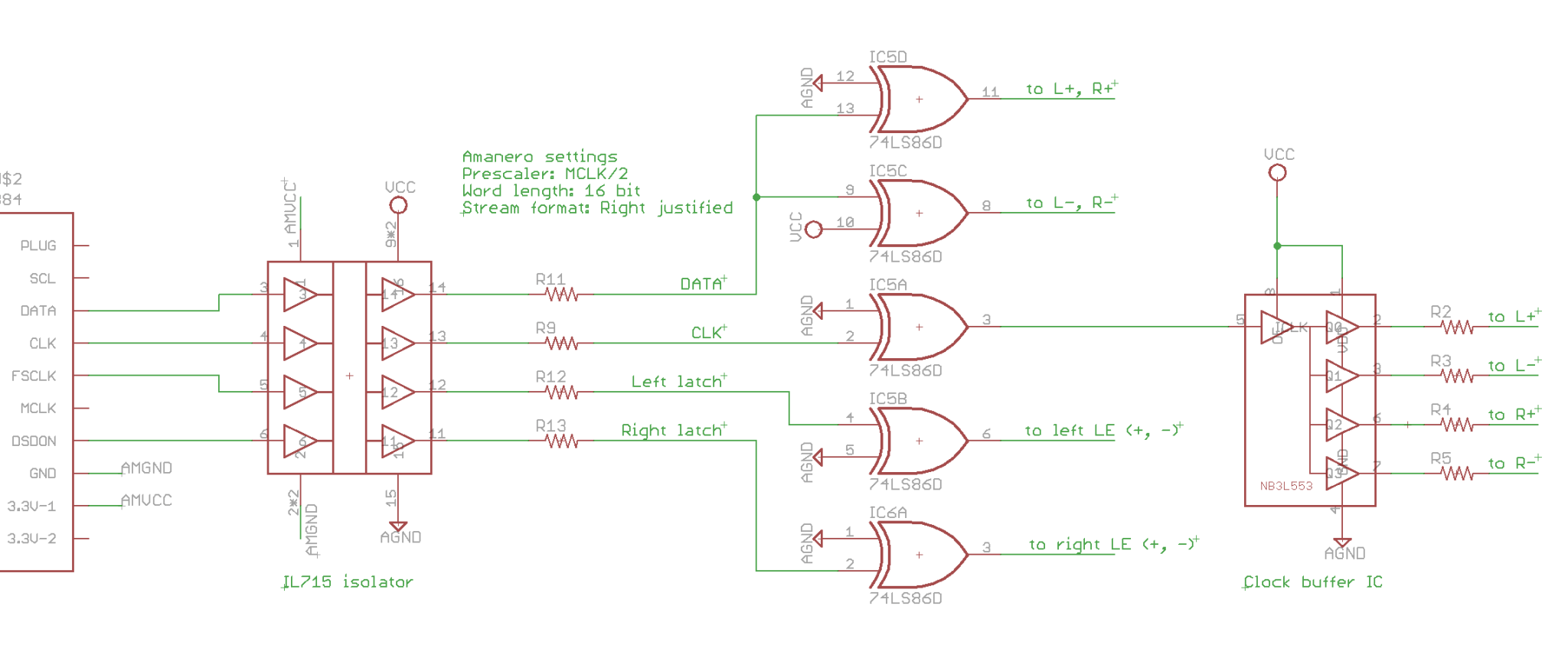

Here's the glue logic I plan on using. Does this look like it'll work? Would anyone do it differently?

The goal is to connect an Amanero Combo384 to four PCM56s for hardware balanced analog outputs, similar to the Parasound DAC1600, Adcom GDA-700, Pass D1, etc. I'll be using the Amanero clock with settings recommended by Domenico at Amanero, but I'm open to doing things differently if anyone has suggestions to improve the jitter performance. I'm concerned the isolator and gates will introduce jitter but am not sure if it's possible to slave the Amanero to a clock on the DAC.

Here's the glue logic I plan on using. Does this look like it'll work? Would anyone do it differently?

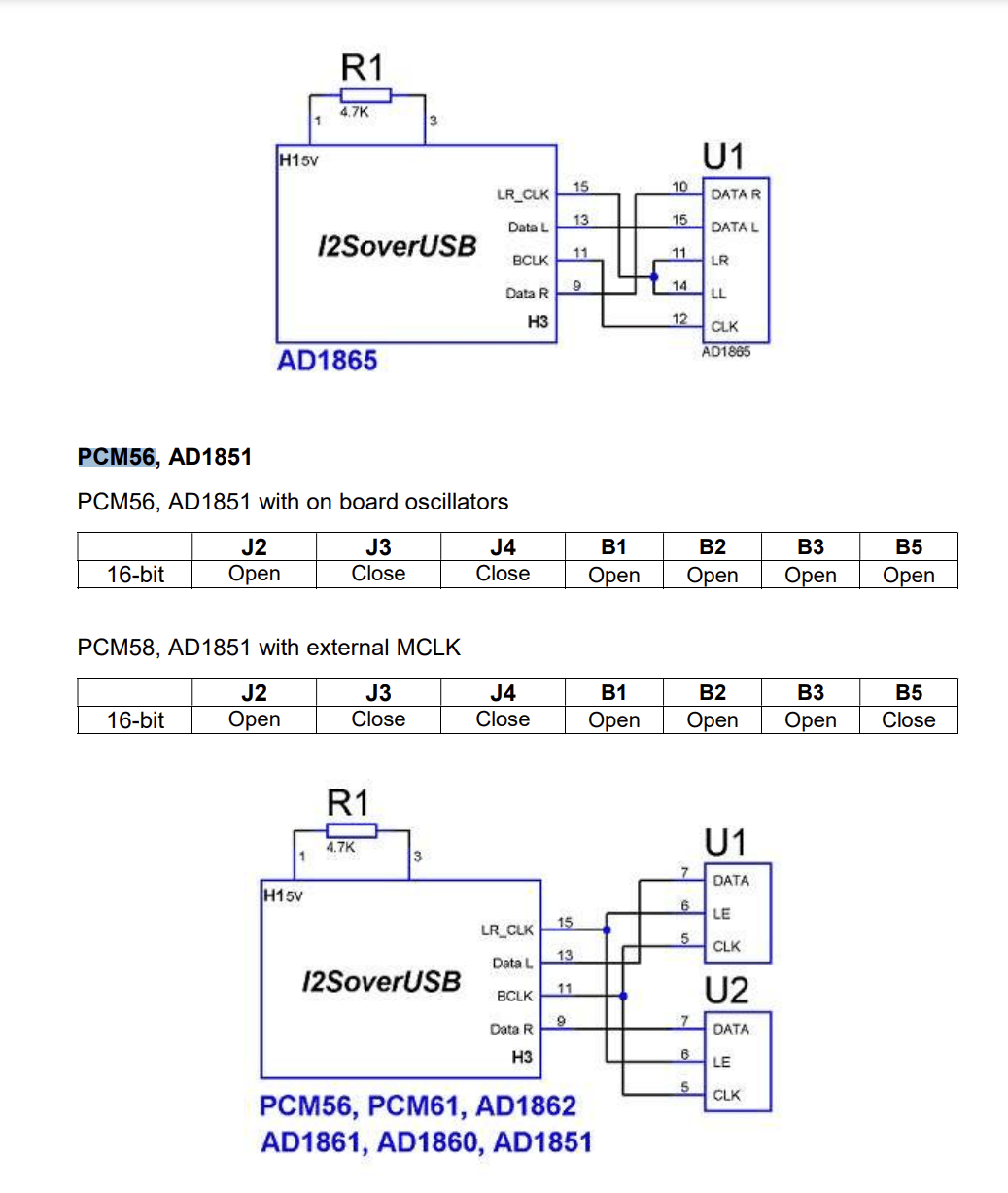

Why use Amanero? I2SoverUSB has built-in support for PCM56 and it costs around the same as a real Amanero.

Image from I2SoverUSB manual.

Image from I2SoverUSB manual.

Sorry for replying sooner!Why use Amanero? I2SoverUSB has built-in support for PCM56 and it costs around the same as a real Amanero.

I'm not opposed to switching receivers. Amanero suggests supplying both chips with the same data stream and providing an inverted LE to each chip should do it, using a different firmware. I can't say I know enough about digital to tell if this is a good idea or not.

That said, I think the I2SoverUSB solution only gets me halfway there if I want to made a hardware balanced DAC. IanCanada has an I2S to PCM converter board which natively supports balanced PCM56s. Perhaps this is the right solution, but it strikes me as a complex way of doing something that should be simple, considering that it requires a separate USB to I2S interface.

There is more than one way to do it. Studying the PCM56 datasheet should tell you most or all of what you need to know.

This is an old one, which Ljuben doesn't sell anymore. New one (FIO) doesn't require resistor jumping. Just to say, in case op chooses i2soverusb board.Why use Amanero? I2SoverUSB has built-in support for PCM56 and it costs around the same as a real Amanero.

View attachment 1288255

Image from I2SoverUSB manual.

@PretentiousFood send an email to Ljuben, he will respond to you with the most info you require. In the meantime, study datasheet as markw4 said, it will help you in general in the long run to study datasheets.

I think I got this figured out. It's my first time using any sort of logic circuit, so I was hoping to get some feedback on anything that seems off. 🙂

I haven't heard back from Amanero and so plan on using external glue logic to convert the I2S signal to BTC, then the Pass D1 glue logic to create a balanced signal. The Amanero unit will run in slave mode; there is an app note on how to set up the firmware, but I haven't seen any hardware implementations.

The ADuM341E isolator sends the FSCLK, DATA, and sample rate to the DAC board. Local oscillators (11.2896MHz & 12.288MHz) act as BCK and are fed back to the Amanero board.

The two local oscillators are NDK parts. I couldn't source the correct frequency oscillators, so am running them through divide-by-2 logic before feeding them to a fanout buffer. The oscillators will remain always on, and the Amanero board controls the enable pin of the fanout buffers through an inverter.

The DATA lines are delayed with a shift register to generate the left and right DATA lines. This is Miro's circuit, augmented with a fanout buffer for clock distribution.

Lastly, this is the schematic for one balanced channel. The LRCLK and DATA lines are both fed through a two-level synchronous reclocker (reference figure 4 of TI app note SCAA042A). This goes to a quad XOR gate to generate the balanced DATA lines and to delay the CLK/LE lines. The optional MSB adjust is implemented. The I/V stage is undecided for now.

Some questions that come to mind--

1. The clock is at a 3.3V logic level, as the good fanout buffers and oscillators are all 3.3V parts, and I assume level translation will do more harm than good. Is this a reasonable hypothesis?

2. I considered eliminating the XOR gates and using the Q-bar output of the reclocker for LE, but I understand there's a 150ps-or-so delay on the Q-bar pin relative to Q. I would expect that to be immaterial here. Would it be beneficial to use the Q-bar output, and eliminate the XOR gate?

3. I used the AHCT logic family throughout as this is as fast as it gets with 5V logic. Should I consider anything else?

Any feedback would be greatly appreciated, I'm sure a trained eye will spot plenty of opportunities to improve the circuit. 🙂

Thanks!

I haven't heard back from Amanero and so plan on using external glue logic to convert the I2S signal to BTC, then the Pass D1 glue logic to create a balanced signal. The Amanero unit will run in slave mode; there is an app note on how to set up the firmware, but I haven't seen any hardware implementations.

The ADuM341E isolator sends the FSCLK, DATA, and sample rate to the DAC board. Local oscillators (11.2896MHz & 12.288MHz) act as BCK and are fed back to the Amanero board.

The two local oscillators are NDK parts. I couldn't source the correct frequency oscillators, so am running them through divide-by-2 logic before feeding them to a fanout buffer. The oscillators will remain always on, and the Amanero board controls the enable pin of the fanout buffers through an inverter.

The DATA lines are delayed with a shift register to generate the left and right DATA lines. This is Miro's circuit, augmented with a fanout buffer for clock distribution.

Lastly, this is the schematic for one balanced channel. The LRCLK and DATA lines are both fed through a two-level synchronous reclocker (reference figure 4 of TI app note SCAA042A). This goes to a quad XOR gate to generate the balanced DATA lines and to delay the CLK/LE lines. The optional MSB adjust is implemented. The I/V stage is undecided for now.

Some questions that come to mind--

1. The clock is at a 3.3V logic level, as the good fanout buffers and oscillators are all 3.3V parts, and I assume level translation will do more harm than good. Is this a reasonable hypothesis?

2. I considered eliminating the XOR gates and using the Q-bar output of the reclocker for LE, but I understand there's a 150ps-or-so delay on the Q-bar pin relative to Q. I would expect that to be immaterial here. Would it be beneficial to use the Q-bar output, and eliminate the XOR gate?

3. I used the AHCT logic family throughout as this is as fast as it gets with 5V logic. Should I consider anything else?

Any feedback would be greatly appreciated, I'm sure a trained eye will spot plenty of opportunities to improve the circuit. 🙂

Thanks!

I presume you are aware that I2SoverUSB already has the ability to directly drive PCM56?

Also, I2SoverUSB works fine with external clocking, reclocking, etc.

Also, I2SoverUSB works fine with external clocking, reclocking, etc.

I presume you are aware that I2SoverUSB already has the ability to directly drive PCM56?

I am aware. This would avoid the 6 shift registers, but I'll still need some glue logic to get the DACs to operate in balanced mode. I'd like to stick with Amanero since I already have a genuine unit and am familiar with the setup, unless it really is a terrible idea.

Also, if you are not supplying an external clock for Amanero, then you will need an ASRC. You can only have one clock domain at a time without resampling.

The clock on the DAC board will be driving pin 6 of the Amanero, with pin 1 acting as the clock selector. I think this works, per their application note. Unless I'm missing something?

https://amanero.com/drivers/AN-05.pdf

Yeah, I edited my post after I noticed the MCLK signal flow direction detail.

Maybe the only thing I2SoverUSB would get you in this case would be an extra layer of galvanic isolation. Does it matter? IME, it can. Also IIRC, Iancanada used to recommend two layers of isolation for best results (such as for McFIFO). At least it may help to run Amanero from clean +5v power.

Maybe the only thing I2SoverUSB would get you in this case would be an extra layer of galvanic isolation. Does it matter? IME, it can. Also IIRC, Iancanada used to recommend two layers of isolation for best results (such as for McFIFO). At least it may help to run Amanero from clean +5v power.

I am a bit confused with the fact that you are not using BCK line from the Amanero.

If you generate it yourself (according to schematic), it is going to be a different clock domain. You can't use it to latch data from Amanero. Yes, the frequency is the same but not the phase.

Second problem is that this clock is hardwired to be 22 or 24Mhz divided by two. That would only work for fs = 192 or 176.4kHz. But if you select 48 or 96 kHz - you would not be able to correctly sample the data. Or am I missing something?

I'd say that correct way of doing it is to have all signals from amanero reclocked by the masterclock (22/24MHz), including the BCK. Like here:

(This is not I2S but just to illustrate the point)

(On the last page there is also a picture of future isolated version)

For balanced option it would still require two inverters and registers for reclocking.

I'll think about option of driving 4 dacs in balanced configurtion but not sure if it is possible with current hardware.

If you generate it yourself (according to schematic), it is going to be a different clock domain. You can't use it to latch data from Amanero. Yes, the frequency is the same but not the phase.

Second problem is that this clock is hardwired to be 22 or 24Mhz divided by two. That would only work for fs = 192 or 176.4kHz. But if you select 48 or 96 kHz - you would not be able to correctly sample the data. Or am I missing something?

I'd say that correct way of doing it is to have all signals from amanero reclocked by the masterclock (22/24MHz), including the BCK. Like here:

(This is not I2S but just to illustrate the point)

Yes, you can make it work with Amanero. But I also would like to mention my project which can interface PCM56 direclty too:I am aware. This would avoid the 6 shift registers, but I'll still need some glue logic to get the DACs to operate in balanced mode. I'd like to stick with Amanero since I already have a genuine unit and am familiar with the setup, unless it really is a terrible idea.

Hello DiyAudio community,

TL;DR: This is a USB transport for audio output (up to 8ch) and input (2ch for now) and user device control (e.g., DSP management) from PC (MacOS/Linux/Windows) thru I2C/GPIO. Including bootloader for remote firmware update, flexible device configuration, HID interface, multiple audio output options, integration with SigmaStudio (simultanious audio playback and ADAU DSP configuration). Compact module available in USB-C and USB-B versions, isolated or non-isolated.

Latest docs, config tool, link to buy:

http://york.eclipsevl.org/...

TL;DR: This is a USB transport for audio output (up to 8ch) and input (2ch for now) and user device control (e.g., DSP management) from PC (MacOS/Linux/Windows) thru I2C/GPIO. Including bootloader for remote firmware update, flexible device configuration, HID interface, multiple audio output options, integration with SigmaStudio (simultanious audio playback and ADAU DSP configuration). Compact module available in USB-C and USB-B versions, isolated or non-isolated.

Latest docs, config tool, link to buy:

http://york.eclipsevl.org/...

- eclipsevl

- Replies: 222

- Forum: Vendor's Bazaar

(On the last page there is also a picture of future isolated version)

For balanced option it would still require two inverters and registers for reclocking.

I'll think about option of driving 4 dacs in balanced configurtion but not sure if it is possible with current hardware.

- Home

- Source & Line

- Digital Source

- Interfacing Amanero to HW balanced PCM56