A while back while I cut and pasted from the 'main' F5 thread a post from NP regarding using dual (paralleled) Toshibas:snip....So far my changes are: 19V rails rather than the stock 24V, Dual output Toshiba FETs with .27 ohm Source Rs. in the output. ....snip

(about the Toshiba 2SJ201 and 2SK1530) NP 6408:

"Judging by the curves on those parts, when paralleling them

you can raise the Source resistor to 1 ohm and get greater

thermal stability yet."

But here you are suggesting 0R27 as output source Rs (R11, R12, R111, R112)? How is this value determined? Stock F5 has R11 and R12 as 0R47....

'Hi flg

Could you summarise where your design is at - Transformer VA and V, Power Supply, Heat sinks.

I assume you are still going with 2 pais of Toshiba 2sk1530/2sJ201.

I am considering 7 pairs of 2sk2013/2sj313 as another alternative to my 3xIRFP240/9240 version

7 prs ,

...But here you are suggesting 0R27 as output source Rs (R11, R12, R111, R112)? How is this value determined? Stock F5 has R11 and R12 as 0R47....

Some of what I am doing will lower the gain in the output and even the input stages. Driving 2 ohm loads causes a loss of gain by a factor of 4 over an 8 ohm load. Lower Rs will give me approximately 20-25% more gain than using the .47 ohm Rs. They would not be as much of an aid to thermal stabalization at this lower value. But, I would be recouping some of the gain losses.

'

7 prs ,I'm all ears ................ tell me more

7 pairs each biased at 286mA for a total of 2A using 24V rails or 7 pairs each biased at 186mA for a total of 1.3A with 40V rails.

What ever sounds best.

Paralleling common source configurations, as in F5, has never worked well for me. I tried some multiple smaller FETs on the PLH output and it sounded sheeety. It's the miller capacitance multipied by the gain that's gonna kill ya! That is not what happens in a multiple source follower output stage!

Having said that, I did a little Pspice over the weekend and found the Low Z F5 version (19V rails and Dual Outputs) to be producing an OLG of about 233 vs. 333 for the std. F5. Source Rs of about 0R22 would raise the gain to about 255.

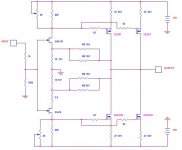

I'm going to procede with the build as in the schematic above.

I'm going to procede with the build as in the schematic above.

Paralleling common source configurations, as in F5, has never worked well for me. I tried some multiple smaller FETs on the PLH output and it sounded sheeety. It's the miller capacitance multipied by the gain that's gonna kill ya! That is not what happens in a multiple source follower output stage!

The capacitance is actually quite low (Ciss <1400pF). It is at least definitely less than 2pairs of Toshiba 2sk1530/2sj201

Isn't it transconductance/Ciss that is important?

The higher the ratio of transconductance to Ciss the better?

Could you explain this a bit more?

Nelson obviously doesn't have problems with it. The Aleph series is a testament to that.

Last edited:

Paralleling common source configurations, as in F5, has never worked well for me. I tried some multiple smaller FETs on the PLH output and it sounded sheeety. It's the miller capacitance multipied by the gain that's gonna kill ya! That is not what happens in a multiple source follower output stage!

Learning more about the subject will do you good:

http://www.diyaudio.com/forums/pass-labs/129040-mosfet-output-stage-capacitance.html#post1599135

The OLG is load impedance dependent.

Patrick

Yes, as stated in post #86.

The capacitance is actually quite low (Ciss <1400pF). It is at least definitely less than 2pairs of Toshiba 2sk1530/2sj201

Isn't it transconductance/Ciss that is important?

The higher the ratio of transconductance to Ciss the better?

Could you explain this a bit more?

Nelson obviously doesn't have problems with it. The Aleph series is a testament to that.

Ciss was not the capacitance I was refering too. And, I thought you were talking 7 pairs.

Learning more about the subject will do you good:

http://www.diyaudio.com/forums/pass-labs/129040-mosfet-output-stage-capacitance.html#post1599135

I suppose it would. However I beleive your link only refers to driving a complimentary pair of source followers? The F5 is common source?

Ciss was not the capacitance I was refering too. And, I thought you were talking 7 pairs.

Yes I was talking 7 pairs. 7x150pF (roughly 1050pF depending on Vds) is less than 1400pF (which is below 2x2sk1530).

At 286mA each (for total of 2A) transconductance is around 0.7S. 7 x 0.7 = 4.9S

For comparison 2 x 2sk1530 biased at 1A each (2A total) gives a total transconductance of about 4S, with Ciss of 2x950pF = 1900pF

I am still not sure what you are talking about regarding miller capacitance issues. If you can explain that It would be appreciated.

Attachments

Last edited:

- Status

- This old topic is closed. If you want to reopen this topic, contact a moderator using the "Report Post" button.

- Home

- Amplifiers

- Pass Labs

- F5 For Low Z Loads ?