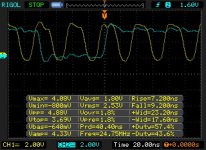

I just purchased the offical XMOS audio 2.0 evm and using an oscilloscope to view the i2s mck sck etc. But I found that there is a serious delay between each signal rise edge

and using an oscilloscope to view the i2s mck sck etc. But I found that there is a serious delay between each signal rise edge replacing the default crystal circuit with a high quality oscillator without help.

replacing the default crystal circuit with a high quality oscillator without help.

There is overhead to process the USB signal, but the MCK is directly route from the crystal/oscillator, result: they are not in syn anymore. I don't think there is a DAC can process this kind of out of phase I2S signal good.

The MCLK must syn with the I2S data before processing with other DAC.

Any xmos design already exist with syn'ed i2s, I am a lazy guy

I am also surprise to found out that even the decade old PCM2707 I2S out wave form from CRO is far better than then the XMOS I2S, is the asyn 2.0 only a marketing strategies

There is overhead to process the USB signal, but the MCK is directly route from the crystal/oscillator, result: they are not in syn anymore. I don't think there is a DAC can process this kind of out of phase I2S signal good.

The MCLK must syn with the I2S data before processing with other DAC.

Any xmos design already exist with syn'ed i2s, I am a lazy guy

I am also surprise to found out that even the decade old PCM2707 I2S out wave form from CRO is far better than then the XMOS I2S, is the asyn 2.0 only a marketing strategies

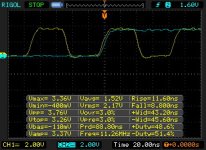

I just try another USB 2.0 audio chip CM6631 to I2S interface,

same delay problem

But I am surprise to see that the old PCM2707 has the best sync signal

Usually you want the data stable for a certain period (setup time) before the clock or there is a race condition inside the chip. Having the data change with the clock leaves a serious question of whether the clock caught the correct edge of the data. Changing the data on the "back side" of the clock is considered the best practice.

Have you checked to see if the bit clock, LR clock and data streams are synchronous or not? Lots of modern DACs only require that the master clock be at an exact multiple of the sampling frequency, not that the clocks are synchronous too.

I mean obviously the bit clock, LR clock and data streams have to be synchronous as this is how the raw data is clocked into the DAC chip. I am assuming that those clock lines are synchronous.

I mean obviously the bit clock, LR clock and data streams have to be synchronous as this is how the raw data is clocked into the DAC chip. I am assuming that those clock lines are synchronous.

Hi wizard1238

Just have seen Your posts.

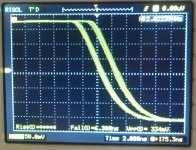

Could You check BitClock on Your XMOS board, with the same scope set-up as mine.

Just set trigger at rising edge and move waveform on the screen to see the falling edge of BitClock.

Please have a look at my screens.

Rosendorfer

Just have seen Your posts.

Could You check BitClock on Your XMOS board, with the same scope set-up as mine.

Just set trigger at rising edge and move waveform on the screen to see the falling edge of BitClock.

Please have a look at my screens.

Rosendorfer

Attachments

Hi wizard1238

Just have seen Your posts.

Could You check BitClock on Your XMOS board, with the same scope set-up as mine.

Just set trigger at rising edge and move waveform on the screen to see the falling edge of BitClock.

Please have a look at my screens.

Rosendorfer

bitclock and data signal is ok

but mclk and data is not sync within a reasonable range, according to the pcm1794 datasheet, mclk is used by the DAC for it's internal digital interpolation filter. (other dac chip should be the same...)

The problem become... Does the internal digital interpolation filter need a mclk and data sync at the rising edge for better sound

Does the internal digital interpolation filter need a mclk and data sync at the rising edge for better sound

From a technical point of view I doubt it. I mean we may have endless debates on subjective vs objective based design/balancing/tweaking, but one things for sure, most IC designers can never be accused of lacking in the latter. If having the master clock synchronous to the others would help on a technical level in terms of improving any of the standard performance parameters then it would be mentioned.

I mean it's obvious that the other three lines need to be synchronous as they are responsible for the data transfer and it's also obvious that any timing errors on said lines will affect how the data is clocked into the device, but in data terms the master clock has no direct link to the data. I mean DSPs and some older DACs don't even need the master clock, so from a data manipulation point of view it is completely unnecessary.

bitclock and data signal is okthey sync within a reasonable range,

Could You check JUST!! BitClock on Your XMOS board, with the same scope set-up as mine !!

And send me the screens.on PM ....Please.

Rosendorfer

The PCM1794 does not require a specific phase relationship between the SCK (also called MCK and MCLK above). But the SCK must of course be frequency locked to the bit clock etc. of the I2S signals. Actually the data sheet specifically states: "The PCM1794A requires the synchronization of LRCK and the system clock, but does not need a specific phase relation between LRCK and the system clock."

I think this is the normal situation with converters. The MCLK does not have to be phase locked, only frequency locked.

I think this is the normal situation with converters. The MCLK does not have to be phase locked, only frequency locked.

- Status

- This old topic is closed. If you want to reopen this topic, contact a moderator using the "Report Post" button.

- Home

- Source & Line

- Digital Source

- XMOS BAD sound?